实验一 简单组合逻辑电路的设计

一实验要求

1. 用verilog HDL语言描写出简单的一位数据比较器及其测试程序;

2. 用测试程序对比较器进行波形仿真测试;画出仿真波形;

3. 总结实验步骤和实验结果。

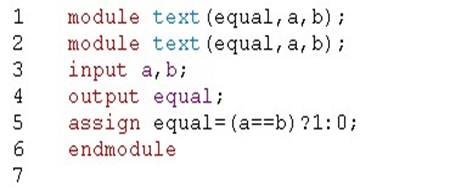

二 实验原理与内容

4. 这是一个可综合的数据比较器,很容易看出它的功能是比较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。在Verilog HDL中,描述组合逻辑时常使用assign结构。注意equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

5. 模块源代码

测试模块:

![Y_]883GK0(9{6E75(]PGDIX](https://upload2.fanwen118.com/wk001/4084888/4084888_img_002.jpg)

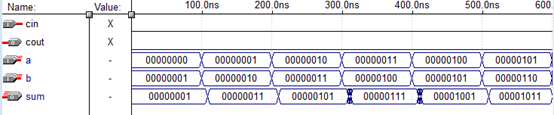

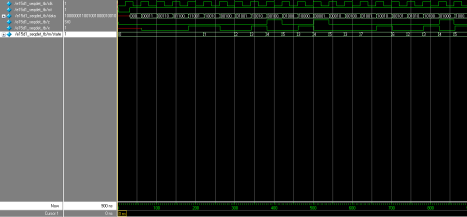

6. 波形图:

四 结实验步骤和实验结果

由图可看出,每当输入的电位值不同时输出为0,这与实验要求一致,相同时输出为1,故此程序是可行的。

实验三 在verilog HDL中使用函数

一实验要求

1. 掌握函数在模块中的使用

2. 用测试程序进行波形仿真测试;画出仿真波形

3. 总结实验步骤和实验结果

二 实验原理与内容

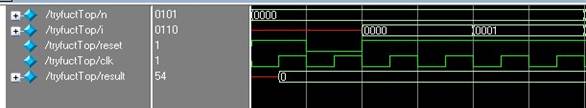

与一般的程序设计语言一样;verilog HDL也可以使用函数已是应对不同变量采取同一运算的操作。verilog HDL函数在综合时被理解成具有独立运算功能的电路,每调用一次函数相当于改变这部分电路的输入以得到相应的计算结果。

模块源代码:

module ex3(clk,n,result,reset);

output[31:0] result;

input[3:0] n;

input reset,clk;

reg[31:0] result;

always @(posedge clk)

begin

if(!reset)result <= 0;

else

begin

result <= n*factorial(n)/((n*2)+1);

end

end

function[31:0] factorial;

input[3:0] operand;

reg[3:0] index;

begin

factorial = operand ? 1:0;

for(index = 2;index <= operand;index = index+1)

factorial = index*factorial;

end

endfunction

endmodule

`timescale 1ns/100ps

`define clk_cycle 50

module ex3_t();

reg[3:0] n,i;

reg reset,clk;

wire[31:0] result;

initial

begin

n=0;

reset=1;

clk=0;

#100 reset=0;

#100 reset = 1;

for(i=0;i <= 15;i=i+1)

begin

#200 n=i;

end

#100 $stop;

end

always #`clk_cycle clk =~ clk;

ex3 ex30(.clk(clk),.n(n),.result(result),.reset(reset));

always @(negedge clk)

$display("at n=%d,result=%d",n,result);

endmodule

波形图 :

实验四 在verilog HDL中使用任务

一实验要求

1. 掌握任务在结构化verilog HDL设计中的应用

2. 用测试程序进行波形仿真测试;画出仿真波形

3. 总结实验步骤和实验结果

二 实验原理与内容

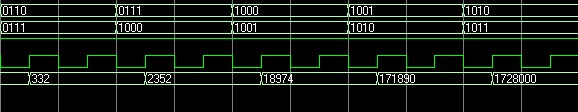

仅有函数并不能满足verilog HDL中的运算需求。当我们希望能够将一些信号进行运算并输出多个结果时,采用函数结构就显得非常不方便,而任务结构在这方面的优势十分的突出。任务本身并不返回计算值,但是它通过类似C语言中形参与实参的数据交换,非常快捷的实现运算结果的调用。

模块源代码:

output[3:0] ra,rb,rc,rd;

input[3:0] a,b,c,d;

reg[3:0] ra,rb,rc,rd;

reg[3:0] va,vb,vc,vd;

always @(a or b or c or d)

begin

{va,vb,vc,vd} = {a,b,c,d};

sort2(va,vc);

sort2(vb,vd);

sort2(va,vb);

sort2(vc,vd);

sort2(vb,vc);

{ra,rb,rc,rd} = {va,vb,vc,vd};

end

task sort2;

inout[3:0] x,y;

reg[3:0] tmp;

if(x>y)

begin

tmp=x;

x=y;

y=tmp;

end

endtask

endmodule

测试程序代码:

`timescale 1ns/100ps

module task_Top;

reg [3:0] a,b,c,d;

wire[3:0] ra,rb,rc,rd;

initial

begin

a=0;

b=0;

c=0;

d=0;

repeat(5)

begin

#100 a=$random;

b=$random;

c=$random;

d=$random;

end

#100 $stop;

end

sort4 sort4(.a(a),.b(b),.c(c),.d(d),.ra(ra),.rb(rb),.rc(rc),.rd(rd));

endmodule

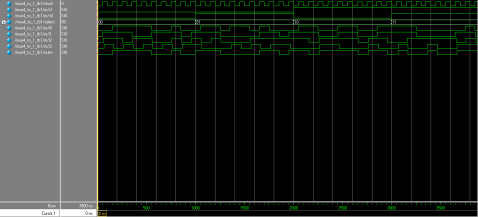

波形图 :

波形图 :

四 结实验步骤和实验结果

a、b、c、d赋以0101,0100,0011,0010,显示结果应为:ra=0010,rb=0011,rc=0100,rd=0101,结果与理论数据相符。

实验六 8位全加器的设计

一实验要求

1. GW48实验箱

2. 用原理图输入方式设计8位全加器,并进行编译、仿真、下载;

3. 总结实验步骤和实验结果

模块源代码

二 实验原理与内容

1. 加法器是数学系统中的基本逻辑器件,加法器和硬件乘法器都可由加法起来构成。多位加法器的构成有两种:并行进位和窜行进位。

2. 万成位全加器ADDER4B的设计,并将此全加器电路设计成一个硬件符号入库。建立一个更高的原理图设计层,可命名为ADDER8B.

模块源代码:

1、 了解一位全加器的设计与编程,设计一个四位二进制的全加器,其编程如下:

module HA(A,B,CIN,S,COUT);

output[3:0]S;

output COUT;

input[3:0] A,B;

input CIN;

assign{COUT,S}=A+B+CIN;

endmodule

2、 用两个四位二进制的全加器级联构成八位二进制的全加器,其编程如下:

module Adder8Bit(a,b,cin,sum,cout);

input[7:0]a,b;

input cin;

output[7:0]sum;

output cout;

wire c;

HA p0(a[3:0],b[3:0],cin,sum[3:0],c);

HA p1(a[7:4],b[7:4],c,sum[7:4],cout);

endmodule

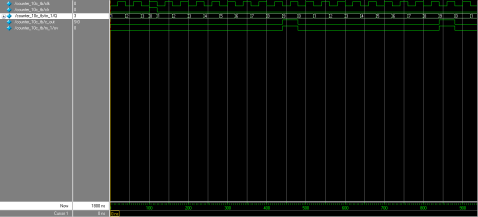

波形图:

图1

图2

四 结实验步骤和实验结果

利用4位全加器级联成8位全加器,由图1可明显的看出此程序实现了全加器的功能;由图2又可以知道此程序是8位相加的,故它实现了8位全加器的功能。

第二篇:Verilog HDL 实验报告

Verilog实验报告

班级:

学号:

姓名:

- 1 -

实验1 :用 Verilog HDL 程序实现直通线

1 实验要求:

(1) 编写一位直通线的 Veirlog HDL 程序.

(2) 编写配套的测试基准.

(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.

(4) 建议用模式 5

2 试验程序:

module wl(in,out);

input in;

output out;

wire out;

assign out=in;

endmodule

3 测试基准:

`include “wl.v”

module wl_tb;

reg in_tb;

wire out_tb;

initial

begin

in_tb =0;

#100 in_tb =1;

#130 in_tb =0;

end

endmodule

4 仿真图形:

- 2 -

实验2 :用 Verilog HDL 程序实现一位四选一多路选择器

1实验要求:

(1) 编写一位四选一多路选择器的 Veirlog HDL 程序.

(2) 编写配套的测试基准.

(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.

(4) 建议用模式 5

2 试验程序:

module mux4_to_1 (out,i0,i1,i2,i3,s1,s0);

output out;

input i0,i1,i2,i3;

input s1, s0;

reg out;

always @ (s1 or s0 or i0 or i1 or i2 or i3)

begin

case ({s1, s0})

2'b00: out=i0;

2'b01: out=i1;

2'b10: out=i2;

2'b11: out=i3;

default: out=1'bx;

endcase

end

endmodule

3 测试基准:

`include "mux4_to_1.v"

module mux4_to_1_tb1;

reg ain,bin,cin,din;

reg[1:0] select;

reg clock;

wire outw;

initial

begin

ain=0;

bin=0;

cin=0;

din=0;

select=2'b00;

clock=0;

end

always #50 clock=~clock;

always @(posedge clock)

begin

#1 ain={$random} %2;

- 3 -

#3 bin={$random} %2;

#5 cin={$random} %2;

#7 din={$random} %2;

end

always #1000 select[0]=!select[0];

always #2000 select[1]=!select[1];

mux4_to_1 m(.out(outw),.i0(ain),.i1(bin),.i2(cin),.i3(din),.s1(select[1]),.s0(select[0]));

endmodule

4 仿真图形:

实验3:用 Verilog HDL 程序实现十进制计数器

1实验要求:

(1) 编写十进制计数器的 Veirlog HDL 程序. 有清零端与进位端, 进位端出在输出为 9 时为高电平.

(2) 编写配套的测试基准.

(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.

(4) 自行选择合适的模式

2 实验程序:

module counter_10c (Q, clock, clear, ov);

output [3:0] Q;

output ov;

input clock, clear;

reg [3:0] Q;

reg ov;

initial Q=4'b0000;

always @ (posedge clear or negedge clock)

begin

if (clear)

Q<=4'b0;

else if (Q==8)

begin

- 4 -

Q<=Q+1;

ov<=1'b1;

end

else if (Q==9)

begin

Q<=4'b0000;

ov<=1'b0;

end

else

begin

Q<=Q+1;

ov<=1'b0;

end

end

endmodule

3 测试基准:

`include"./counter_10c.v"

module counter_10c_tb;

wire[3:0] D_out;

reg clk,clr;

wire c_out;

reg[3:0] temp;

initial

begin

clk=0;

clr=0;

#100 clr=1;

#20 clr=0;

end

always #20 clk=~clk;

counter_10c m_1(.Q(D_out),.clear(clr),.clock(clk),.ov(c_out)); endmodule

4 仿真波形:

- 5 -

实验4 :用 Verilog HDL 程序实现序列检测器

1 实验要求:、

(1) 编写序列检测器的 Veirlog HDL 程序. 检测串行输入的数据序列中是否有目标序列 5'b10010, 检测到指定序列后, 用一个端口输出高电平表示.

(2) 编写配套的测试基准.

(3) 通过 QuartusII 编译下载到目标 FPGA器件中进行验证.

(4) 自行选择合适的模式

2试验程序:

module e15d1_seqdet( x, z, clk, rst);

input x,clk, rst;

output z;

reg [2:0] state;

wire z;

parameter IDLE = 3 'd0,

A = 3'd1,

B = 3'd2,

C = 3'd3,

D = 3'd4,

E = 3'd5,

F = 3'd6,

G = 3'd7;

assign z =(state==D && x==0)?1:0;

always @(posedge clk or negedge rst)

if(!rst)

begin

state<=IDLE;

end

else

casex(state)

- 6 -

IDLE: if(x==1)

state<=A;

else state<=IDLE; A: if (x==0)

state<=B;

else state<=A;

B: if (x==0)

state<=C;

else state<=F;

C: if(x==1)

state<=D;

else state<=G;

D: if(x==0) state<=E;

else state<=A;

E: if(x==0)

state<=C;

else state<=A;

F: if(x==1)

state<=A;

else state<=B;

G: if(x==1)

state<=F;

else state <=G;

default: state<=IDLE;

endcase

endmodule

3 测试基准:

`include"e15d1_seqdet.v"

`timescale 1ns/1ns

`define halfperiod 20

module e15d1_seqdet_tb;

reg clk, rst;

reg [23:0] data;

wire z;

reg x;

initial

begin

clk =0;

rst =1;

#2 rst =0;

#30 rst =1;

data= 20 'b1100_1001_0000_1001_0100; - 7 -

#(`halfperiod*1000) $stop;

end

always #(`halfperiod) clk=~clk;

always @ (posedge clk)

begin

#2 data={data[22:0],data[23]};

x=data[23];

end

e15d1_seqdet m(.x(x),.z(z),.clk(clk),.rst(rst));

endmodule

4 仿真波形:

- 8 -