深 圳 大 学 实 验 报 告

课程名称: Verilog使用及其应用

实验名称: 频率可变的任意波形发生器

学院: 电子科学与技术学院

专业:电子科学与技术班级: 2

组号: 指导教师:##

报告人: ## 学号: ##

实验地点 科技楼B115

一、实验目的

应用Verilog进行编写四种波形发生的程序,并结合DE2板与DVCC实验板上的D/A转换器在示波器显示出波形。初步了解Verilog的编程及DE2板的应用,加强对其的实际应用操作能力。

二、实验原理

实验程序分为三部分:

第一、 通过计数器实现内置信号分频,并通过外置开关调节频率来控制输出波形的频率。

第二、 设定ROM中的数值,将波形数据存储到ROM中。

第三、 设定波形选择开关。

总体设计方案及其原理说明:

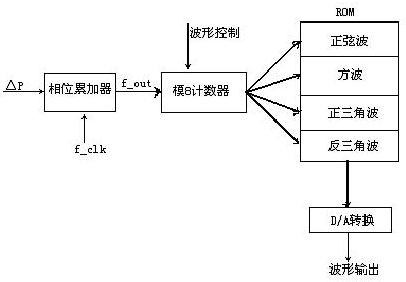

图 1-1 系统总体设计方案

DDS是一种把数字信号通过数/模转换器转换成模拟信号的合成技术。它由相位累加器、相幅转换函数表、D/A转换器以及内部时序控制产生器等电路组成。

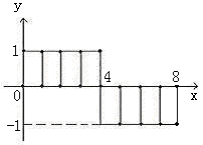

参考频率f_clk为整个合成器的工作频率,输入的频率字保存在频率寄存器中,经N位相位累加器,累加一次,相位步进增加,经过内部ROM波形表得到相应的幅度值,经过D/A转换和低通滤波器得到合成的波形。p为频率字,即相位增量;参考频率为f_clk;相位累加器的长度为N位,输出频率f_out为:

f_out——输出信号的频率; N————相位累加器的位数;

p———频率控制字(步长); f_clk——基准时钟频率。

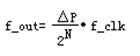

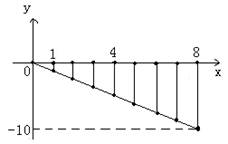

图1-2 四种波形单周期的取样示意图

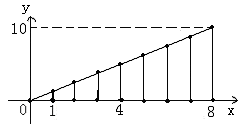

段地址 基地址 D7 D6 D5 D4 D3 D2 D1 D0

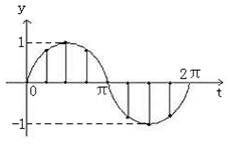

图1-3 函数查找表的设计

三、实验内容

程序编码:

module dds(f_clk,p,choose,data);//端口设定

input [5:0] p; //频率控制字

input[1:0] choose; //波形选择

input f_clk; //内置晶振

output [7:0] data;

wire [7:0]data;

reg [5:0] addr,address;

reg [5:0] i;

reg f_out;

initial

begin

i<=0;

addr<=0;

f_out<=0;

end

always @(posedge f_clk) //利用计数器实现任意分频

begin

if(i==p) //设定频率控制字p

begin

i=0;

f_out=~f_out;

end

else

i=i+1;

end

function [7:0] romout; //ROM的设定

input[5:0] address;

case(address) //各波形初值的预装入

0 : romout = 10; //正弦波初值

1 : romout = 17;

2 : romout = 15;

3 : romout = 17;

4 : romout = 10;

5 : romout = 3;

6 : romout = 5;

7 : romout = 3;

8 : romout = 3; //方波初值

9 : romout = 3;

10: romout = 3;

11: romout = 3;

12: romout = 1;

13: romout = 1;

14: romout = 1;

15: romout = 1;

16 : romout = 0; //正三角波初值

17 : romout = 5;

18 : romout = 10;

19 : romout = 15;

20 : romout = 20;

21 : romout = 25;

22 : romout = 30;

23 : romout = 35;

24 : romout = 35; //反三角波初值

25 : romout = 30;

26 : romout = 25;

27 : romout = 20;

28 : romout = 15;

29 : romout = 10;

30 : romout = 5;

31 : romout = 0;

default : romout = 10'hxx;

endcase

endfunction

always@(posedge f_out)

begin

if(addr==8) //波形数据切换

addr=0;

else

addr=addr+1;

case(choose) //波形选择开关设定

0: address=addr;

1: address=addr+8;

2: address=addr+16;

3: address=addr+24;

endcase

end

assign data = romout(address);//将ROM中对应数据传递输出端口data输出

endmodule

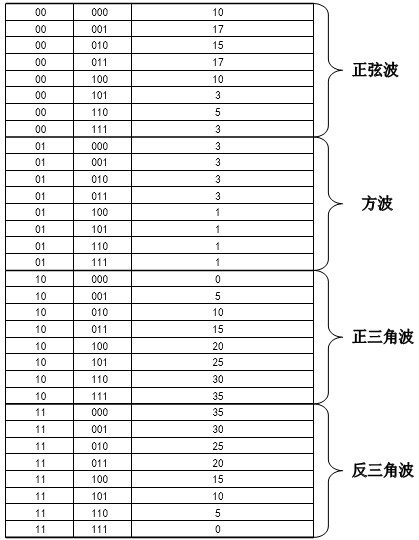

四、实验截图

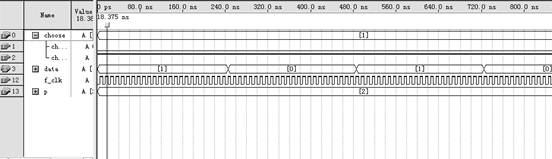

1.正弦波示意图:(choose=0时的波形数值)

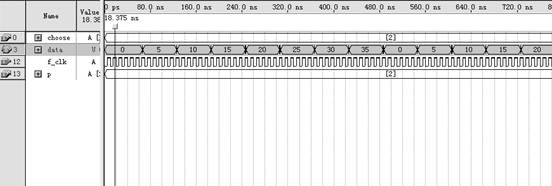

2.方波示意图:(choose=1时的波形数值)

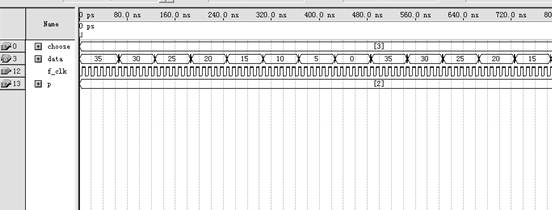

3.正三角波示意图:(choose=2时的波形数值)

4.反三角波示意图:(choose=3时的波形数值)

五、实验总结

通过这次期末实验,更进一步认识了Verilog语言的使用,详细了解了整个设计制作和仿真流程,独立思考并通过一步步的调试,逐步摸索和进一步优化程序最终完成实验,锻炼了逻辑思维能力。实验综合性较强,在实验中涉及了本学期多个知识点: ①always语句;②initial语句;③if—else语句;④case语句;⑤传递函数assign;⑥function说明语句。

在测试和调整程序时发现一些容易犯错的问题:

第一、 用case语句取代了定义ROM造成了数据开始并没有固化在ROM中而是从程序中写入再读出。(解决办法:用function语句对ROM进行定义并装初值)

第二、 应该注意传递函数中的输出端口应该是wire型的,如果定义为reg将会出错。

第三、 开始时波形数据按照图放入初值时,有负数、小数等,当装入负数小数后在仿真中无法正确显示数字。(解决办法:将波形平移扩大将小数和负数换算成整数装入即可显示波形数据)

第四、 关键的问题是怎样实现寻址的操作,首先是定义一个从0—7的循环加法计数器作为段内基地址寻址,然后通过case语句choose波形选择相应波段的段地址。

个人觉得这样的实验比较贴近学习和工作,通过自己动手更加能够充分掌握所学知识点,将书本和实际结合起来,希望以后可以开展更多这样的实验。

第二篇:波形发生器实验报告

电子信息工程系实验报告

课程名称:智能仪器

课程名称:智能仪器

实验项目名称:实验三 波形发生器实验 实验时间:20##/06/08

实验项目名称:实验三 波形发生器实验 实验时间:20##/06/08

班级:电信092 姓名:陈毜 学号:910706220

一、实验目的:

掌握波形发生器的硬件电路实现方法,通过labview 软件的使用,掌握虚拟仪器系统的软件实现方法。

二、实验环境:

LABVIEW软件、实验箱、labjack

三、实验原理:

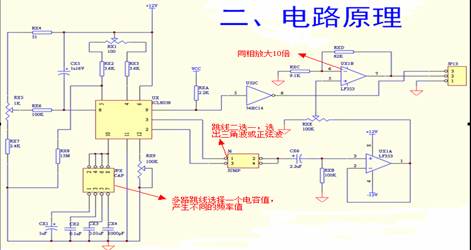

实验电路原理图如下所示。

图1 电路原理图

频率的计算如下所示:

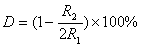

对于三角波,其输出幅度与振荡频率为: ,

,

这也是矩形波和正弦波的频率,其中矩形波的占空比为:

当 时,输出的为对称波,频率可化简为:

时,输出的为对称波,频率可化简为:

四、实 验 步 骤:

1、JP6: 跳线1短接;

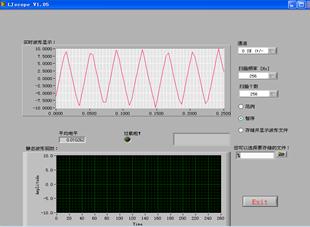

2、先把JP13的“方波”--->LABJACK 的“AI0”,运行“WAVE.VI”,观测波形如图2所示:

3、保持运行“WAVE.VI”,把JP13的“信号”--->LABJACK 的“AI0”,短接JP6的 跳线1(三角波),观测波形如图3所示:

4、保持运行“WAVE.VI”,把JP13的“信号”---> LABJACK 的“AI0”,短接JP6的 跳线2(正弦波),观测波形如图4所示

图2 方波波形图 图3 三角波波形图

图4 正弦波波形图

五、实 验 结 果 及 分 析:

六、实 验 心 得