静态存储器扩展实验报告

一、 实验目的

1. 掌握单片机系统中存储器扩展的方法;

2. 掌握单片机内部RAM和外部RAM之间数据传送的特点。

二、 软件、硬件环境要软件、硬件环境要求

1、软件环境要求

Windows XP操作系统以及Keil C51 单片机集成开发环境。

2、硬件环境要求

电脑一台,TD-51单片机系统。

三、 实验内容

编写实验程序,在单片机内部一段连续RAM 空间30H~3FH 中写入初值00H~0FH,然后将这16 个数传送到RAM 的0000H~000FH 中,最后再将外部RAM 的0000H~000FH 空间的内容传送到片内RAM 的40H~4FH 单元中。

四、  实验原理

实验原理

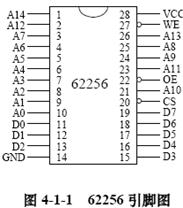

存储器是用来存储信息的部件,是计算机的重要组成部分,静态RAM 是由MOS 管组成的触发器电路,每个触发器可以存放1 位信息。只要不掉电,所储存的信息就不会丢失。因此,静态RAM工作稳定,不要外加刷新电路,使用方便。但一般SRAM 的每一个触发器是由6个晶体管组成,SRAM 芯片的集成度不会太高,目前较常用的有6116(2K×8 位),6264(8K×8 位)和62256(32K×8位)。本实验以62256 为例讲述单片机扩展静态存储器的方法。

SST89E554RC 内部有1K 字节RAM,其中768 字节(00H~2FFH)扩展RAM 要通过MOVX指令进行间接寻址。内部768 字节扩展RAM 与外部数据存储器在空间上重叠,这要通过AUXR寄存器的EXTRAM 位进行切换,AUXR 寄存器说明如下:

EXTRAM:内部/外部RAM 访问

0:使用指令MOVX @Ri/@DPTR 访问内部扩展RAM,访问范围00H~2FFH,300H 以上的空间为外部数据存储器;

1:0000H~FFFFH 为外部数据存储器。

AO:禁止/使能ALE

0:ALE 输出固定的频率;

1:ALE 仅在MOVX 或MOVC 指令期间有效。

五、 实验步骤

1. 按图连接使用电路;

2. 按实验内容编写实验程序,经编译、链接无误后启动调试;

3. 打开存储器观察窗口,在存储器#1 的Address 中输入D:0x30,在存储器#2 的Address中输入X:0x0000 来监视存储器空间;

4. 可单步运行程序,观察存储器内容的变化,或在while(1)语句行设置断点再运行程序,验证实验功能。

六、 实验程序

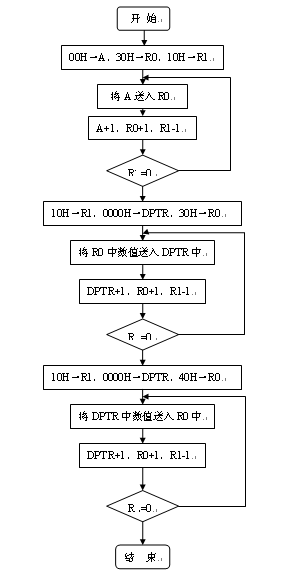

程序流程图:

程序清单:

ORG 0000H

LJMP MAIN

ORG 0100H

MAIN:

MOV R1,#10H ;循环次数=16

MOV A,#00H ;给A赋初值值为0

MOV R0,#30H

LOOP:

MOV @R0,A ;将00H~0FH写入内部RAM30H~3FH

INC A

INC R0

DJNZ R1,LOOP ;R1不为0则循环,否则结束

MOV R1,#10H ;循环次数=16

MOV R0,#30H

MOV DPTR,#0000H

LOOP1: ;写入外部RAM0000H~000FH中

MOV A,@R0 ;30H的内容给累加器A

MOVX @DPTR,A ; A的内容给0000H

INC DPTR

INC R0

DJNZ R1,LOOP1 ;R1不为0则循环,否则结束

MOV R1,#10H ;循环次数=16

MOV R0,#40H

MOV DPTR,#0000H

LOOP2: ;写入内部RAM40H~4FH中

MOVX A,@DPTR ;0000H的内容给A

MOV @R0,A ;A的内容给40H

INC DPTR ;修改A里面的内容

INC R0

DJNZ R1,LOOP2 ;R1不为0则循环,否则结束

SJMP $

END

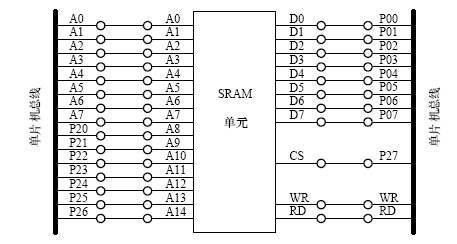

硬件接线图:

扩展存储器实验线路图

注:连接实验线路时,若使用PITE 接口实验箱,应将BHE#和BLE#信号接GND;若使用PIT+实验箱,需将BE3~BE0 接GND。

七、 实验结果

在存储器窗口可以看到30H~3FH,0000H~000FH,40H~4FH里面的内容都为00H~0FH。实现了单片机内部RAM和外部RAM之间的数据的传送。

注意:在调试运行程序,察看结果时,存储器窗口可能不会出现我们想要的结果,只能单步运行或设置一断点时才可以看到正确的结果。

八、 实验总结

本次实验是实现单片机内部RAM和外部RAM之间数据的传送,这就要求我们知道他们各自传送的特点。内外之间不可以直接传送,要通过累加器A来实现。由于此次实验是在硬件环境下完成的,所以需要我们掌握单片机存储器扩展的方法。

第二篇:存储器设计实验报告

实验一:存储器设计

一、实验目的:

1、掌握随机存储器RAM的工作特性及使用方法;

2、掌握半导体存储器存储和读写数据的工作原理。

二、实验电路及其原理:

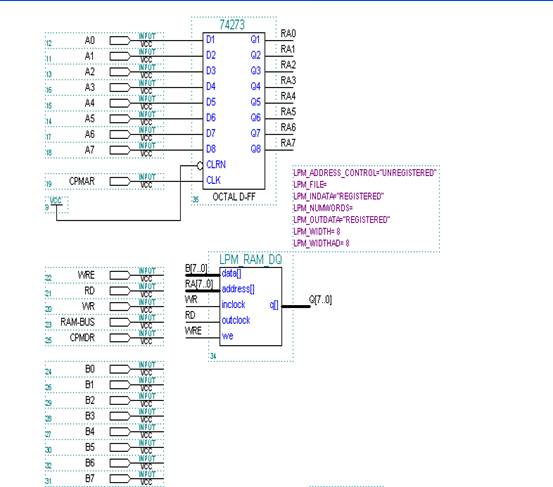

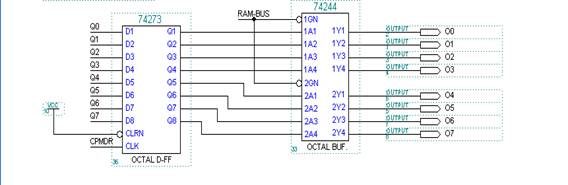

1.实验电路图

2、设计原理

存储器就是选择RAM地址,并对其操作存入数据,在需要时对其读取,并把数据输出到数据总线。实验思路大致为:

①第一个74273用来接收数据存放在RAM里的地址,即A0…7。当CPMAR有效时数据进入芯片。

②当WE=1,RD=0时,RAM进行写操作,接收存储在74273里的数传到地址端口,同时接收从B0…7输入的数据传到数据端口,把数据写到相应RAM里。

③当WE=0。RD=1时,RAM进行读操作,把对应存储单元的数据传到第二个74273,通过74273传到74244芯片输出。

三、实验步骤

1、根据实验原理在maxplus下连接电路图,对其进行编译。

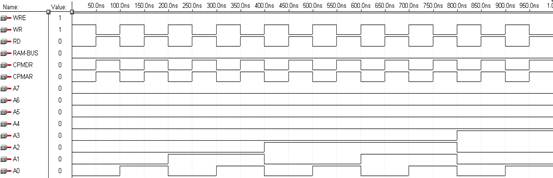

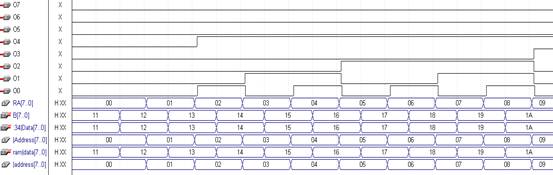

2、根据实验原理设计各个输入端的波形图,对其进行仿真模拟获得输出数据,仿真波形如下图。

四、仿真图

说明:RAM在WRE=1时才工作,为方便起见WRE置为1;74244在RAM_BUS=0时工作,为方便起见RAM_BUS置为0。因CPMOR为一个周期变换一次,为了不浪费存储空间,A0为两倍的周期变换,A1为四周期变换,以此类推。存储的数据从11H起依次增加。

五、实验总结

通过本次实验熟练掌握MAX+PLUS软件,并运用该软件设计存储器,了解了存储器的结构设计和工作原理,并在理解的基础上自己设计了一个简单的存储器。在之后的波形仿真图模拟时,发现自己不能很好控制各个芯片的片选信号,不知道如何使各个芯片在合适的时间工作,在经过仔细分析后,设置了上图的波形图,保证每个存储单元都可以存到数,没有刚开始的浪费现象,数据在各个数据线之间的传输也正常,存储器的数据输出为两个周期输出一次(这是因为WR、RD为一个周期变换一次,在两个周期后才会读有效)。

通过此次实验对MAXPLUS有了初步了解,同时也对存储器的结构有了一定的了解,初步掌握了一些设置波形的技巧。