实 验 报 告

课程名称 EDA技术与VHDL设计

实验项目 Quartus II 入门

实验仪器 计算机、QuartusII

系 别 信息与通信工程学院

专 业 电子信息工程

班级/学号

学生姓名

实验日期 2014.4.22

成 绩

指导教师

实验一 Quartus II入门

一、实验目的

1. 掌握QUARTUS II工具的基本使用方法;

2. 掌握FPGA基本开发流程和DE2开发板的使用方法;

二、实验内容

运用QUARTUS II 开发工具编写简单LED和数码管控制电路并下载到DE2 实验开发板。

三、实验环境

1.软件工具:QUARTUS II 软件;开发语言:VHDL;

2.硬件平台:DE2实验开发板。

四、源程序:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY fuqi IS

PORT(SW :IN STD_LOGIC_VECTOR(0 TO 17);

HEX0 :OUT STD_LOGIC_VECTOR(0 TO 6);

LEDR :OUT STD_LOGIC_VECTOR(0 TO 17));

END fuqi;

ARCHITECTURE Behavior OF fuqi IS

SIGNAL temp :STD_LOGIC_VECTOR(0 TO 3);

BEGIN

LEDR<=SW;

temp(3)<=SW(0);

temp(2)<=SW(1);

temp(1)<=SW(2);

temp(0)<=SW(3);

PROCESS(temp)

BEGIN

CASE temp IS

WHEN "0000"=>HEX0<="0000001";

WHEN "0001"=>HEX0<="1001111";

WHEN "0010"=>HEX0<="0010010";

WHEN "0011"=>HEX0<="0000110";

WHEN "0100"=>HEX0<="1001100";

WHEN "0101"=>HEX0<="0100100";

WHEN "0110"=>HEX0<="0100000";

WHEN "0111"=>HEX0<="0001111";

WHEN "1000"=>HEX0<="0000000";

WHEN "1001"=>HEX0<="0000100";

WHEN OTHERS=>HEX0<="1001000";

END CASE;

END PROCESS;

END Behavior;

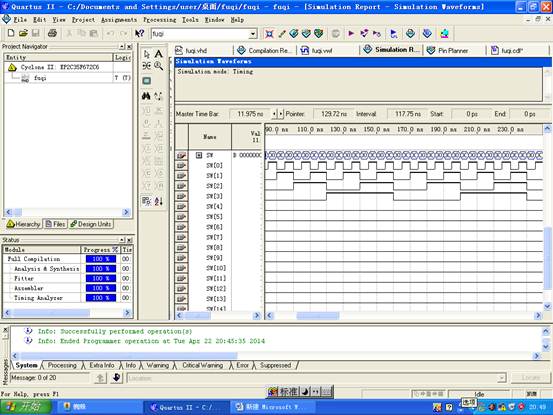

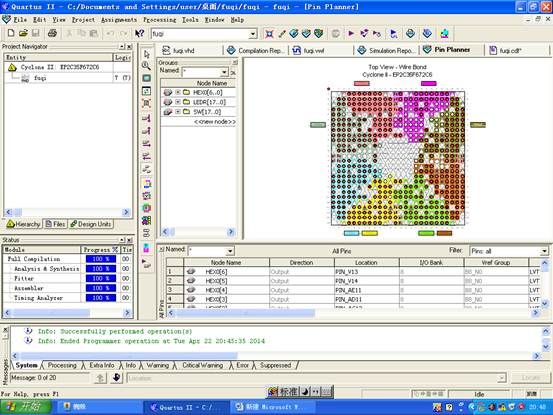

五、仿真结果:

六、实验总结:

第一次实验比较简单。通过这次实验,我对这门课程有了初步的了解,知道了QUARTUS 是FPGA的基本工具,掌握QUARTUS II工具的基本使用方法,并能够简单地操作。在做实验的过程中也遇到一些问题,但在同学的帮助下,最终运用QUARTUS II 开发工具编写简单LED和数码管控制电路并下载到DE2 实验开发板。

第二篇:FPGA实验报告

FPGA/CPLD实验报告(一)

学院:信息科学与工程学院 专 业:通信工程09-2

学号:3099990662 姓名:吴声泽 同组人:

实验:一位全加器的VHDL文本输入设计 日 期: 20##、4、14

一、实验目的:

通过实验进一步了解、熟悉和掌握FPGA开发软件的使用和VHDL语言的学习和使用,学习一位全加器的设计、多层设计方法的使用,以及GK48-PK2试验箱的使用和调试。

二、实验硬件要求:

GK48-PK2试验箱、电脑计算机

三、实验内容:

1、电路功能分析:

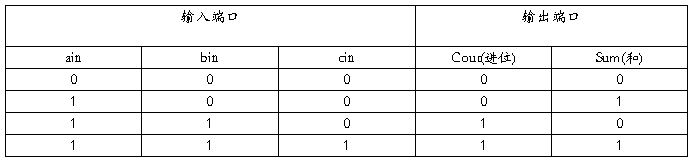

本实验的真值表如下(部分):

2、电路图或VHDL实体图:(这个是什么!?是那个模块符号图吗?)

3、VHDL程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT (ain,bin,cin : IN STD_LOGIC;

cout,sum : OUT STD_LOGIC );

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS

COMPONENT h_adder

PORT ( a,b : IN STD_LOGIC;

co,so : OUT STD_LOGIC);

END COMPONENT ;

COMPONENT or2a

PORT (a,b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d,e,f: STD_LOGIC;

BEGIN

u1 : h_adder PORT MAP(a=>ain,b=>bin,co=>d,so=>e);

u2 : h_adder PORT MAP(a=>e,b=>cin,co=>f,so=>sum);

u3 : or2a PORT MAP(a=>d,b=>f,c=>cout);

END fd1;

4、仿真波形图和波形解释:

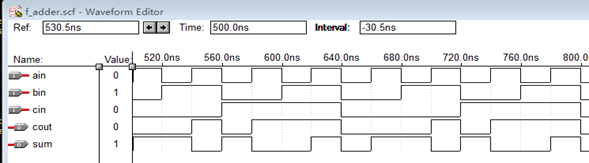

(1)、仿真波形图如下:

(2)、波形解释:如真值表与波形图所示,ain、bin、cin都是输入端,cout是高位进位计数端,sum是全加和。三个输入端有一个为1时,和sum值为1,进位cout值为0;当三个输入端有两个为1时,和sum值为0,进位cout值为1;当三个输入端都为1是,sum和cout的值均为1。

5、对应硬件选择和管脚分配关系:

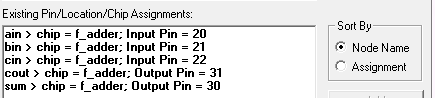

在对应硬件芯片选择时,我们选择ACEX1K系列的EP1K30TC144-3芯片。并选择试验电路结构图(6)来进行试验,用LED等D1、D2分别表示输出端sum和cout,它们对应的管脚是30、31;分别用键3、4、5作为输入端ain、bin、cin。它们的管脚分配分别是20、21、22。管脚分配如下图:

6、试验结果说明:

将程序下载到试验箱之后,依照摁下键3、4、5,LED灯出现了对应的变化,如:摁下三个键的其中一个,只有代表sum的D1亮;摁下其中两个则只有代表cout的D2亮,如果三个都摁下了,则D1、D2都亮;如果把输入键都摁灭,这D1、D2都不亮。实验结果表明:我们的实验结果成功,虽然我们还是第一次真是接触正式的实验,可是在老师的指导下并经过我们的一番学习和摸索,我们成功把实验完成了。

FPGA/CPLD实验报告(一)

学院:信息科学与工程学院 专 业:通信工程09-2

学号:3090731209 姓名:覃俊钦 同组人:张达强

实验: 2 选1多路选择器VHDL设计 日 期: 20##、4、14

一、实验目的:

通过实验进一步了解、熟悉和掌握FPGA开发软件的使用和加强VHDL语言的学习和使用,学习2选1多路选择器的设计以及掌握并加强GK48-PK2试验箱的使用和调试。

二、实验硬件要求:

GK48-PK2试验箱、电脑计算机

三、实验内容:

1、电路功能分析:

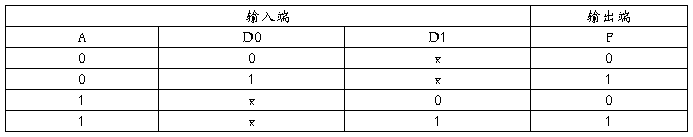

本实验的真值表如下:

2、VHDL程序如下:

library ieee;

use ieee.std_logic_1164.all;

entity erxuanyi is

port(a,d0,d1:in bit;

f:out bit);

end;

architecture one of erxuanyi is

begin

f<=d0 when a='0'else

d1;

end;

3、仿真波形图和波形解释:

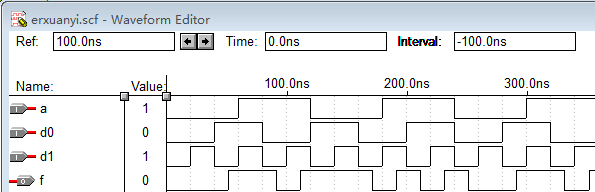

(1)、仿真波形图如下:

(2)、波形解释:

如真值表与波形图所示,A、D0、D1是信号输入端,F为信号输出端,其中A是选择输出端。当A为0时,选择D0输入端的信号在F端输出;当A为1时,选择D1输入端的信号在F端输出。

4、对应硬件选择和管分配关系:

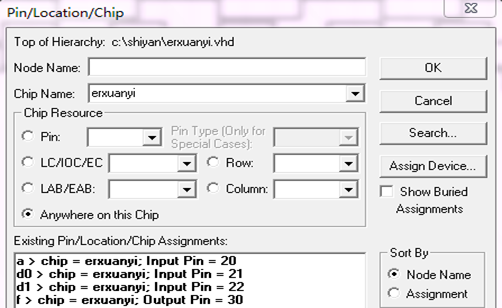

在对应硬件芯片选择时,我们选择ACEX1K系列的EP1K30TC144-3芯片。并选择实验电路结构图(6),用LED灯D1来作为F端的输出显示,键3、4、5分别作为A、D0、D1输入端,它们实际分配情况如下:

5、实验结果说明:

将程序下载到实验箱之后,摁动键3、4、5,LED灯D1出现了相应的变化 ,如:当键3没摁下去(即A=0),输出显示端LED灯由键4(即D0)来控制,它的输出和键4的输入相同;同理,当键3摁下去(即A=1),输出显示端LED灯由键5(即D1)来控制,它的输出此时与键5相同。