FPGA 实验任务书—实验一

实验心得体会:

通过这一次实验,我熟悉了DE2开发板的使用,也了解了FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

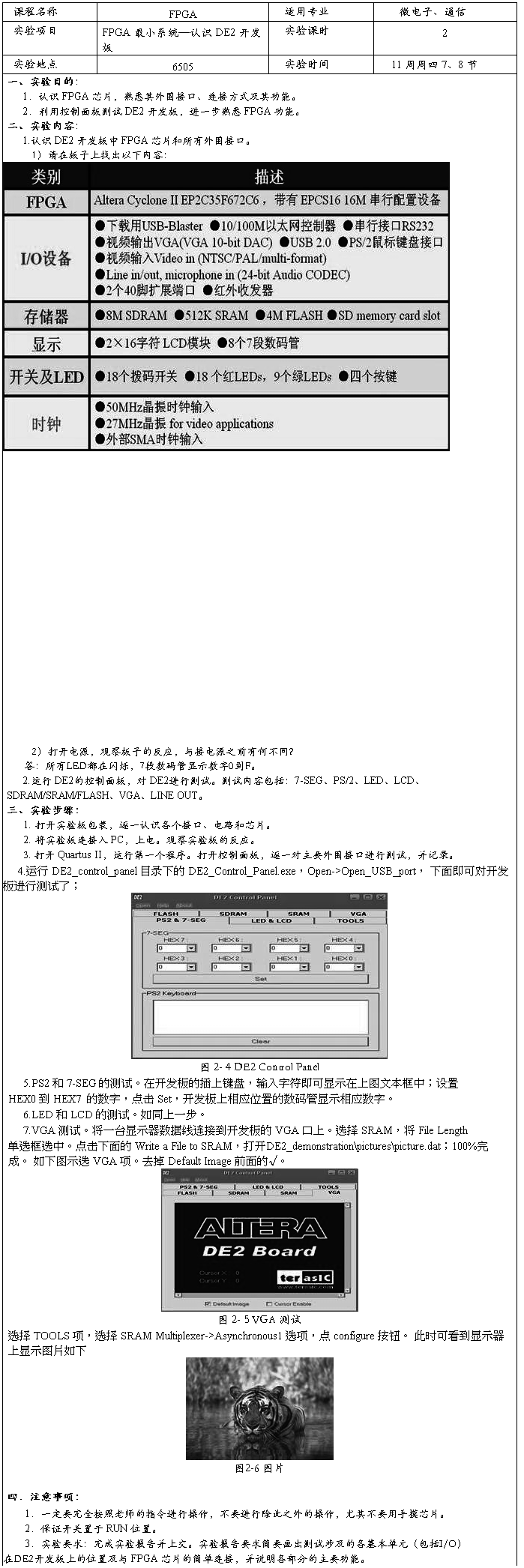

DE2是Altera公司针对大学教学及研究机构推出的FPGA多媒体开发平台。DE2 为用 户提供了丰富的外设及多媒体特性,并具有灵活而可靠的外围接口设计。DE2 能帮助使用 者迅速理解和掌握实时多媒体工业产品设计的技巧,并提供系统设计的验证。DE2 平台的 实际和制造完全按照工业产品标准进行,可靠性很高。

为了使用DE2开发板,我也学会使用QuartusII。通过读DE2开发板使用指南和QuartusII入门介绍可以获得必要的知识。Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。我也了解了Quartus II软件的一些优点:数十年来一直在缩短编译时间,编译时间平均每年减少20%。Altera高级布局布线算法支持您根据四个成本标准,迅速找到最佳结果——时序、拥塞、走线长度以及功耗,从而缩短了编译时间。

第二篇:FPGA实验报告(可上传)

FPGA实验报告

3903……

一. 对FPGA的认识

通过三次实验课的学习,我们对FPGA有了初步的认识,了解了如何在Quartus II环境下进行程序的编写、下载和运行。实验过程中虽然也遇到了不少困难,但在同学和老师的帮助下都一一解决了,总之,这几次实验,收获不少,感受颇多。

二. VHDL语言编程经验总结

实验中我们使用VHDL语文进行程序的编写,虽然VHDL语言和C语言有很多相似之处,但还是有很多地方需要我们注意。

1. 对象类型和赋值

与C语言相比,VHDL中的对象类型包含信号类型,而在实验中,信号类型的对象多次出现在实验程序中,另外,在给对象赋值时,也要注意用不对的符号,用“<=” 对信号进行赋值,而用“:=”对变量进行赋值。

同时,也要特别注意信号的方向,即input和output。

2. 常用的语句结构

我们在实验中,程序主体采用顺序结构进行编写,依次编写实体、结构体、进程等程序所必须的模块,在实验中,我们多次使用了选择结构的语句,值得注意的是,在VHDL中,case语句需要时钟触发,因而常出现在时序电路的程序设计中,对组合逻辑可以使用select语句。

三. 对实验程序的改进和探索

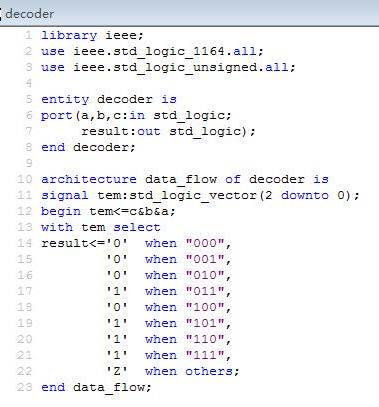

1.三人表决器

根据“指令译码器”实验,结合三人表决电路的真值表,对程序稍加改动,便可以实现三人表决器的程序设计,由于是组合逻辑,我们选取select语句结构,信号tem=a&b&c,代码如下:

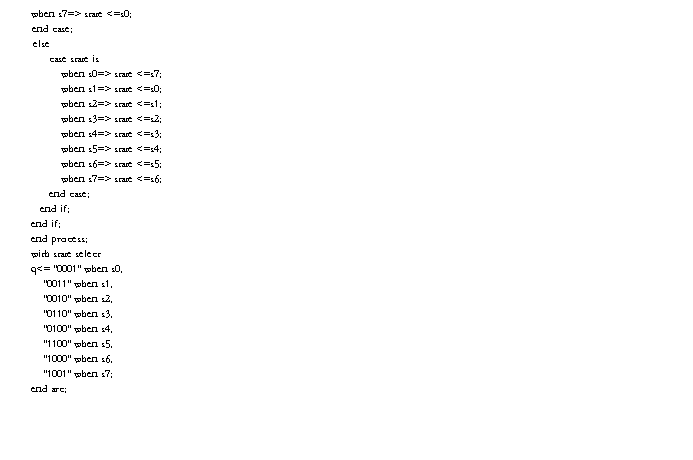

2.步进电机四线八拍运行

根据步进电机的八拍运行时序,在原有的case结构中多添加4种情况,便可以实现步进电机的八拍运行,代码如下:

根据步进电机的八拍运行时序,在原有的case结构中多添加4种情况,便可以实现步进电机的八拍运行,代码如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity state_stepper_b is

port(clk,dir:in std_logic;

q:out std_logic_vector(3 downto 0));

end state_stepper_b;

architecture arc of state_stepper_b is

type state_type is (s0,s1,s2,s3,s4,s5,s6,s7);

signal state:state_type;

begin

process(clk)

begin

if clk'event and clk='1' then

if dir='1' then

case state is

when s0=> state <=s1;

when s1=> state <=s2;

when s2=> state <=s3;

when s3=> state <=s4;

when s4=> state <=s5;

when s5=> state <=s6;

when s6=> state <=s7;

3.顺序锁设计

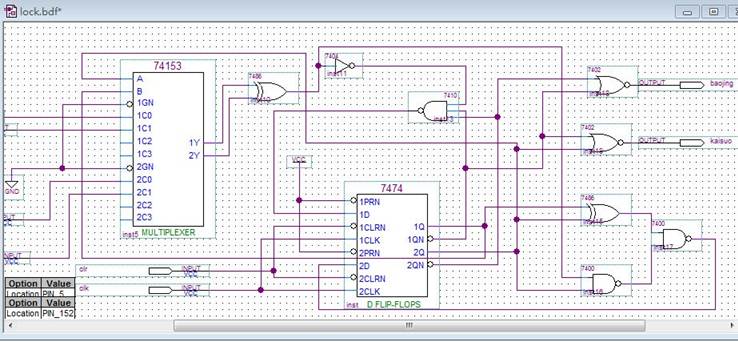

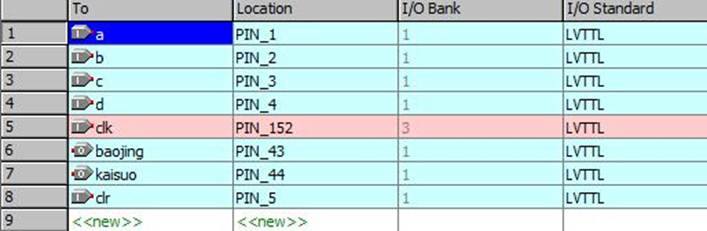

在Quartus II中,不仅仅支持对VHDL文件的编译,也支持对原理图文件的编译,由于程序的编写能力有限,我们采用原理图实现顺序锁设计,下面是画好的原理图和管脚分配,只要在器件选择框内输入正确的名称即可,如VCC,GND,input,7474等,使用也很方便。

在Quartus II中,不仅仅支持对VHDL文件的编译,也支持对原理图文件的编译,由于程序的编写能力有限,我们采用原理图实现顺序锁设计,下面是画好的原理图和管脚分配,只要在器件选择框内输入正确的名称即可,如VCC,GND,input,7474等,使用也很方便。

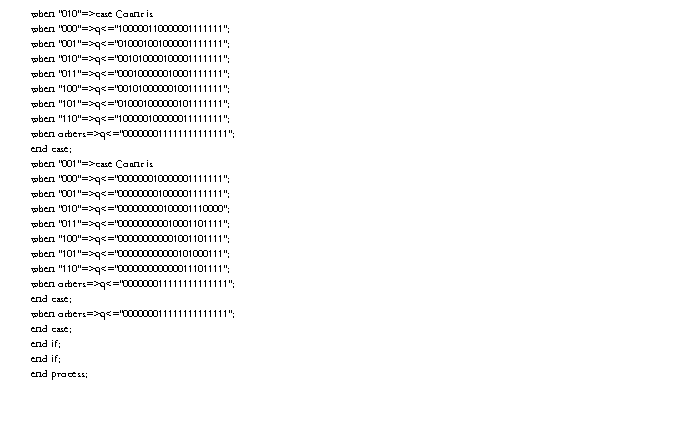

4.在交通灯设计

在提供的程序文件中,LED点阵始终显示 为红色,为了使设计更切合实际,我们通过修改程序代码将显示分为两种情况,“X”为红色,左转和直行为绿色,同之前修改类似,也是在case语句中增加,修改后的部分代码如下:

process (Clock)

process (Clock)

variable a:std_logic_vector(2 downto 0);

begin

if Clock'event and Clock='1' then

if Reset='1' then

q<="000000000000000000000";

else

if Count="111" then

Count<="000";

else

Count<=Count+1;

end if;

a:=Strait_A&Block_A&Turn_A;

case a is

when "100"=>case Count is

when "000"=>q<="000000010000001111111";

when "001"=>q<="000000001000001111111";

when "010"=>q<="000000000100001011111";

when "011"=>q<="000000000010000000000";

when "100"=>q<="000000000001001011111";

when "101"=>q<="000000000000101111111";

when "110"=>q<="000000000000011111111";

when others=>q<="000000011111111111111";

end case;

四. 总结与感悟

经过几节课的学习,我觉得FPGA的学习应该做好预习工作,最好提前安装一下Quartus II。提前练习程序编写应该有很大帮助,另外,最好使用Quartus II5.0 。这个版本的文件小,而那些新的版本文件太大安装不方便。

要想掌握好VHDL语言,仅靠三节课的学习是远远不够的,我们还要对FPGA进行更多的学习和研究。FPGA与常见的单片机相比,虽然价格要贵一些,但是引脚多,功能强大,特别适用于对信号的处理,因而用FPGA做控制芯片是一个不错的选择。