数字钟实验报告

1. 设计要求

在Xilinx FPGA上实现可以校时和清零的数字钟。

2. 实验程序

下面是采用8421BCD计数,并行在一个模块中实现时钟的Verilog程序。时钟主程序可以用一个模块实现,另外还有数码管动态显示、初始化、校时和计时模块。主时钟(50MHz)分频得到秒信号,计秒到60时分加1,计分到60时,分清零。 //顶层设计

module clock(input clk,

input en,

input key1,

input key2,

input key3,

input key4,

output sec,

output wire[7:0] seg,

output wire[3:0] digit

);

wire[3:0] num0,mum1,num2,num3;

disp u0(clk,num0,mum1,num2,num3,seg,digit);

clk_gen u1(clk,en,key1,key2,key3,key4,sec,num0,mum1,num2,num3);

endmodule

////////////////////////////////////数码管动态显示

module disp(input clk,

input [3:0] num0,

input [3:0] num1,

input [3:0] num2,

input [3:0] num3,

output reg[7:0] sm_seg,

output reg[3:0] an

);

reg[1:0] s;

reg[3:0] digit;

reg[16:0] clkdiv;

always@(*)

begin

an=4'b1111;//禁止所有数码管显示

s<=clkdiv[16:15];//间隔2.6ms使能an

an[s]=0;//根据s使能数码管其中之一

case(s)//根据s取对应的数码管上要显示的数据

0:digit<=num0;

1:digit<=num1;

2:digit<=num2; 3:digit<=num3; default:digit<=num0; endcase

case(digit)//七段译码表,跟书上的其实是一样的,只不过用的是16进制

4'h0 : sm_seg = 8'hc0; // "0"

4'h1 : sm_seg = 8'hf9; // "1"

4'h2 : sm_seg = 8'ha4; // "2"

4'h3 : sm_seg = 8'hb0; // "3"

4'h4 : sm_seg = 8'h99; // "4"

4'h5 : sm_seg = 8'h92; // "5"

4'h6 : sm_seg = 8'h82; // "6"

4'h7 : sm_seg = 8'hf8; // "7"

4'h8 : sm_seg = 8'h80; // "8"

4'h9 : sm_seg = 8'h90; // "9"

default : sm_seg = 8'hff; // "x"

endcase

end

always@(posedge clk)//主时钟计数:50MHz时钟,周期20ns,计数到1FFFFh时长2621420ns,约2.6ms

clkdiv<=clkdiv+17'd1;

endmodule

///////////////////////////////////////////初始化

module clk_gen(input clk,

input en,

input bt0,

input bt1,

input bt2,

input bt3,

output reg sec,

output [3:0] num0,

output [3:0] num1,

output [3:0] num2,

output [3:0] num3

);

reg[25:0] ctr;

reg[3:0] time[3:0];

reg[7:0] s;

assign num0=time[0];

assign num1=time[1];

assign num2=time[2];

assign num3=time[3];

always@(posedge clk)//产生秒脉冲

begin

ctr<=ctr+26'd1;

if(ctr==25000000-1)

begin

ctr<=0;

sec<=~sec;

end

end

//wire sen;

//assign sen=(sec)|(bt0)|(bt1)|(bt2)|(bt3);

always@(negedge sec)//校时阶段

if(!en)//使能无效

begin

if(bt0)

begin

time[0]<=time[0]+4'd1;

if(time[0]==9) time[0]<=0;

end

else if(bt1)

begin

time[1]<=time[1]+4'd1;

if(time[1]==5) time[1]<=0;

end

else if(bt2)

begin

time[2]<=time[2]+4'd1;

if(time[2]==9) time[2]<=0;

end

else if(bt3)

begin

time[3]<=time[3]+4'd1;

if(time[3]==2) time[3]<=0;

end

if(time[3]==2 && time[2]==3 && bt2 || time[3]==2 && time[2]==3 && bt3)//显示23时,按下左一或左二按钮可回到00

begin

time[2]<=0;

time[3]<=0;

end

end

else//使能有效,计时阶段

begin

s<=s+1;//s计数,当s从0到59时,计秒得分 if(s==59)

begin

s<=0;

time[0]<=time[0]+4'd1;

if(time[0]==9)

begin

time[0]<=0;

time[1]<=time[1]+4'd1;

if(time[1]==5)

begin

time[1]<=0;

time[2]<=time[2]+4'd1;

if(time[3]==2 && time[2]==3) begin

time[2]<=0;

time[3]<=0;

end

if(time[2]==9)

begin

time[2]<=0;

time[3]<=time[3]+4'd1;

end

end

end

end

end

endmodule

3.编写约束文件

#Basys2约束文件

NET "clk" LOC = "B8";

NET"seg[0]" LOC="L14";

NET"seg[1]" LOC="H12";

NET"seg[2]" LOC="N14";

NET"seg[3]" LOC="N11";

NET"seg[4]" LOC="P12";

NET"seg[5]" LOC="L13";

NET"seg[6]" LOC="M12";

NET"seg[7]" LOC="N13";

NET "digit[0]" LOC = "F12";

NET "digit[1]" LOC = "J12";

NET "digit[2]" LOC = "M13";

NET "digit[3]" LOC = "K14";

NET "key4" LOC = "A7"; # Bank = 2, Signal name = BTN3

NET "key3" LOC = "M4"; # Bank = 2, Signal name = BTN2

NET "key2" LOC = "C11"; # Bank = 2, Signal name = BTN1

NET "key1" LOC = "G12"; # Bank = 2, Signal name = BTN0

NET "en" LOC = "P11"; # Bank = 2, Signal name = sw0

NET "sec"LOC="M5";

4.心得体会

这次设计数字钟的EDA实验让我了解了模块化的设计思路,熟悉了对于七段译码器和脉冲发生器的编程步骤,并且对时钟置数的概念有了更深的了解,在程序的调试中进一步掌握了Verilog语言。数字钟经检验达到了实验的预期目的,也锻炼了我的自主学习能力、理解能力、学习效率和创造能力。

第二篇:数字钟实验报告 3

计数、译码、显示与简易数字钟插板

院系: 光电信息工程

班级: 光电1101

姓名: 张逸飞

学号: U201114938

指导老师: 左东红

一、实验目的:

1、掌握中规模集成计数器CC40161的逻辑功能。

2、掌握计数、译码、显示电路的实现与调试方法。

3、掌握小规模数字系统装调方法。

二、实验任务与要求:

采用中规模集成电路设计完成数字钟基本功能及扩展功能。

基本功能:

1. 具有“秒”、“分”、“时”计时的功能,小时按计数器按24小时制;

2. 具有校时功能,能对“分”和“时”进行调整;

3. 具有手动输入设置定时闹钟的功能。

扩展功能(两组合作完成)

1. 仿广播电台整点报时: 在59分(51、53、55、57)秒发出低音500Hz信号,在59分59秒时发出一次高音1kHz信号,音响持续1秒钟,在1kHz音响结束时刻为整点。

2. 报整点:几点敲几下。

三、电路的设计过程:

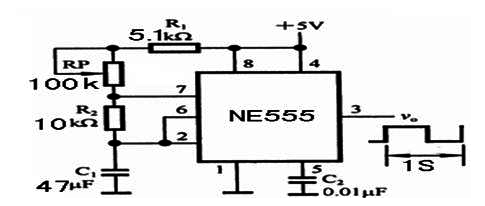

1、振荡器的设计:

选用NE555构成多谐振荡器,使振荡频率f=1Hz,电路参数如下图所示。输出端正好可得到1Hz的标准脉冲。

2、分、秒、时计数器的设计:

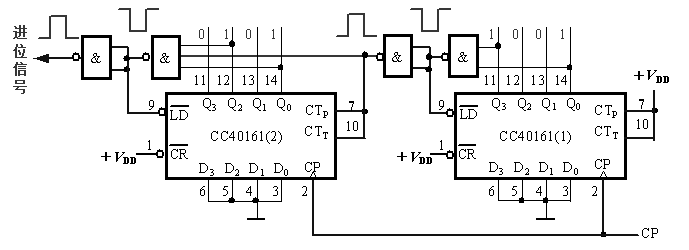

分和秒计数器都是模为60的计数器,其计数规律为00-01…-58-59-00…,选CD40161作六、十进制计数器,再将它们级联组成模数为60的计数器。利用并行进位的级联方式,如下图:

时计数器是一个24进制计数器,其计数规律为00—01—…—22—23—00…即当数字钟运行到23时59分59秒时,秒的个位计数器再输入一个秒脉冲时,数字钟应自动显示为00时00分00秒。

选两片CD40161级联组成模24的计数器构成时计数器。级联方式跟分秒计数器一样,即也用并行进位方式。

四、调试过程:

调试过程中发现计数器到9之后不能马上跳0,原因是使用同步清零需要等到下一个上升沿到来才会清零,改为异步清零后解决了这一问题。

五、实验的收获、体会与改进建议:

在本次数字钟的设计过程中,更进一步熟悉了芯片的结构,掌握了各芯片的工作原理及其具体的使用方式。在连接模六十计数器时熟悉了芯片引脚的功能。在连接电路的过程中,出错的主要原因都是导线和芯片的接触不良,还有连线错误也会导致出错。

本次试验主要的是连线与调试,需要考虑怎样正确连线并能正常显示结果,但是对电路本身的原理不是很清楚。不过总的来说,通过本次设计试验,增强了实验的动手能力及思考能力。