电子电路数字钟设计说明书

电子电路课程设计总结报告

同济大学

项目名称:数字钟

学院:机械工程学院

专业:

班级:

姓名:

指导老师:

1

电子电路数字钟设计说明书

一、课程设计题目??????????????3

二、课程设计的设计任务和基本要求??????3

三、课程设计题目分析 ???????????3

四、课程设计的电路设计部分 ????????5

五、课程设计的总电路图 ??????????9

六、元器件的使用说明????????????11

七、课程设计的心得体会???????????15

八、参考文献????????????????15

2

电子电路数字钟设计说明书

一、课程设计题目: 数字钟

二、课程设计任务和基本要求:

1)设计数字钟电路(每人一组,独立完成)

基本功能:准确计时,以数字形式显示时、分、秒的时间;小时的计时要求为24进位,分和秒的计时要求为60进位;能快速校正时、分的时间。

扩展功能:定点闹时功能,比如在7时59分发出闹时信号,持续时间为1分钟;整点报时功能,比如计时到整点时发出声音,且几点响几声。

2)提交设计报告(书面形式)

画出所设计电路的结构方框图;分析各部分的工作原理;所含集成电路的管脚和功能说明;通过Multisim 等软件对所设计电路进行仿真,提交仿真电路的原理图(电子版)。

3)制作数字钟(两人一组共同完成)

实现基本功能,给定统一的元器件,按照自己的设计方案在面包板上搭建实际电路,并达到设计要求。

三、课程设计题目分析:

☆ 设计要点

●设计一个精确的秒脉冲信号产生电路

●设计60进制、24进制计数器

●设计译码显示电路

●设计操作方面的校时电路

●设计整点报时电路

☆ 工作原理

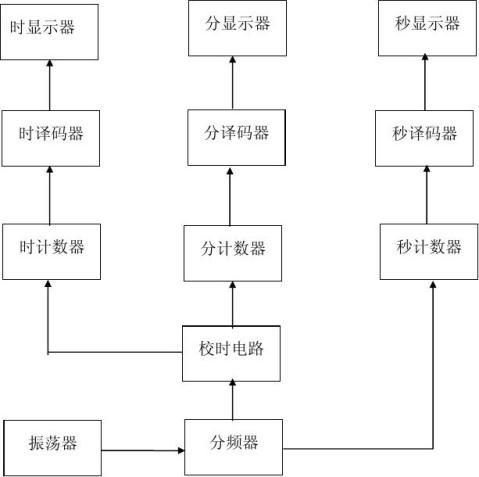

数字电子钟由信号发生器、“时、分、秒”计数器、译码器及显示器、校时电路、整点报时电路等组成。秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,一般用555构成的振荡器加分频器来实现。将标准秒脉冲信号送入“秒计数器”,该计数器采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计数器,可以实现一天24h的累计。译码显示电路将“时、分、秒”计数器的输出状态经七段显示译码器译码,通过六位LED显示器显示出来。整点报时电路是根据计时系统的输出状态产生一个脉冲信号,然后去触发音频发生器实现报时。校时电路是来对“时、分、秒”显示数字进行校对调整。其数字电子钟系统框图如下:

3

电子电路数字钟设计说明书

各部件

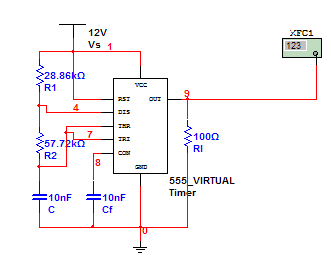

(1)时钟振荡电路。 555定时器与RC组成的多谐振荡器可以产生1kHz的方波信号,可以作为时间标准信号源。

(2)秒脉冲产生电路。

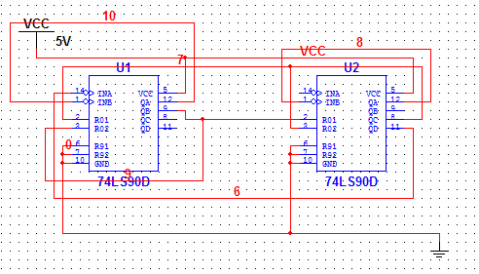

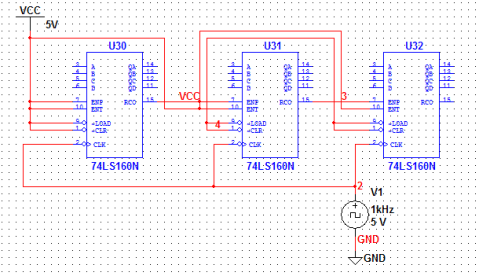

分频器电路将1kHz的方波信号经1000次分频后得到1Hz的方波信号供秒计数器进行计数。分频器实际上也就是计数器。

(3)计数电路。

电子时钟分为小时、分钟和秒,其中小时为二十四进制,分钟和秒均为六十进制,输出可用数码管显示,所以要求二十四进制为00000000~00100011计数,六十进制为00000000~01100000计数,并且均为8421编码形式。

(4)校时校分电路。

4

电子电路数字钟设计说明书

在刚接通电源或者时钟走时出现误差时,则需要进行时间的校准。通常可以在整点时刻和利用电台或电视台的信号进行校准,也可以在其他时刻利用别的时间标准进行校对。

(5)译码驱动电路。

译码驱动电路将计数器输出的8421码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

(6)显示数码管。

本设计选用LED七段数字显示数码管,检验选用四段数字显示。

四、课程设计的电路设计部分:

555振荡器555多谐振荡器产生1kHz。利用555和3个电阻、两个电容完成电路。其中Cf为刚干扰电容,设计电路前根据相关频率计算公式计算R1 R2 C的具体取值并通过示波器的显示来进行微调。

公式如下:f=1/T=1.43/(R1+2*R2)*C

仿真电路如下:

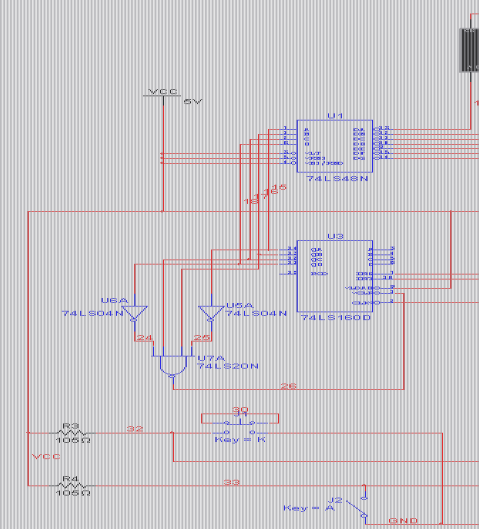

分频器 74LS160在级联使用时一定注意两个使能端EP、ET的设置,只有两个均为高电平才能计数,当第三级控制时一定是第一级和第二级一同控制第三级。如下图所示,第二级的EP、ET一同由第一级的RCO控制,第三级的EP由第二级的RCO控制,而ET由第一级的RCO控制,这样保障了第三级的进位是前两个芯片均计满益处时。

5

电子电路数字钟设计说明书

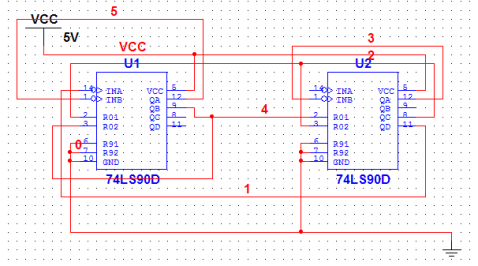

60进制计数器

由两片74LS290构成六十进制计数器,联接方式如下图,将一片74LS290作为个位(下图芯片1),另一片74LS290作为十位(下图芯片2)。秒计数器的十位和个位,输出脉冲除用作自身清零外,同时还作为分计数器的输入脉冲CP0。下图电路即可作为秒计数器,也可作为分计数器

:

图4 60 进 制 计 数 器

24进制计数器

由两片74LS290构成的二十四进制计数器,连接图如下:将一片74LS290作为个位(下图芯片1),另一片作为十位(下图芯片2),当个位值是4,同时十位值是2的时候,两片同时清零。

6

电子电路数字钟设计说明书

图5 24 进 制 计 数 器

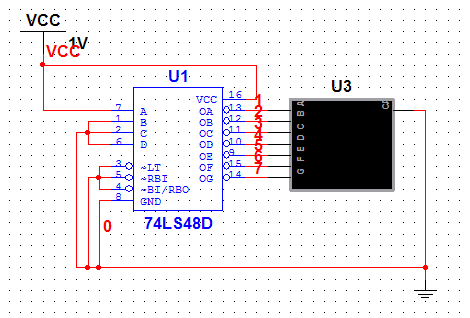

译码显示电路

译码电路的功能是将秒、分、时计数器的输出代码进行翻译,变成相应的数字。用与驱动LED七段数码管的译码器常用的有74LS247。74LS247是BCD-7段译码器/驱动器,输出高电平有效,专用于驱动LED七段共阴极显示数码管。若将秒、分、时计数器的每位输出分别送到相应七段译吗管的输入端,便可以进行不同数字的显示。在译码管输出与数码管之间串联电阻R作为限流电阻。在模拟过程中,我们直接选用带有译码器的显示器,也就是将译码器和显示器合并成一个元件。

6 译码显示电路 图

校正模块

7

电子电路数字钟设计说明书

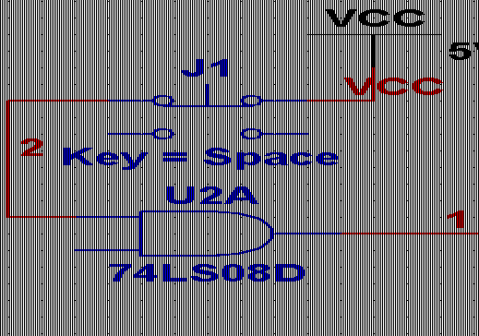

校正电路的工作原理:校时校分电路基本一致,这里只仿真校分电路,方法是控

制六十进制的时钟输入端CP,使用两个三态门或者把秒进位信号(V2信号源仿真)加入,或者把校分的按键信号J1加入,J2用来控制校分和计分切换,由于两个三态门U10A和U11A的使能端有效电平刚好相反,J2接地时为校分功能,J2不接地时为计分功能。校时电路与此电路基本一致。

图9 时校正连接电路

上电复位

在计数器清零端处接一个或门即可。

8

电子电路数字钟设计说明书

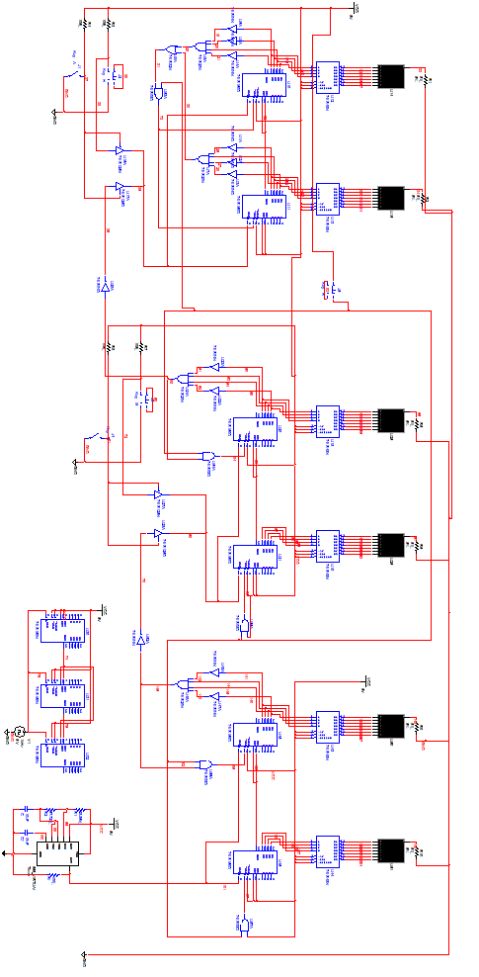

五、总电路图:

9

电子电路数字钟设计说明书

10

电子电路数字钟设计说明书

六、元器件的使用说明:

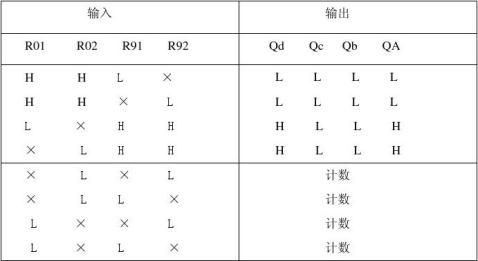

集成异步十进制计数器74LS90

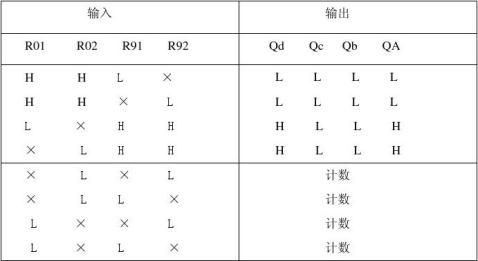

集成异步十进制计数器74LS90它是二-五-十进制计数器,若将Qa与CPB相连从CPA输入计数脉冲其输出Qd、Qc、Qb、Qa便成为8421码十进制计数器;若将Qd与CPA相连,从CPB输入计数脉冲其输出Qd、Qc、Qb、Qa便成为5421码十进制计数器。74LS90具有异步清零和异步置九功能。当R0全是高电平,R9至少有一个为低电平时,实现异步清零。当R0至少有一个低电平,R9全是高电平时,实现异步置九。当R0、R9为低电平时,实现计数功能。

8421 BCD码十进制 5421 BCD码十进制

74LS90功能表如下:

11

电子电路数字钟设计说明书

555定时器

振荡器由555定时器构成。在555定时器的外部接适当的电阻和电容元件构成多谐振荡器,再选择元件参数使其发出标准秒信号。555定时器的功能主要由上、下两个比较器C1、C2的工作状况决定。比较器的参考电压由分压器提供,在电源与地端之间加上VCC电压,且控制端VM悬空,则上比较器C1的反相端“-”加上的参考电压为2/3VCC,下比较器C2的同相端“+”加上的参考电压为1/3VCC。若触发端 S的输入电压V2≤1/3VCC,下比较器C2输出为“1”电平,SR触发器的S输入端接受“1”信号,可使触发器输出端Q为“1”,从而使整个555电路输出为“1”;若阈值端R的输入电压V6≥2/3VCC,上比较器C1输出为“1”电平,SR触发器的R输入端接受“1”信号,可使触发器输出端Q为“0”,从而使整个555电路输出为“0”。控制电压端VM外加电压可改变两个比较器的参考电压,不用时,通常将它通过电容(0.01μF左右)接地。放电管T1的输出端Q′为集电极开路输出,其集电极最大电流可达50mA,因此,具有较大的带灌电流负载能力。若复位端 RD加低电平或接地,可使电路强制复位,不管555电路原处于什么状态,均可使它的输出Q为“0”电平。只要在555定时器电路外部配上两个电阻及两个电容元件,并将某些引脚相连,就可方便地构成多谐振荡器。

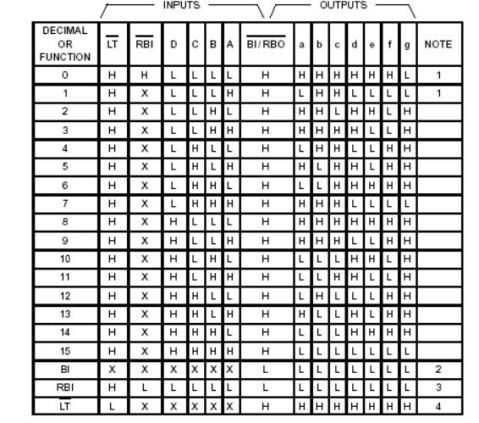

译码器 74LS48

74LS48芯片是一种常用的七段数码管译码器驱动器,下面是74LS48的引脚图和功能表。

12

电子电路数字钟设计说明书

74LS48功能表

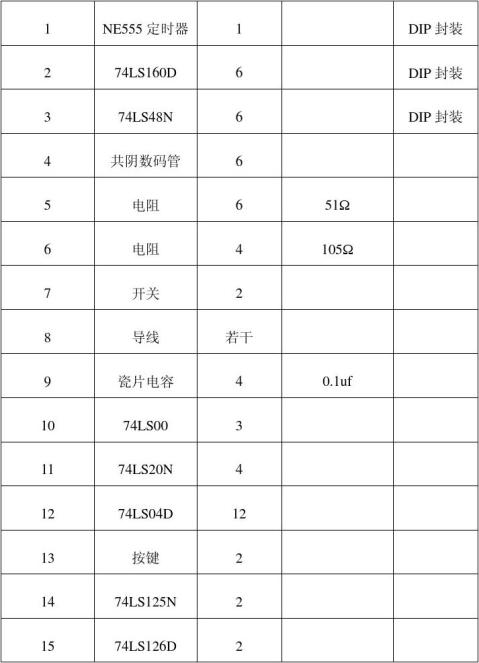

元器件清单

13

电子电路数字钟设计说明书

14

电子电路数字钟设计说明书

七、实习心得:

拿到这份实习任务,因为当初不认真学习,还有时间很久的缘故,根本无从下手,而通过再次翻书,借鉴同学的,与同学讨论等等,让我对数字电路以及各种元器件有了重新的了解。而且通过设计发现总会有一些小的错误,让我在细节的注意上有了更深刻的了解。还有就是发现理论和实际差距还是很大的。

八、参考文献:

《电工学(第六版)》上、下册

社

《Multisim 2001电路设计及仿真入门与应用》 郑步生 ·电子工业出版社 《数字电子技术基础》 杨颂华 ·西安电子科技大学出版社 《电子线路设计指导》 李银华 主编 ·北京航空航天大学出版社

《微型计算机原理与接口技术》 冯博琴 吴宁 主编·清华大学出版社 秦曾煌 主编 ·高等教育出版

15

第二篇:同济实验报告

会计实务总结报告

——烟台同济经贸有限公司

在这次会计实习中,我可谓受益非浅。毕业实习是学生大学学习完成全部课程后的最重要的实践环节。通过这次的实习,我对自己的专业有了更为详尽而深刻的了解,也是对这几年大学里所学知识的巩固与运用。

从这次实习中,我体会到了实际的工作与书本上的知识是有一定距离的,并且需要进一步的再学习。由于会计行业的特殊性我只能参加财务部门中较为简单的工作,如出纳及帮助会计进行账目的核对等工作,但是,这帮助我更深层次地理解现在的企业会计,并且我对会计分录、记账、会计报表的应用也有了进步的掌握。不在局限于书本,而是有了一个比较全面的了解。实践暴露了我许多知识上的不足,也是对理论知识的一种补足。会计工作中的每一个步骤都是十分重要的,只要有一个部分出差错,那么就会牵连到其他的部分,所以会计真的不是简单的算算记记,这是一项十分严谨的管理活动,工作前先做好个人工作计划,有条不紊地进行。此外,我们在一起相互交流,相互促进。为我们以后进一步走向社会打下坚实的基础。在这次的社会实践中,学到了很多在课堂上根本就学不到的知识,打开了视野,增长了见识,因此在实践中锻炼了自己,巩固了知识