实验三 触发器及其应用

一、 实验目的

1. 熟悉基本D触发器的功能测试。

2. 了解触发器的两种触发方式(脉冲电平触发和脉冲边沿触发)及触发特点。

3. 熟悉触发器的实际应用。

二、 试验设备

1. 数字电路试验箱

2. 数字双踪示波器

3. 函数发生器

4. 74LS00、74LS74

三、 试验原理

触发器是一个具有记忆功能的二进制信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即“0”和“1”,在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。触发器呦集成触发器和门电路(主要是“与非门”)组成的触发器。按其功能可分为有RS触发器、JK触发器、D触发器、T和T’功能等触发器。触发方式有电平触发和边沿触发两种。

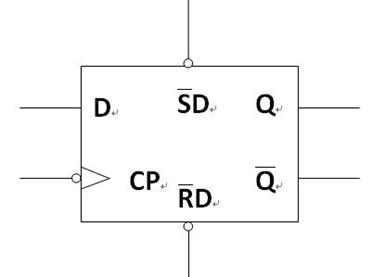

D触发器在时钟脉冲CP的前沿(正跳变0→1)发生翻转,触发器的次态 取决于CP脉冲上升沿到来之前D端的状态,及

取决于CP脉冲上升沿到来之前D端的状态,及 =D。因此,它具有置0、置1两种功能。由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

=D。因此,它具有置0、置1两种功能。由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。 和

和 分别是决定触发器初始状态

分别是决定触发器初始状态 的直接置0、置1端。当不需要强迫置0、置1时,

的直接置0、置1端。当不需要强迫置0、置1时, 和

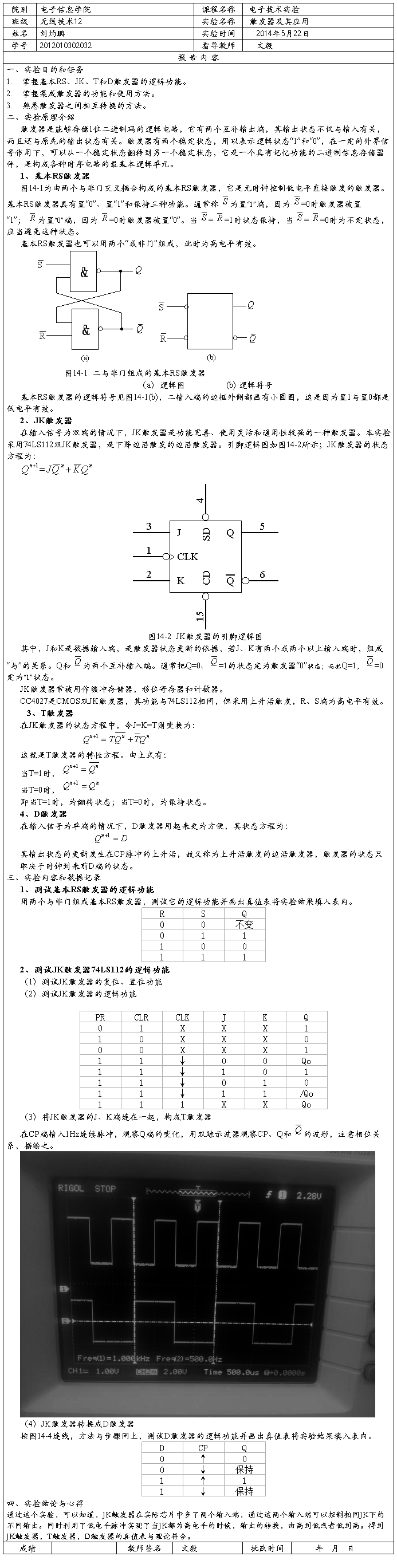

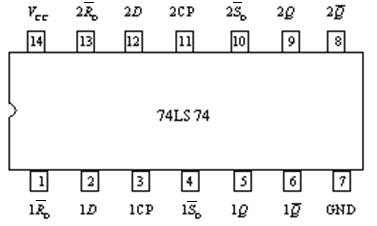

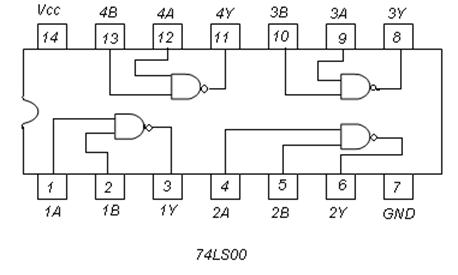

和 端都应置高电平(如接+5V电源)。74LS74(CC4013)等均为上升沿触发的边沿触发器。图(1)为74LS74的引脚图,图(2)为其逻辑图,表(1)为其真值表。D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等。74LS000的引脚排列如图(3)。

端都应置高电平(如接+5V电源)。74LS74(CC4013)等均为上升沿触发的边沿触发器。图(1)为74LS74的引脚图,图(2)为其逻辑图,表(1)为其真值表。D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等。74LS000的引脚排列如图(3)。

图(1)

图(2)

表(1)

图(3)

四、 试验内容

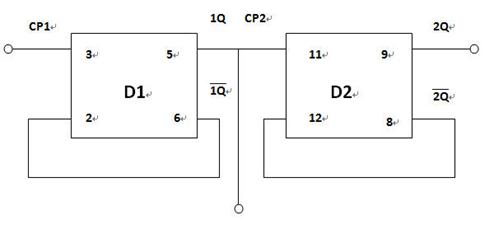

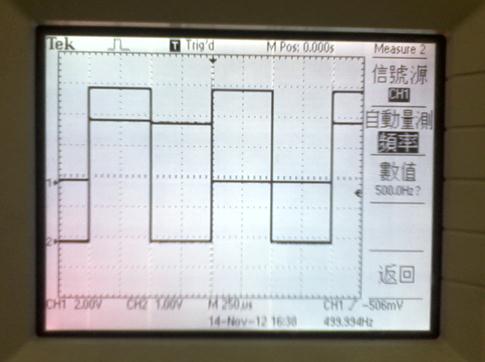

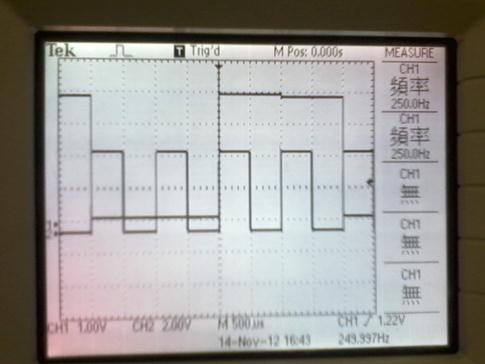

1. 用双D触发器构成二分频器

2. 用双D触发器构成四分频器

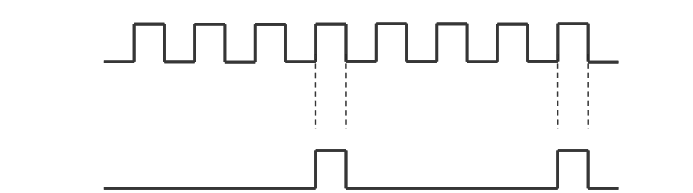

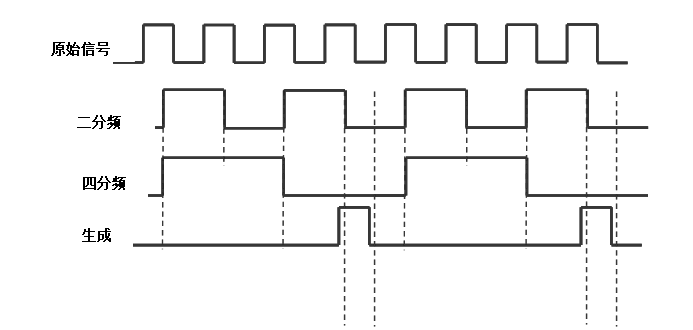

3. 生成如图所示时序脉冲

五、 试验结果

1和2设计

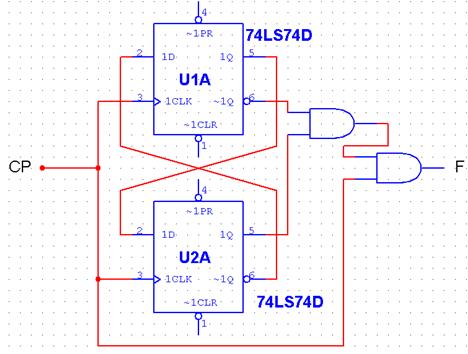

连接示意图见图(4)。在CP1端加入1KHz,峰峰值为5.00V,平均值为2.50V的连续方波,并用示波器观察CP,1Q,2Q各点的波形,见图(5)。

图(4)

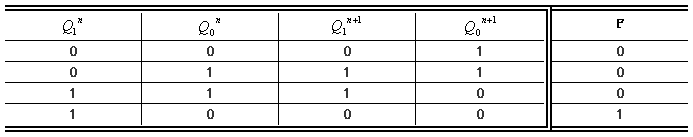

3设计

A) 逻辑分配

B) 特征方程

=

= =

=

=

= =

=

F=

CP

CP

C) 电路图

图(5)

第二篇:触发器及其应用实验报告

学生实验报告