EDA实验报告

实验目的:

1.触发器的工作原理。

2.基本时序电路的VHDL代码编写。

3.按键消抖电路应用。

4.定制LPM原件。

5.VHDL语言中元件例化的使用。

6.移位寄存器的工作原理及应用。

实验要求:

1.运用LPM原件定制DFF触发器,并调用LPM 定制的DFF触发器,用VHDL语言的元件例化实现消抖电路并了解其工作原理。

2. 移位寄存器是用来寄存二进制数字信息且能进行信息移位的时序逻辑电路。根据移位寄存器存取信息的方式不同可分为串入串出、串入并出、并入串出、并入并出4种形式,并通过数码管显示出来。

实验原理:

1.消抖电路

由于一般的脉冲按键与电平按键采用机械开关结构,其核心部件为弹性金属簧片。按键信号在开关拨片与触点接触后经多次弹跳才会稳定。本实验采用消抖电路消除抖动以获得一个稳定的电平信号。

2.移位寄存器

移位寄存器具有左移、右移、并行输入数据、保持及异步清零5种功能。其中A、B、C、D为并行输入端, 、

、 、

、 、

、 为并行输出端;SRSI为右移串行输入端,SLSI为左移串行输入端;S1、S0为模式控制端;CLRN为异步清零端;CLK为时钟脉冲输入端。

为并行输出端;SRSI为右移串行输入端,SLSI为左移串行输入端;S1、S0为模式控制端;CLRN为异步清零端;CLK为时钟脉冲输入端。

实验具体步骤:

1.消抖电路

(1).用lpm定制DFF

<1>.设置lpm_ff选择Installed Plug-Ins→Storage→lpm_ff项;

<2>.设置输入data为1位,clock为时钟信号,类型为D型;

<3>.添加异步清零和异步置1;

其VHDL语言为:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY lpm;

USE lpm.all;

ENTITY mydff IS

PORT

(

clock : IN STD_LOGIC ;

data : IN STD_LOGIC ;

q : OUT STD_LOGIC

);

END mydff;

ARCHITECTURE SYN OF mydff IS

SIGNAL sub_wire0 : STD_LOGIC_VECTOR (0 DOWNTO 0);

SIGNAL sub_wire1 : STD_LOGIC ;

SIGNAL sub_wire2 : STD_LOGIC ;

SIGNAL sub_wire3 : STD_LOGIC_VECTOR (0 DOWNTO 0);

COMPONENT lpm_ff

GENERIC (

lpm_fftype : STRING;

lpm_type : STRING;

lpm_width : NATURAL

);

PORT (

clock : IN STD_LOGIC ;

q : OUT STD_LOGIC_VECTOR (0 DOWNTO 0);

data : IN STD_LOGIC_VECTOR (0 DOWNTO 0)

);

END COMPONENT;

BEGIN

sub_wire1 <= sub_wire0(0);

q <= sub_wire1;

sub_wire2 <= data;

sub_wire3(0) <= sub_wire2;

lpm_ff_component : lpm_ff

GENERIC MAP (

lpm_fftype => "DFF",

lpm_type => "LPM_FF",

lpm_width => 1

)

PORT MAP (

clock => clock,

data => sub_wire3,

q => sub_wire0

);

END SYN;

(2).VHDL结构式描述顶层

--Top level entity xiaodou

library ieee;

use ieee.std_logic_1164.all;

entity xiaodou is

port( d_in,clk:in std_logic;

clk_out:out std_logic);

end xiaodou;

architecture xiaodou_arch of xiaodou is

component mydff is --元件例化

PORT

(

clock : IN STD_LOGIC ;

data : IN STD_LOGIC ;

q : OUT STD_LOGIC

);

END component;

signal x,y:std_logic;

begin

dff1:mydff port map(clock=>clk,data=>d_in,q=>x);

dff2:mydff port map(clk,x,y);

clk_out<=x and (not y);

end xiaodou_arch;

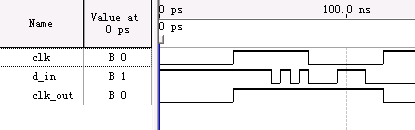

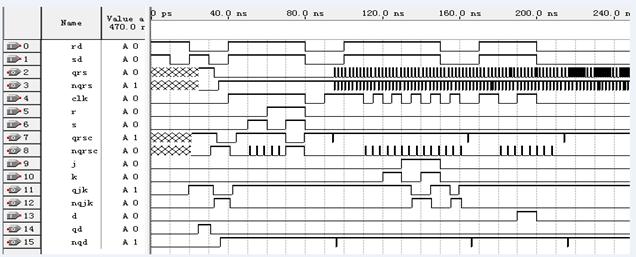

(3).功能仿真波形:

2.移位寄存器

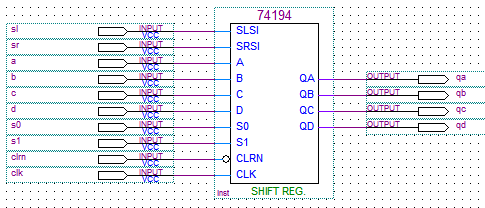

(1).74194功能验证电路

(2).74194功能仿真结果

仿真分析:

clrn=1,clk上升时,s为11,移位寄存器并行置数,此时abcd=1010,q_abcd=1010;

clrn=0,移位寄存器进行清零,此时有q_abcd=0000;

clrn=1,clk上升时,s为01,sl_sr为01,移位寄存器串行右移补1,输出q_abcd=1000;

clrn=1,clk上升时,s为01,sl_sr为10,移位寄存器串行右移补0,输出q_abcd=0100;

clrn=1,clk上升时,s为10,sl_sr为10,移位寄存器串行左移补1,输出q_abcd=1001;

clrn=1,clk上升时,s为10,sl_sr为01,移位寄存器串行左移补0,输出q_abcd=0010。

结论:输出结果与74194的真值表相符,得仿真验证正确。

思考题

1.VHDL元件例化语句作用是什么?如何调用标准的jkff(tff)元件?

答:元件例化是用于结构式描述方式时调用库元件或底层实体。元件例化是系统层次化设计的一种重要途径。

元件例化语句由元件声明语句和元件描述语句两部分构成。

格式:component 元件名

[generic <参数说明>;]

port <端口说明>;

end component;

标号:元件名 port map([端口名=>]信号名,...)

2.VHDl语言中边沿触发的signal如何描述?VHDL描述时序电路是signal的作用是什么?

答:上升沿:clk’=1 ; 下降沿:clk’=0

在时序电路中signal作为中间信号,起连线内部电路的作用。

3.lpm_ff定制时clear、load、set输入有哪两类?

答:clear、load、set有synchronous inputs和asynchronous inputs两类,S类为同步清零操作,A类为异步清零操作。

4.简单说明移位寄存器的概念及应用情况?

答:移位寄存器是用来寄存二进制数字信息且能进行信息移位的时序逻辑电路。根据移位寄存器存取信息的方式不同可分为串入串出、串入并出、并入串出、并入并出4种形式,并通过数码管显示出来。移位寄存器可构成计数器、顺序脉冲发生器、串行累加器、串并转换。

5.仿真常规步骤是什么?有什么注意事项?

答:

1、参数设置:Grid size 和 Endtime。

2、添加节点或总线后的信号整合与位置分配。注意事项:激励输入信号与待分析输出信号上下放置,界限分明;时钟信号置顶,其他信号按照“异步控制→同步控制→数据输入”顺序想下放置;

3、激励输入及分段仿真。注意事项:将时间轴分为连续的时间段,一时间段完成一小步实验内容,一小段信号激励输入完成后立即生成波形并判断结果;波形正确后再根据下一个实验内容,直至完成所有实验内容仿真。

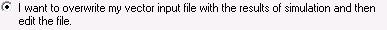

6.如何保存用户的仿真结果波形?

答:产生仿真波形后选择

即可保存至波形文件中。

即可保存至波形文件中。

实验心得

此次实验,让我学习了VHDL语言中的元件例化,并学习编写顶层文件的VHDL代码,了解并掌握了74194移位寄存器的工作原理和功能实现。

第二篇:EDA触发器功能模拟实验报告

EDA技术实验项目报告

项目题目: 触发器功能模拟

姓 名: 左 修 林

院 系: 应用技术学院

专 业: 电子信息工程

学 号: 201015254135

指导教师: 陈 强

综合成绩:

完成时间: 2012年 5月 21日

一、 项目实验内容摘要

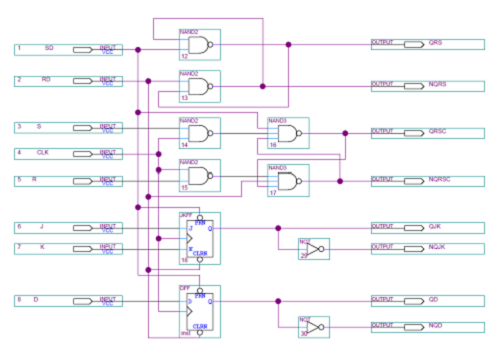

基于FPGA硬件开发板,利用QuartusII软件通过VHDL输入的方式实现基本RS触发器,同步触发器,JK触发器,D触发器同时集成在一个FPGA芯片中模拟功能;

实验原理图:

二、项目实验源代码

library ieee;

use ieee.std_logic_1164.all;

entity mff is

port(sd,rd,r,s,clk,j,k,d:in std_logic;

qrs,nqrs,qrsc,nqrsc,qjk,nqjk,qd,nqd:out std_logic); --定义多触发器I/O.

end mff;

architecture mff of mff is

signal qtp, qbtp,dd,ndd: std_logic;

begin

rsff:process(rd,sd) --基本RS触发器功能模拟

begin

if rd='0' and sd='1' then

qrs<='0';nqrs<='1';

elsif rd='1' and sd='0' then

qrs<='1';nqrs<='0';

elsif rd='1' and sd='1' then null;

end if;

end process rsff;

rsc:process(clk,rd,sd,r,s) --同步RS触发器功能模拟

begin

if sd='0' then

qrsc<='1'; nqrsc<='0';

elsif rd='0' then

qrsc<='0'; nqrsc<='1';

elsif clk='1' then

if r='0' and s='1' then

qrsc<='0';nqrsc<='1';

elsif r='1' and s='0' then

qrsc<='1';nqrsc<='0';

elsif r='0' and s='0' then null;

end if;

end if;

end process rsc;

jk:PROCESS(clk, sd, rd, j, k) --JK触发器功能模拟

BEGIN

IF sd='0' then qtp<='1'; qbtp<='0';

elsif rd='0' THEN qtp<='0';qbtp<='1';

elsif rising_edge(clk) then

if j='0' and k='0' then null;

elsif j='0' and k='1' then

qtp<='0'; qbtp<='1';

elsif j='1' and k='0' then

qtp<='1'; qbtp<='0';

else

qtp<=NOT qtp; qbtp<=NOT qbtp;

end if;

end if;

qjk<=qtp;nqjk<=qbtp;

end process jk;

dff:process (clk,rd,sd,d) --D触发器功能模拟

begin

if (rd='0') then dd<='0'; ndd<='1';

elsif(sd='0') then dd<='1'; ndd<='0';

elsif rising_edge(clk) then dd<=d; ndd<=not d;

end if;

qd<=dd; nqd<=ndd;

end process dff;

end mff;

三、项目实验工具软件的选用以及实验过程

(一)项目实验工具软件的选用:

1、EDA2000实验箱(其他厂家具有同等配置试验箱均可),主要使用:输入:时钟源,按键开关,拨码开关,输出:LED灯;

2、主芯片:EP1K1OTC100-3(大于此规模的芯片亦可);

3、计算机与QUARTUS Ⅱ软件;

(二)实验过程:

1、建立工作文件

2、创建工程

3、编译前设置

4、全程编译

5、时序仿真

6、引脚设置和下载

7、配置文件下载

8、编程配置器件

四、项目实验结果

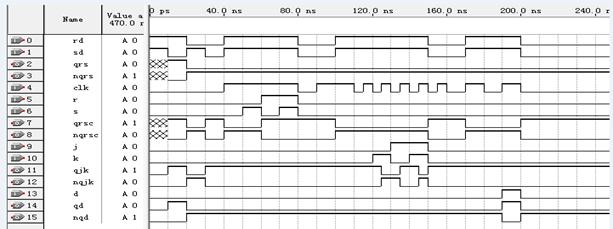

时序仿真波形图 : 功能仿真波形图:

功能仿真波形图:

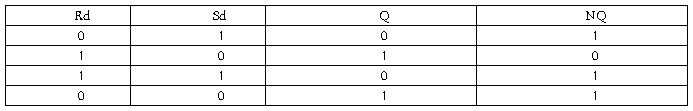

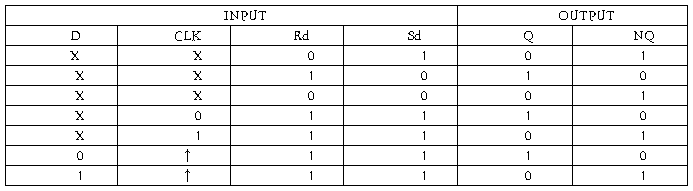

表一 基本RS触发器

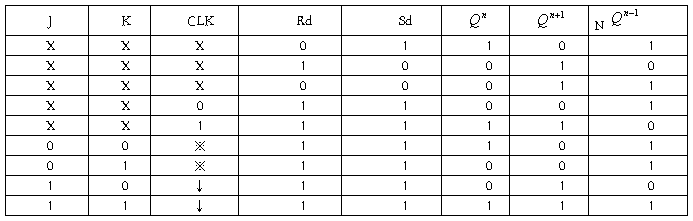

表二 同步RS触发器

表三 J-K触发器

表四 D触发器

五、项目实验分析

本次实验基本实现了预期要求,传统的对触发器的功能验证方法均采用集成电路搭接实现,本次采用EDA技术避免了传统方法连线复杂,效果不理想的缺点。同时能够有助于了解,体会CPLD的高集成度,多I/O的特点。

六、项目实验参考资料

《脉冲与数字电路》、《EDA实验教程 》

七、小组验收记录及评价