大连理工大学大学生创新创业训练计划

项目结题报告

项 目 编 号: 201310141599

项 目 名 称: 空气质量和微量污染物的健康效应研究 项 目 级 别:

项目负责人:

项目类型:

指 导 教 师:

所在学部学院:

校级 王雪雪 创新训练 柳丽芬 化工与环境生命学部

教务处制

大连理工大学大学生创新创业训练计划

项目原创性声明

本人郑重声明:所呈交的项目结题报告以及所完成的作品实物等相关成果,是本人和项目组其他成员独立进行研究工作所取得的成果。除文中已经注明引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写过的作品成果,不侵犯任何第三方的知识产权或其他权利。本人完全意识到本声明的法律结果由本人承担。

项目负责人签名:

年 月 日

项目指导教师审核签名:

年 月 日

空气质量及微量污染物的健康效应研究

摘要:通过对校园各处进行PM2.5的测量,分析其影响因素及健康效应;对空气中的粉尘进行采样,然后对采得的样品进行萃取、浓缩、净化分析,研究粉尘上的多环芳烃、多溴联苯醚等有机物的浓度和分布;最后研究不同滤膜对空气中PM2.5的净化效率,在滤膜上加以不同大小的电压,结果表明有纺布滤膜净化效率高,且在1.0V和2.5V电压下净化效率更高。

关键词:PM2.5、空气净化、健康效应

Research on the health effects of air quality and trace pollutants

Abstract:By around campus PM2.5 measurements, analyze their impact factors and health effects; dust in the air is sampled, and then the samples were mined extraction, concentration and purification analysis, research on polycyclic aromatic hydrocarbons in dust, polybrominated diphenyl ethers and other organic matter concentration and distribution; last of different filters in the air purification efficiency of PM2.5 to the voltage on the filter of different sizes, the results show that there is a high woven fabric membrane purification efficiency, and at 1.0V and higher removal efficiency under 2.5V voltage.

Key words:

一、项目概述

1、项目成员

赵春婷 化工与环境生命学部环境学院 环境科学1101班

王雪雪 化工与环境生命学部环境学院 环境科学1101班

指导老师

柳丽芬 化工与环境生命学部环境学院 职称:教授

研究领域(研究课题)

1、校园周边和室内空气PM2.5甲醛\TVOC\PBDE\PAH污染物水平

2、微量污染物种类和浓度测定方法

3、污染物的净化方法研究

4、微量污染物的健康效应

2.项目的选题背景、目的与意义 选题背景:

空气是指包围在地球周围的气体,它维护着人类及生物的生存。对人类及生物生存起重要作用的是距地面12公里以内的空气层,也就是对流层。清洁的空气是由氮78.06%、氧20.95%、二氧化碳0.03%等气体组成的,这三种气体约占空气总量99.04%,其它气体总和不到千分之一。洁净大气是人类赖于生存的必要条件之一,一个人在五个星期内不吃饭或5天内不喝水,尚能维持生命,但超过5分钟不呼吸空气,便会死亡,人体每天需要吸入10─12立方米的空气。大气有一定的自我净化能力,因自然过程等进入大气的污染物,由大气自我净化过程从大气移除,从而维持洁净大气。

但是近年来随着工业及交通运输业的不断发展,大量的有害物质被排放到空气中,改变了空气的正常组成,使空气质量受到前产生了严重的危害。而空气中的微量污染物在一定范围内不断积累,影响着我们的健康所未有的冲击,因此,研究空气质量和微量污染物的种类、浓度及其净化方法是一种改进空气质量的有效途径。

研究目的:

在当前研究的基础上,测定新型(PM2.5)净化材料\去除途径与效率。

研究意义:

通过研究微量空气污染物的种类、浓度及其净化方法,净化效果对人体健康的益处,为提高空气质量,保护我们的健康,提供科学依据及技术方法。

3.项目实施过程的人员工作分配和完成情况

项目实施过程中,小组二个人分工如下:王雪雪负责项目进度安排、和指导老师进行定期交流。全员全程参与到项目实施当中去。整体完成状况良好。

4.项目实施过程收获和体会

为期一年的创新实验到现在已经结束了,它带给我们的收获是在平时的教学实验中得不到的。没有完善、成熟的实验方法,我们边做边思考着、改进着,一次次的收集、萃取、净化、提纯,甚至在开始时我们还不会用那些仪器。在这过程中我们成功过也失败过,成功让我们无比喜悦,因为这是我们自己动手动脑得到的成果;失败则让我们更加谨慎的思考我们错在哪里并且操作时更加小心规范。不管项目取得结果如何,有了这些,这一年的付出就是值得的。

七、项目总结

PM2.5浓度随地点变化的测量结果表明室外浓度高于室内浓度,人多时高于人少时。

实验采用有纺布滤膜和无纺布滤膜加以不同的电压,在不同空气流量下观察其对PM2.5的净化效果。不同电压对PM2.5净化效果影响:在相对低电压下滤膜对PM2.5的净化效果好,去除率高,如2.5V;滤膜的种类对PM2.5净化效果影响:有纺布滤膜对PM2.5的净化效果好,去除率高;气体流量对PM2.5净化效果影响:在测试条件下,流量为8L/h时的净化效率最好。

八、附录(含图纸、软件、资料或参考文献目录等)

结题报告参照提纲及要求

一、原创性声明

二、中英文对照题目

三、中英文对照摘要(中文摘要限200字)和关键字

四、项目概述

1.项目成员基本情况(人数、学部学院、专业、年级)、指导教师基本情况(职称、专业领域)

2.项目的选题背景、目的与意义

3.项目实施过程的人员工作分配和完成情况

4.项目实施过程收获和体会

五、项目预期成果完成情况和创新点

六、项目说明(创新训练项目:实验方法设计及方案、实施过程、数据分析处理、原因分析说明、解决办法、最终实现功能、特色等;创业训练项目:主要业务或产品生产方法及技术、经营模式及运作情况等)

七、项目总结

八、附录(含图纸、软件、资料或参考文献目录等)

九、附件(包括大学生创新性实验计划项目过程记录册、项目发表论文、专利等成果支撑材料、相关照片说明资料等)

注:

1.项目结题报告用A4纸打印,一式一份,同时提交电子版材料。

2.结题报告相关章节、图表等内容格式要求请参考本科生毕业设计(论文)规范化要求。

第二篇:SRT项目结题报告

SRT项目结题报告 目录

内容摘要...................................................................................................................................2

关键词.......................................................................................................................................2

第一章 概论.............................................................................................................................3

1.1 新型16位教学实验计算机系统的研制背景..........................................................3

1.2 新型16位教学实验计算机系统追求的目标..........................................................3

1.3新型16位教学实验计算机系统的改进之处...........................................................3

第二章 新型实验机的原理设计与实现...............................................................................3

2.1新型实验机的简化逻辑框图.....................................................................................3

2.2新型实验机的运算器部件.........................................................................................3

2.3新型实验机的控制器部件.........................................................................................3

2.4 新型实验机的存储器部件........................................................................................3

2.5 新型实验机的时钟启停电路....................................................................................3

Start.vhd....................................................................................................................................3

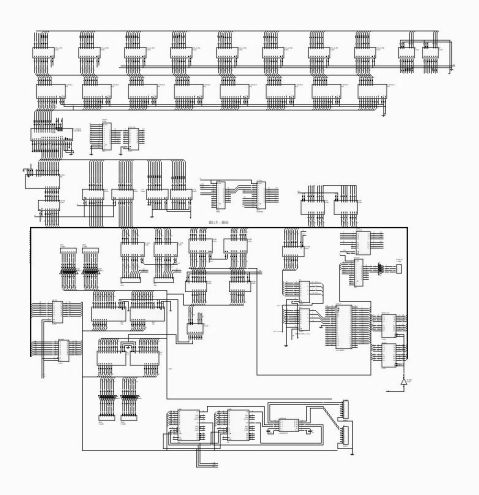

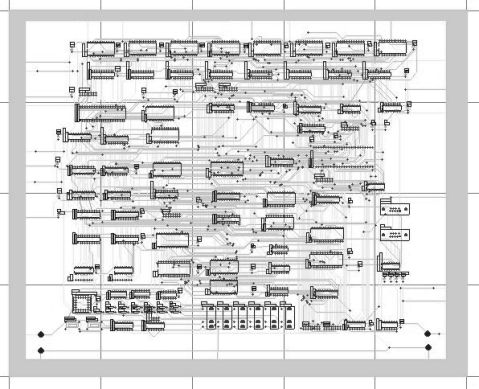

2.6 整机原理图和PCB图..............................................................................................3

第三章 新型实验机的调试.....................................................................................................3

结束语.......................................................................................................................................3

SRT项目结题报告

内容摘要

本文作者在2001-2002学年,在周继群工程师和汤志忠教授、许忠信博士的指导和帮助下,和杜江同学一起,合作进行了新型16位教学实验计算机的设计与开发项目。

这套实验系统是在原有实验计算机系统TEC-2的基础上进行改进,基于AM29116芯片的新的16位实验计算机系统。该系统的运算器采用16位可编程微处理器AM29116,控制器采用微程序方案,支持动态微程序设计,时钟发生电路采用可编程器件ISP1016模拟AM2925部分功能实现。整个实验系统具有更强大的功能和更好的扩展性,可更好的满足教学要求。

在设计开发过程中,我们使用Protel软件将原理图自动转化为PCB图,从而避免了手动设计PCB图的低效性和易错性。另外,考虑到当今硬件实验软件化的趋势,我们在设计和调试的过程中尽可能采用了可编程器件EPROM、FPGA,采用VHDL等语言进行软件模拟与调试。

本文主要介绍实验系统的硬件设计和调试工作。微程序、指令系统以及监控程序等软件设计工作将在杜江同学的报告中涉及。第一部分为概论,主要介绍新型实验系统的研制背景和主要特性。第二部分详细介绍了新型16位实验计算机系统的硬件组成与设计原理,包括主要部件运算器、控制器及存储器的设计。第三部分着重论述了整个实验系统硬件的调试过程。鉴于AM29116芯片是该系统的主要创新之处,论文对它的指令集和外部管脚信号进行了详尽的介绍和深入的分析。

关键词

教学实验计算机系统,AM29116微处理器,控制器,Am2910,微程序,指令系统,指令集

SRT项目结题报告

第一章 概论

1.1 新型16位教学实验计算机系统的研制背景

计算机组成原理课,是计算机系本科生很重要的一门专业基础课。在这门课中,老师要向学生传授单台计算机的组成与运行原理的基础知识,培养学生包括计算机硬件设计、制造、调试和运行维护等多方面的技能,并能训练学生一定的实验动手能力。为了达到这个教学目的,有一套能满足主要教学实验要求的实验计算机系统是必要的。

TEC-2型实验计算机即是为此目的,由清华大学的数十名老师和研究生历经三年多的时间研制出来的一套完整的实验系统。TEC-2系统具有完备性、实验性能高以及应用面广的优点。完备性是指其主要组成方式和PC机差不多,是一台硬软件相对完整、配置小巧合理的计算机系统。实验性能高是指用TEC-2机能完成运算器部件、控制器部件、主存储器部件、总线和几种最常用的外设接口的实验,能很好地满足学生实验的要求。应用面广是指TEC-2既能支持与计算机终端(或PC/XT作为仿真终端)的连接运行,又能在不接任何计算机外围设备的情况下,只用TEC-2机主板上的开关、按键与指示灯等来控制TEC-2机的实验运行。

TEC-2虽然已经是一个相当成熟的实验系统,但还存在一些缺陷:

(一)运算器部件采用四片4位的AM2901芯片串联组成16位芯片,功能不够强大,它只支持8种算术逻辑运算:R+S,S-R,R-S 3种算术运算和R∧S,R∨S,/ R∧S,R?S,/(R?S)5种逻辑运算。并且需要AM2902并行进位链的支持,占据实验线路板的的空间较大。

(二)当今硬件实验的趋势是硬件实验软件化,在硬件实验中采用可编程器件EPROM、FPGA,采用VHDL等语言进行软件模拟与调试,灵活性非常强,并且不易损坏器件,操作简单。TEC-2实验计算机系统支持的实验项目比较齐全,但是灵活性比较差。学生没有机会去独立设计实验计算机系统,不能完成功能部件如控制器的独立设计。实验侧重于了解TEC-2的使用,对计算机系统的整体组成没有掌握。

为了更好的进行计算机组成原理课程的教学,使学生对计算机的组成原理有更深刻的了解,提高实验教学的效果,所以有必要开发新型的实验计算机系统。

1.2 新型16位教学实验计算机系统追求的目标

作为在TEC-2基础上进行改进的新型16位教学实验计算机系统,它具有如下特点: z 完备性

具有完整的指令系统,支持多种I/O接口电路,能够支持现有的所有实验,并开发新的实验。

z 先进性

SRT项目结题报告 运算器芯片采用16位的AM29116芯片,该芯片功能强大,指令系统更加复杂,具有完整的算数运算和逻辑运算功能。

z 灵活性

采用可编程逻辑器件,学生可采用VHDL语言进行编程,经软件模拟测试通过后可以在实验计算机系统上进行检验。如果输入输出的逻辑清晰,学生可以独立进行功能部件的设计,如存储器、中断处理部件等部分的设计。

1.3新型16位教学实验计算机系统的改进之处

作为在TEC-2系统基础上发展起来的新型实验计算机系统,它与TEC-2系统在保证原理基本一致的前提下,在先进性和灵活性方面有了较大的改进,主要是采用了功能更强的芯片和可编程器件。具体表现在:

(一)运算器部分采用了16位的AM29116可编程微处理器,与TEC-2采用的4片4位的2901串联组成16位运算器相比,大大节省了实验电路板的空间。而且AM29116芯片的指令集非常强大的,除了单操作数和双操作数的逻辑和算术指令外,还包含用在控制器应用方面的指令:位设置 、位清除 、位测试、 旋转合并、旋转比较、 循环冗余码校验。

(二)时钟发生电路采用了可编程器件ISP1016,用VHDL语言模拟AM2925的部分功能实现。TEC-2中的启停电路使用了一片GAL20V8外加单稳态电路实现,两者相比,ISP1016的管脚更多,能够实现的功能更强。显然新型教学实验计算机的设计更灵活,更先进,也更节省电路板空间,且给出的时钟信号边沿相当好。

(三)原来TEC-2机的微程序固化在2片ROM中,在加电后再装入由7片LS6116随机读写的存储器芯片组成的56位字长的微程序控制器中。为了简单起见,在本新型教学实验计算机中,直接将微程序烧入8片2816ROM中,从而简化了电路原理图。

(四)TEC-2机上安装有约26个扭子开关、3个按钮微动开关、16个发光二极管,为了实现在不接入计算机终端与PC机的情况下,在手动方式下完成全部的实验项目。但是由实践证明,手动完成实验项目可行性不强,所以在新型教学实验计算机中去掉了这一部分,改用中断处理。另外,将数据显示灯做成附加板,用数据线引出,这样在不增加电路板空间的情况下,大大增加了显示灯的数量,便于测试板的调试和学生实验时的数据测试。

另外,为了方便起见,在本文中,我们将新型16位教学实验计算机简称为新型实验机。

第二章 新型实验机的原理设计与实现

前面已经指出,新型实验机是在TEC-2系统基础上发展起来的,故它的原理和TEC-2

SRT项目结题报告 机基本相同。但作为一代新型实验机,经过一些重要部件的修改,比原来TEC-2机拥有更强大的功能和更灵活的操作。下面将分几节详细介绍新型实验机的硬件各重要部件,包括运算器、控制器及存储器部件的组成与设计原理,尤其对改进的地方作重点介绍。

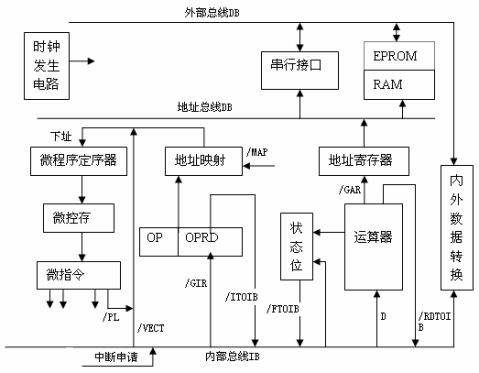

2.1新型实验机的简化逻辑框图

在详细介绍新型实验机的具体组成与运行原理之前,先看一下它的简化逻辑框图,有利于理解系统的整机结构、各功能部件之间的连接关系。

新型实验机的简化逻辑框图如图2.1所示。

图2.1

从简化逻辑框图上可以看出:

新型实验机的主机部分主要有三个重要组成部件:控制器、运算器、主存储器。当然作为一个计算机系统,还应包括输入输出接口设备,但由于新型实验机还处于一个实验开发阶段,重点放在主机部分,输出基本上由指示灯显示,故下面着重讲述主机部分的三大部件的组成及整机的运行原理。

我们知道,要用计算机完成某一运算,或解决某一特定的任务,必须实现编制程序。它告诉计算机需要做哪些事,按什么步骤去做,并提供所要处理的原始数据。一件事往往要分步去做,每一步要求计算机执行的操作命令称为一条指令。

存储器是用于存放程序(指令和数据)的部件,其中包括只读存储器ROM和随机存储器

SRT项目结题报告 RAM,当然计算处理所获得的中间结果与最终结果可作为数据存放到RAM中。在新型实验机中,我们事先将要运行的程序烧入ROM,启动运行后,控制器(包括指令寄存器、地址映射MAPROM、微程序定序器、微控存及流水线寄存器)向存储器送出某个地址码,从指定的存储单元中读取一条指令,送入控制器识别,分析该指令要做什么动作,操作数在何处。根据该指令的含义,控制器发出相应的操作命令,例如将某存储单元中存放的操作数取出,送往运算器进行所指定的运算处理,再将运算结果送回存储器中指定的单元。运算器是根据控制器的命令进行各种运算处理的部件。运算过程中的某些状态信息:如有无进位(C)、结果是否为0(Z)、结果的正负(S)、是否溢出(V)等,可送回控制器作为下一步骤操作的参考依据。

将主机的各大部件连接起来实现信息传送的结构为总线。从逻辑图中我们可以看出,主机内的总线包括数据总线和地址总线两组。

地址总线,其输入信号仅有一组,即来自地址寄存器,而地址寄存器只能接收来自运算器的结果输出信号。它的输出,要送往主存、各外设的入/出接口。地址中的某几位经过译码器产生片选信号,选择相应的存储器和接口。主存和外设可根据送来的地址进行读写操作或读操作。总之,地址总线是CPU向主存、外设接口等传送地址信号的通路。

数据总线,又分为内部数据总线IB与外部数据总线DB,他们之间通过2片8位的双向三态门连接起来。

内部数据总线的信号输入来源有5组:

(1)运算器的16位输出;

(2)外部数据总线传送来的数据;

(3)指令寄存器的低位字节(入/出端口地址或相对寻址的位移量);

(4)处理机状态字(C, Z, V ,S 4个标志位及中断优先级);

(5)中断向量寄存器的16位输出。

这些输入的控制是通过一个3-8译码器给出,译码器的输入控制信号是从微码得到。 内部数据总线的信号将送出到如下部件:

(1)运算器的16位输入;

(2)送往外部数据总线;

(3)送往指令寄存器;

(4)微程序控制器AM2910的10位下地址输入端。

这些输出控制通过开关门实现,具体的在后面介绍各部件时加以说明。

SRT项目结题报告

2.2新型实验机的运算器部件

计算机的基本功能是进行各种运算处理,运算器就是进行各种运算处理的部件。在计算机的组成中,运算器接收来自控制器的控制信号,对送入运算器内部寄存器中的数据进行运算或在内部寄存器之间传送,并把结果保存在内部寄存器中或送到输出寄存器。运算器是新型实验机的主要改进之处,所以有必要对它的结构和工作原理做一个详细的介绍。

新型实验机的运算器主要是由芯片AM29116及其辅助电路组成。下面分节介绍AM29116的内部结构、引脚信号及指令集。

2.2.1 AM29116芯片的内部结构

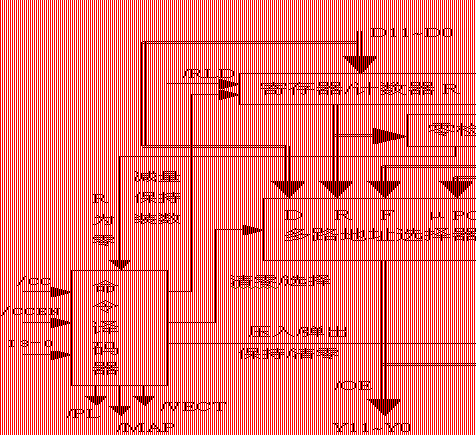

AM29116芯片的原理如下图所示:(图2.2)

图2.2

AM29116是高性能的微可编程的16位双极微处理器,内部各组成通过16位的数据总线连接起来,支持16位或8位的运算。其内部组成包括:

(1)32字×16位RAM,分别用R0-R31表示。其输出端有16bit的锁存器。当CP为高时锁存器透明,当CP为低时,锁存器数据锁存。当CP为低,/IEN输入也为低,并且正在执行的指令的目的地址是RAM时,数据写入RAM。对于Byte指令,只有低8位写入。对于word指令,所有16位都写入。利用外部的多路选择器对指令输入的5个bit进行选择,

在同一指令中能够选择独立的读地址和写地址。对于立即数指令这种双地址操作不允许。

SRT项目结题报告

(2)16位全进位前行ALU。根据正在执行的指令,ALU能够支持单、双和三操作数指令。支持常规的单双操作数操作,如传送、补码、双补码、加、减、AND、NAND、OR、NOR、EXOR、EX-NOR。并且能够执行三操作数指令,例如循环合并、循环比较。支持字和字节的操作,在byte模式下只对低8位进行操作。ALU运算后产生三个状态输出:C(进位),N(负数)和OVR(溢出)。虽然ALU不产生0标志,但是能够检测出byte或者word模式下的0标志。ALU的进位输入可以是0,1或者来自状态寄存器QC,通过进位选择器进行选择。利用QC作为进位使高精度的加减法成为可能。

(3)状态寄存器,它存储8-Bit的状态位。低四位是ALU的状态位:Z、C、N、OVR。高四位包括一个连接位和3个用户定义的状态位(FLAG1,FLAG2,FLAG3)。当/SRE和/IEN同时为低时,低4位在指令结束时状态更新,空操作、保存状态 、测试状态和状态重置、状态置位指令除外。高四位只有在word模式下相应的状态重置、状态置位指令和状态读取指令才进行更新。在移位指令结束后,移入位进行更新。低4位状态字(Z、C、N、OVR)能够通过双向T总线直接读出。当OE为高时,这4位状态字在T1-T4上输出。

(4)条件码产生选择器,包含逻辑线路,对12位条件码测试信号进行处理。 多路选择器可以选择其中一个测试信号,通过CT输出供微程序使用。

(5)三状态输出缓冲

在AM29116芯片中存在两种三态输出缓冲。一种可以控制双向十六位总线。当输入的/OEy置低电平时,输出使能。当/OEy高电平时,Y输出处于高阻态,使数据从外部设备输入到数据锁存器。

另一种可以控制双向四位T总线。当输入的OEt置高电平时,T总线使能,可以允许从外部设置ALU的状态位(Z、C、N、OVR)。OEt为低电平时,T输出为高阻态,外部设备能够驱动T总线为CT的输出选择一个测试条件。

(6)16位数据锁存器,控制AM29116双向Y总线的数据输入。DLE为高时锁存器透明,DLE为低时锁存器锁存。

(7)16位移位寄存器,作为ALU的一个输入。可以对来自RAM、累加器或者数据锁存器的数据移动最多15个位置。在word模式下,对全部16bit进行移位,在byte模式下,只对低8位进行移位。

(8)16位累加器 ,优先编码器 ,指令锁存与译码。

2.2.2 AM29116芯片的引脚信号

AM29116芯片的各管脚定义如下:

Y0-Y15:数据输入/输出。当/OEy为高电平时,Y0-Y15作为外部数据输入,直接写入16位数据锁存器,保持低电平时,ALU数据输出到Y0-Y15。

SRT项目结题报告 I0-I15:16位指令输入。AM29116根据指令进行相应的操作,在立即数指令中也用作数据输入。

T1-T4:输入/输出管脚。受OET控制,当OET为高时,Z、C、N、OVR输出到T1-T4, 可作为外部状态寄存器的输入;OET为低时, T1-T4作为产生CT输出的输入。

CT:条件测试。条件码多路选择器选择12个条件码信号中的一个作为CT的输出。如果CT输出为高,表示条件通过,输出为低,表示条件不通过。

DLE:数据锁存使能端,为低电平时数据锁存,当为高电平时,16位数据锁存器透明。 /Oey:输出使能端(低电平有效)。高电平时,16位Y输出禁止,为高阻态;低电平时,16位Y输出使能。

/IEN: 指令使能端。当/IEN为低时,数据在时钟的低电平时写入RAM,在时钟正向跳变时累加器接收数据。/IEN为低时,状态寄存器在/SRE为低时更新。当/IEN为高时,条件测试输出CT作为指令输入的功能被禁止。在立即数指令的第一个周期的前一半/IEN必须为低。

/SRE: 状态寄存器使能端。当/SRE和/IEN同为低时,状态寄存器在指令结束时更新(NO-OP,保存状态[save status]和测试状态[test status]指令除外)。/SRE或/IEN任何一个为高电平时,状态寄存器内容将保持不变。

OET: 输出使能端,当为低电平时,4位的T输出禁止(高阻态);当为高电平时,4位T输出使能。

CP: 时钟脉冲。时钟为高时,RAM的锁存器透明。时钟为低时,RAM输出锁存。如果IEN为低,并且被执行的指令指定RAM作为操作的目标,在时钟为低期间,数据写入RAM。如果/IEN为低,在时钟的正向跳变时累加器和状态寄存器接收数据。如果在正向跳变期间存在立即数指令模式,指令锁存器透明。

在新型实验机中,以上各管脚信号由微指令给出的控制信号有:/SRT, /INE, DLE, OET, /OEY, I0-I15, T1-T4,根据这些信号的不同编码,可以控制运算器进行各种操作。

2.2.3 新型实验机运算器部件实现中的一些具体问题

新型实验机的运算器主要由AM29116组成,外加一些输入输出的配套线路。在具体实现中,还有一些问题需作一下必要的说明。

(一)32个通用寄存器的功能分配

在新型实验机的具体实现中,把AM29116芯片内的32个通用寄存器R0-R31,分为两组,其中R0-R15作为通用寄存器供用户编程使用,而把R16-R31作为特殊寄存器使用,即用户不能使用,具体分配如下:R16、R18、R19分别作为PC、IP、SP,即程序计数器、指

SRT项目结题报告

令当前地址、堆栈指针;R30、R31分别作为ONE、TEMP,即存放数值为1的寄存器和临时寄存器,其他11个寄存器还未作具体的定义。

(二)运算中具体寄存器的给出

从上面列举的指令格式中,我们可以看出,运算中所用到的寄存器由AM29116的指令输入端I4-I0给出,即指令输入端的低5位输入为00000,即表示对R0进行操作,其他依此类推。在具体实现中,低四位的输入有三个来源:指令中的目的寄存器地址DR、源寄存器SR、微码。具体选哪一个输入,由微码中的SA、SB两位编码定义。具体编码意义将在下面的微码格式中讲解。一般的,当执行用户程序时选用指令给出的寄存器,当要用到特殊寄存器时,选用微码中的I3-I0的编码。

(三)条件测试CT的产生

条件测试CT共有12种可能的测试状态。除了状态寄存器中的8位(QZ,QC,QOVR,QLINK,QFLAG1,QFLAG2,QFLAG3), 四种逻辑功能QN?QOVR,(QN?QOVR)+QZ,QZ+/QC和LOW也有可能被选中。这些功能在测试二进制补码和无符号数算术运算时很有用。通过T 总线的输入或指令中I1-I4的编码,CT不同的输出如下图所示。其中指令中I0-I4比T总线有优先权。

T4 T4 0 0 0 0 0 0 0 0 1 1 1 1

T3 T3 0 0 0 0 1 1 1 1 0 0 0 0

T2 T2 0 0 1 1 0 0 1 1 0 0 1 1

T1 T1 0 1 0 1 0 1 0 1 0 1 0 1

(N?N?OVR Z OVR LOW C Z+/C N LINK Flag1 Flag2 Flag3 CT

在系统的具体实现中,CT的输出将作为外部状态标志位形成的一个输入,这个信号非常有用,尤其是在移位指令中,运算器的最高位、最低位的移入信号都要借助CT的输出。例如,设C=CT(其中C为系统的进位标志位),在执行移位指令时,最高位或最低位移入LINK中,此时只要取CT输出为LINK,即T4-T1的编码为1000,即可实现将最高位或最低位移入C的要求。

SRT项目结题报告

(四)系统状态标志位(C、Z、V、S)的形成

运算器在执行某些指令时,必须把所得结果的特征记在标志位中。哪些指令将影响标志位,影响哪一个或几个标志位,是在确定指令功能和用法时规定的。在新型实验机设计中,出现如下几种影响标志位的情况:

1)不受执行指令的影响;

2)C、Z、V、S按指令执行结果的特征(Am29116芯片内部寄存器的低四位输出CY,Z=0 , OV , S)变化。

3)POPF和IRET都要从堆栈中恢复保存在那里的原标志位的值。即接收从内部总线上送来的值。

4)CLC(清进位标志)指令使C变为0。

5)STC(置进位标志,该指令留待扩展)指令使C变为1。

6)在执行移位指令时,运算器最低位/最高位移出值要移入C标志位,其他标志位不变。 在新型实验机具体实现中,通过控制器的微指令字中的3位微码,来区分上述各种不同的处理。并用一片GAL20V8可编程逻辑器件,实现相应的逻辑处理。

2.2.4 对AM29116的静态和动态测试

静态测试

重点测试AM29116的三态门控制。如果AM29116的三态门控制出错,可能会导致错误的运算结果,甚至损坏器件。

通过开关手动设置AM29116的指令和控制信号,从而测试AM29116的指令系统和控制信号的意义。

测试内容及测试结果见下表。 指令 I15-

I0

Mov 1101

R1,2 1000

1100

0001

Read

R1 11011000

0100

0001 Y15-Y0 DLE OET /Oey1 1 CTT1- T4 /IEN/ SRE0 指令 类型 备 注 00001 000000000010 00001 000000000010 NC 0000 0 Single 先将I拨成相应指令,其他信号设置好,然后/Oey拨为1,按CP Single 先把/Oey拨为0,再输入指令输入,按CP 1 0 NC NC 0 0

SRT项目结题报告

Mov r1,1010 1010 1010 1010

1101NC 100011100001 1010NC 101010101010

1 1 0 NC 0010 0 0 Imme

/IEN保持低,拨指令后按CP,然后拨数据,再按CP

1 1 0 NC 0000 0 0

Add 1101NC r1,r2 1000

00000010

1001 100010000001

MOV 1101NC R1,r2 1001

01100010

1101 100101100001

SHL r1 1100NC

110000000001 RCR r1 1100NC

110011000001 SETST 0111NC

011101000011

1 1 0 NC NC 0 0

Single Acc?R2,

R1+r2?r1

1 1 0 NC Nc

参见0 备注

Double 指令比较复杂,拨好指

令,/IEN=1,按住CP不放,改变DEST Reg,改变/IEN=0,抬起CP

1 1 0 NC NC 0 0

Single 高位放入C不能实现,

可通过先判断N再移位来实现 Single Qlink需置零,否则结

果出错。

1 1 0 NC Nc 0 0

1 1 0 NC 1111 0 0

Single 设置CZVO=1111。在

T4_t1上结果立即显示,但并没有写入Status Reg,要等下一个时钟来临才写入。原因在原理图上很清楚。Single 同上一指令

RSTST 0111NC

010101000011 TEST

01110011

NC

1 1 0 NC 0000 0 0

1 1 0 0 0

Single 根据状态生成CT。如果

状态寄存器

SRT项目结题报告

01000000

ZCNo=0010,,则Ct=1 如指令改为0111001101000100,则CT=0

1

1

NC ND

Single 设置R1的bit 13

为1

0Bitset

1110NC 000110100001

动态测试

重点测试在连续时钟下AM29116的指令系统和时序关系。在EPROM中保存AM29116的指令和控制信号,类似于TEC-2中的微程序控制存储器。在时钟脉冲的作用下,通过EPROM给出AM29116所需的指令和控制信号,从而测试AM29116的指令系统和控制信号的意义。

动态测试与静态测试的目的不同。静态测试的重点在于三态输出缓冲器的控制,侧重于验证指令的正确性。动态测试侧重于测试连续时钟脉冲下的时序关系,在连续时钟脉冲下测试控制信号的配合关系。

在测试过程中,2716中各管脚与AM29116芯片的信号对应关系如下: M1 M2 M3 M4 M5 M6

D7 I0 I8 Y0 Y8 DLE T1

D6 I1 I9 Y1 Y9 OET T2

D5 I2 I10 Y2 Y10 /OEY T3

D4 I3 I11 Y3 Y11 /IEN T4

D3 I4 I12 Y4 Y12 /SRE

D2 I5 I13 Y5 Y13

D1 I6 I14 Y6 Y14

D0 I7 I15 Y7 Y15

测试的指令序列如下所示:

Mov R2,2 Read R2 Mov R1,5 Read R1 Mov R2,9 Read R2 Add R1,R2 Add R1,R2 Read R1 Mov R2,9 Read R2 Shl R2

M1 43 42 83 82 43 42 40 81 82 43 42 40

M2 1b 1b 1b 1b 1b 1b 1b 19 1B 1B 1B 33

M3 40 Ff A0 Ff 90 Ff Ff Ff FF 90 FF FF

M4 00 Ff 00 Ff 00 Ff Ff Ff FF 00 FF FF

M5 E7 C7 E7 C7 E7 C7 C7 C7 C7 E7 C7 C7

M6

FF FF FF FF FF FF FF FF FF FF FF FF

SRT项目结题报告

Read R2 Shl R2 Read R2 R1?5 Read R1 R2?9 Read R2 R2?acc R1?R1+acc Read R1 Shl R1 Read R1 Shl R1 Read R1 R2?acc R1?R1 or acc

Read R1

42 40 42 83 82 43 42 40 81 82 80 82 80 82 40 82 82

1B 33 1B 1B 1B 1B 1B 1B 19 1B 33 1B 33 1B 1B 99 1B

FF FF FF A0 FF 90 FF FF FF FF FF FF FF FF FF FF FF

FF FF FF 00 FF 00 FF FF FF FF FF FF FF FF FF FF FF

C7 C7 C7 E7 C7 E7 C7 C7 C7 C7 C7 C7 C7 C7 C7 C7 C7

FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF FF

以上指令序列均通过测试,未出现异常现象,实验结果正确。

2.3新型实验机的控制器部件

控制器部件是计算机的五大功能部件之一,其作用是向整机每个部件(包括控制器部件本身)提供协同运行所需要的控制信号。计算机的最本质的功能是连续执行指令,而每一条指令往往又要分为几个执行步骤才得以完成。由此又可以说,计算机控制器的基本功能,是依据当前正在执行的指令和它所处的执行步骤,形成并提供处在这一时刻整机各部件要用到的控制信号。

依据前述控制器各组成部分的具体组成与运行原理的不同,通常把控制器区分为微程序的控制器和组合逻辑(硬布线)的控制器两大类。我们的新型实验机采用了微程序的方案,所以下面将重点介绍微程序控制器的基本工作原理及新型实验机的控制器部件组成结构与运行原理。

2.3.1微程序控制器的基本工作原理

微程序控制的概念,最早是由英国剑桥大学的威尔克斯在19xx年提出的。它的基本思想可概括为如下两点:

(1)将控制器所需的微命令,以代码(微码)形式编成微指令,存入一个用ROM构成的控制存储器中。在CPU执行程序时,从控制存储器中取出微指令,其所包含的微命令控制有关操作。

SRT项目结题报告

(2)将各种机器指令的操作分解为若干微操作序列。每条微指令包含的微命令控制,实现一步操作。若干条微指令组成一小段微程序,解释执行一条机器指令。针对整个指令系统的需要,编制出一套完整的微程序,事先存入控制存储器中。

根据以上的思想,微程序控制器的工作原理,是依据读来的机器指令的操作码,找到与之对应的一段微程序的入口地址,并按由指令具体功能所确定的次序,逐条从控制存储器中读出微指令,以"驱动"计算机各功能部件正确运行。

2.3.2 微程序定序器AM2910芯片的组成与功能

在新型实验机中,程序定序器继续采用AM2910芯片。它的核心功能是依据机器的运行状态和当前微指令的有关内容,正确的形成下一条微指令的地址,以保证微程序按照要求的微指令序列关系自动的逐条衔接执行。因为在TEC-2中采用AM2910作为微程序定序器,技术比较成熟,我们的设计在很大程度上参考了TEC-2的设计。下面将简单介绍一下AM2910芯片的组成与功能。

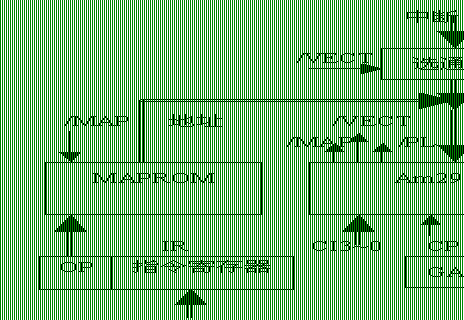

(一)AM2910芯片的内部组成

AM2910芯片的内部组成如图2.3所示。

图2.3

AM2910是一片能提供12位微指令地址的器件,即它的输入输出的地址位数和器件内的部件位数均为12位,能直接寻址4096条微指令字的空间范围。

SRT项目结题报告 从图中我们可以看出,AM2910的内部结构包括几下几个部分:

(1)一个四输入的多路地址选择器。用来从寄存器/计数器(R/C),直接输入(D),微程序计数器(μPC)或微堆栈(F)四个输入中,选择其一作为下一条微指令的地址。

(2)寄存器/计数器(R/C),由12个D触发器组成。当它用作寄存器时,主要用于保存一个微地址,用以实现微程序转移;当它用作计算器时,具有减一功能(何时减一,取决于AM2910的命令码),主要用于控制微程序的循环次数,若装入的 初值为N,则可能执行N+1次循环。

(3)微程序计数器,由12位的增量器和12位的寄存器μPC组成。当增量器的进位输入C1为高时,多路数的输出Y加1后装入μPC(即μPC<-Y+1),用于实现微程序的顺序执行;而当C1为低电平时,多路器的输出Y直接装入μPC(即μPC<-Y),用于实现同一条微指令的多次执行。

(4)微堆栈是由5字×12位的寄存器堆栈和微堆栈指针即μSP组成,主要用于保存微子程序调用识的返回地址和微程序循环的首地址。微堆栈指针μSP总是指向最后一次压入的数据,因此,执行微程序循环时,允许不执行弹出操作而直接访问微堆栈的栈顶。当微堆栈的数据达到5格式,就发出微堆栈已满信号(/FULL=0),这时,任何压入操作都将覆盖掉栈顶的原有数据。

(二)AM2910引脚的定义

输入信号:

D11-D0:外部直接输入的数据,既可以作为寄存器/计数器的初值,也可以经过地址多路选择器直接从Y输出,作为下一条微指令的地址。

I3-I0:AM2910的命令码,来自微指令字的有关字段,用以选择AM2910的16条命令之一。

/CCEN和/CC:共同确定测试条件是否通过,只有当两者均为低时,才表明测试通过。在实验系统中,我们将/CCEN接地,即使其恒为低电平,则可以只使用/CC判断测试结果,/CC为低时测试通过,为高则表明测试失效。

/PLD:寄存器/计数器装入信号,当其为低电平时,不管AM2910所执行的命令和测试条件如何,都强制吧直接输入D11-D0装入AM2910内部的寄存器/计数器。

CI:增量器进位输入,当其为高电平时,控制微指令地址增量,即执行μPC<-Y+1,当为低电平时,执行μPC<-Y。

/OE:Y输出允许信号,低电平有效,当为高电平时,Y输出为高阻态。

CP:时钟脉冲信号,由低变高的上升沿触发所有内部状态的变化。

输出信号:

SRT项目结题报告

Y11-Y0:下一条微指令的地址,它直接被用作读控制存储器的地址。 /FULL:微堆栈满信号,低电平有效。

/PL,/MAP,/VECT:3个使能信号,由于决定直接输入D的来源。

当/PL有效时(即/PL=0),D来源于微指令的下地址字段,由于实现微程序的转移; 当/MAP有效时(即/MAP=0),D来源于MAPROM,用于实现从机器指令的操作码找到相应的微程序段首地址的转移;

当/VECT有效时(即/VECT=0),D来源于中断向量。

这三个信号为互斥关系,由AM2910芯片提供的3个互斥控制信号/MAP、/VECT和/PL加以选通。

(三)AM2910的功能与具体用法

AM2910提供了16条命令,用来控制AM2910内部的操作和选择下一条将要执行的微指令的地址。下表给出了AM2910所完成的功能,这些功能由命令码I3-I0、条件输入/CC、/CCEN以及计数器当前值组合的结果来决定。具体规定见表2.3。

/CCEN

SCI3-0

完成的功能

R/C 内容

R/C 操作

使能 信号

/CC高 Y 输出

0 1 2 3 4 6 8 10 14 15

初始化 条件微转子 指令功能分支 条件转移 入栈R/C装数 转中断向量 R/C非零循环

零

条件返回 顺序执行 三路转移

非零 零

-1

PL PL PL PL

表2.3

注1:/CC为高,R/C保持;/CC为低,R/C装数 注2:R/C操作栏为空,则保持;堆栈栏为空,则保持

/CC低 Y 输出 0 D D D μPC D F μPC F μPC μPC μPC

堆栈 清除 压入 弹出 弹出 弹出

堆栈 清除 压入 弹出

非零

-1 注1

PL PL MAP PL PL VECT PL

0 μPC D μPC μPC μPC F μPC F D

SRT项目结题报告 现将现阶段新型实验机中用到的几条命令的功能和我们的具体用法说明如下:

2号命令:用于指令功能分支,即输出信号/MAP为低,使D输入信号从MAPROM(微地址映射部件)得到,并将其作为输出微地址Y的值,实现用指令操作码找到对应该指令的微程序段的入口地址,从而开始该条指令的执行过程。

3号命令:用于条件微转移控制,当条件成立,即/CC为低时,用/PL把微指令字中的下地址字段的内容(转移地址)经过D输入并送到Y,实现微程序转移。当/CC为高时,微程序顺序执行,即把Y增1后的微指令地址作为下地址。若外部电路确保送入的/CC的状态为低,3号条件微转移也可以用于实现无条件的必定微程序转移来使用。

14号命令:顺序执行,即执行紧跟在本条微指令后面的那条微指令。

2.3.3 新型实验机控制器部件的组成

新型实验机控制器部件的简化逻辑框图,见图

2.4。

图2.4

从图中我们可以看出,控制器部件主要由5部分组成:控制存储器,流水线寄存器PLR,微程序定序器AM2910,微地址映射器MAPROM及指令寄存器。

最核心的部分是控制存储器,用于存放系统的微程序,由64位组成,用8片只读存储器74LS2764实现。在执行微程序时,该控存将依据AM2910提供它的10位地址,读出相应单元的一条微指令。

读出的微指令将通过CP脉冲,打入该控制器的第二个部件--流水线寄存器中。在实验系统的实现中,用7片74LS374和1片74LS273实现。一条微指令的内容通常由下地址和控

SRT项目结题报告 制信号(微命令)两部分组成。下地址是供给控制器部件本身使用的,而微命令又可由若干个小字段组成,提供对计算机其他功能部件,如运算器、主存、输入/输出设备的控制信号。

该控制器的第三个组成部分,是微程序定序器AM2910。在实验系统中,已把AM2910的/OE端接地,使其输出Y11-Y0总保持有效(实际只用了低10位);把/CCEN接地,使AM2910的条件判断结果只取决于/CC;把CI接电源,使微指令地址+1总是执行;

剩下的各部分是与AM2910配套的电路,主要包括地址映射器MAPROM、指令寄存器及/CC信号逻辑值的条件判断电路。MAPROM被用作指令微地址映射部件,它变换指令的操作码位该指令对应的微程序段入口地址,由2片74LS2764 ROM芯片组成,其地址位指令的操作码,对应单元中存放相应微程序段的入口地址,执行读操作,并用/MAP选通读出的信息,解决的是指令功能分支问题。条件码/CC的形成用一片Gal20V8器件实现,通过微指令中的SCC(3位)和SC(1位)两个字段指明的。

2.4 新型实验机的存储器部件

新型实验机的主存储器由2K(字长为16位)的ROM与2K的RAM组成。ROM 由两片2764组成,之所以选用2片,是因为2764的数据是8位的,而新型实验机是个16位的系统。同样,RAM是由两片6116组成。

主存的地址选择来自地址总线AB15-AB0,地址总线的信号是由地址寄存器AR的输出提供的,而AR只接收运算器的输出。主存储器的入\出数据与外部数据总线DB15-DB0接通。外部总线又通过双向三态门电路(LS245与CPU内部总线IB15-IB0连接。在/MIO和/WE两位控制信号的控制下,使内部总线处于逻辑上断开、内向外传送或外向内传送数据的3种状态之一。

内存芯片的片选信号由一片3-8译码器芯片LS138给出(DC1),通过地址的第AB11、AB12、AB13三位给出8个译码信号,选择最大16KW的地址。AB10-0用于选择每片2K内的一个内存单元。

另外,3-8译码器的一个控制端接入的控制信号是/MERQ,即仅在有内存读写请求时才能去选内存,以与外设入/出(用/IOEQ表示)请求相区别。外设接口和内存合用同一地外部数据总线和地址总线。

主存ROM区的读是用相应的ROM片选信号完成的,而RAM区的读写除了用到相应的片选信号,还用读/写控制信号区分读还是写操作,/MMW为低是些,为高是读。

2.5 新型实验机的时钟启停电路

时钟启停电路在整个实验机系统中是一个比较独立的部分,为系统提供时钟信号和其它一些控制信号。同时,由于需要用到一些特殊的时钟信号相配合以实现某些功能,我们所

SRT项目结题报告

设计的启停电路将主要参考Am2925的功能。

2.5.1 Am2925功能简述

Am2925是时钟信号发生器及信号波形控制器(clock generator and microcycle length controller),是实现启停电路的主要元件,同时还能根据不同的输入信号,输出相应的分频信号,以实现一些特殊的控制信号。AM2925各管脚的作用及其工作方式如下: C1,C2,C3,C4:系统时钟输出,由输入L1,L2,L3决定。 L1,L2,L3: 用于控制时钟分频的输入。

/HALT,/RUN: 一对互补输出,提供了/HALT的控制(/RUN=HIGH时停止时钟输出)。 /INIT: 实现系统的初始化,为LOW时,各时钟输出将保持正常输出,此时其它的

控制信号不起作用。

FIRST/(/LAST):在/HALT状态下控制输入,决定输出。为HIGH时,C4=LOW,C1=C2=C3=HIGH;

为LOW时,C1=C2=C3=LOW,C4=HIGH。

SSNC,SSNO: 互补输出,在HALT时,实现单步。 L3 L2 L1 L L L L L H H L H H H H

实现分频 3分频 4分频 5分频 6分频

L3 L2 L1 L H H L H L H H L H L L

实现分频 7分频 8分频 9分频 10分频

2.5.2 利用isp1016实现时钟启停电路

我们用管脚较多的isp1016来实现所需的启停电路。其中主要实现Am2925的时钟信号输出分频控制的功能,以及RESET,STEP等基本功能,以适应实际的需要。

为了更有效率地进行设计和调试,我们采用VHDL语言进行设计,并用软件实现动态输入输出的模拟。设计得到的VHDL源码如下:

Start.vhd

--simulating am2925 and 74ls120 entity Start is port(

c:in bit; --clock in

f:in bit; --mode select (single/continue)

s:in bit; --step

co2:out bit; --systemclock output l1:in bit; --clock cycle length control l2:in bit; --clock cycle length control l3:in bit; --clock cycle length control co1:out bit; --systemclock output

r:in bit; --reset

SRT项目结题报告 co3:out bit; --systemclock output

f0:out bit; --systemclock output rst:out bit --reset signal output );

end Start;

architecture Start of Start is

signal q1:bit:='1'; signal k1:bit:='1'; signal q2:bit:='1'; signal k2:bit:='1'; signal rr:bit:='1'; signal ss:bit:='1';

signal e1:bit:='0'; signal e2:bit:='0'; signal e3:bit:='0'; signal a1:bit:='0'; signal a2:bit:='0'; signal c1:bit:='0'; signal c2:bit:='0'; signal c3:bit:='0'; signal c4:bit:='0';

signal stp:bit:='0'; signal ff0:bit:='0'; begin

rst<= c and q1 ;

q1 <= (k1 and not c) or (q1 and c) ;

k1 <= ((not rr and not r) and c) or (k1 and not

c) ;

rr <= not r and (rr or (not c and k1)) ; stp<= c and q2 ;

q2 <= (k2 and not c) or (q2 and c) ;

k2 <= ((not ss and not s) and c) or (k2 and not c) ;

ss <= not s and (ss or (not c and k2)) ;

co4:out bit; --systemclock output

e1<=not ((c1 and l1) or (not c1 and not e1)); e2<=not ((c1 and l2) or (not c1 and not e2)); e3<=not ((c1 and l3) or (not c1 and not e3));

co1<=c1; co2<=c2; co3<=c3; co4<=c4;

f0<=(not f and c) or (f and stp); ff0<=(not f and c) or (f and stp);

process(ff0) begin if ff0='1' and ff0'event then

c1<=not((not c3 and not c2) and c1 ); c2<=not(((((((not c4 and c3)and e3)and e2)and e1) or (((((not a2 and a1) and c4) and c3) and e3) and e2)) or (((a2 and a1) and not c3) and c2)) or

((not c3 and not c2) and c1));

c3<=not(((((((not c4 and c3) and e3) and e2) and e1) or

(((not a2 and a1) and c4) and c3))

or

(not c3 and c2)) or (not c3 and

c1)); c4<=not((not c3 and not c2) and not c1); a1<=not((((not a2 and c3) and e1) or ((not c4 and c3) and e1)) or

(((not a2 and not a1) and c4)

and c3));

a2<=not(((((not c4 and c3) and e2) or (((a1 and c4) and c3) and e3)) or ((a2 and a1) and c4)) or

(a2 and not c3));

end if;

SRT项目结题报告 end process; end Start;

SRT项目结题报告

2.5.3 动态模拟测试结果

从中可以看出,Am2925的时钟信号输出分频控制的功能,以及RESET,STEP等功能都得到了实现。

2.6 整机原理图和PCB图

以下是我们利用Protel设计得到的整机原理图和PCB图。

SRT项目结题报告

SRT项目结题报告

在PCB版图的绘制过程中,我们并没有像TEC-2和TEC-2000的设计过程一样,利用人工将原理图转化为PCB图,而是利用protel的布线工具自动生成PCB版图。

手动布线有利于充分利用电路板面积,并能满足多种电路性能要求。而且布局美观,可以实现一面水平布线而另一面垂直布线。但是效率低、周期长、容易出错。而且,由于我们都没有这方面的经验,采用手动布线的方法还需要请专业人员来完成,在时间和经费上都有相当大的开销。因此,我们采用了计算机辅助设计,利用protel的布线工具实现了自动布线,避免了手动设计Pcb图的低效性和易错性,做到了一次成功,无飞线改线等情况。

自动布线的最大好处是在整个设计过程中,设计者可以通过CRT显示、观察任意层次版图的局布和全貌。另外,设计者只需完成总体布局的工作,具体走线的工作全部由计算机软件来完成。实际上,计算机辅助设计也体现了当今设计的主流。利用计算机辅助设计,可以降低设计费用和缩短设计周期。

本章小结

至此,我们已经介绍了新型实验计算机硬件组成中主要部件的原理及实现。从计算机组成的角度看,新型实验机具备了一台计算机的所有基本结构,包括核心的控制器部件,执行算术和逻辑运算的运算器部件以及存储器部件,其中主存又分为随机存储器RAM和只读存储器ROM。控制器部件

SRT项目结题报告

的基本功能,是依据当前正在执行的指令和它所处的执行步骤,形成并提供处在这一时刻整机各部件要用到的控制信号;运算器部件的基本功能,是进行各种运算处理;存储器部件的基本功能,是用来存放程序与数据。各部件在电路上的具体实现及其它们如何相互连接成有机的整体等硬件设计上的问题,都可从本章找到答案。

SRT项目结题报告

第三章 新型实验机的调试

前一章介绍了实验计算机硬件的设计。这一部分介绍硬件部分的调试工作。任何一个实验系统在设计的时候都不可能做到天衣无缝,往往要经过几轮调试,更换数版设计版图,不断改进,设计才能够基本满足性能的要求。所以调试也是一个必不可少的非常重要的一个环节。我们这次SRT项目,很大一部分时间都是用在调试改进上面,对设计制出的整个电路板都作了测试和验证,工作量相当大。

硬件电路调试的主要目的是,走通主要的数据通路,包括数据通路,地址通路以及各部件内部通路等,并验证所有三态控制的有效性。

硬件电路的调试主要分两步完成:

(1) 整体性检查。拿到一块刚才厂家出厂的电路板后,在焊器件之前,必须对其进行整体性的检查,因为很多电路问题并不是因为设计上的问题,而是由于生产过程的技术或其他问题而导致的。整体性检查包括:所有导孔是否都通,各焊线之间有没有短路或断路,极性相同的电源线是否都连通,正负级之间有没有短路等。

这个整体性的检查是非常重要的,如果不进行这一步,等焊上器件后,很多电路部分都无法测试到,一旦出现短路或断路现象,严重的会导致所有器件都损坏,轻一点的也将很难查出问题出在哪里,大大影响整个调试进程。

焊接完器件管座后,还要检查一下各管腿是否有虚焊情况,为下一步调试做好充足的准备。

(2)数据链路的调试。这一部分的调试包括AM2910是否能够正确的提供需要执行的微码地址,AM29116内部的32个ROM的运算操作是否正确,主存部分与其它部分是否能协同工作。

调试时各开关的状态为: Continue/Step开关出于低电平,使电路处于单步状态,CP由STEP单脉冲开关送出;每次上电后,按RESET按键,实现系统总清零。

在调试过程中,我们按照指令的功能,编制了两个测试程序,如下所示。

调试程序1(检测数据通路):

0->R0

00:MOV

03:ADD R1, 1 R0, R1 指 令

MOV R1,

ADD R0,R1 1 主存内容 2C,10 00,01 04,01 主存地址 00 01 02

SRT项目结题报告

写入微控存的内容:

00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D

R0+R1->R0 Mov R1,01

微指令 0->R0 0->PC PC->Y Y->AR,PC->ACC ACC->IP PC+1->PC,MEM->IR

/map=0 XXX

PC->Y Y->AR PC+1->PC MEM->R1 R1->ACC R0+ACC->R0

1,2 00 00 00 00 00 00 00 00 00 00 00,40 00 00,40

3 07 07 07 07 07 07 04 07 07 07 0C 07 0C

4 90 90 90 90 90 A0 A0 90 90 90 A0 90 18

5 06 06 06 06 06 06 06 06 06 06 0E 06 06

6 9B 9B 1B 1B 1B BB 1B 1B 1B BB 1B 1B 19

7 00 08 0A 01 89 0E 0A 0A 0A 0E 03 80 01

8 1E 1F FF 13 1F 03 03 1F 13 1F 1E 1C 1E

说明:从上表的微指令一列中可以看到,这段程序的执行,涉及到了AM2910下地址的形成电路、AM29116内部寄存器之间的加法运算、内存的读操作及内部Y总线、地址总线、外部数据总线和内部数据总线之间的数据传送,还涉及到了条件码形成电路、状态寄存器、地址寄存器、指令寄存器等部件的操作。也就是说,调通了这段程序,这个实验板的数据链路出了一些特殊操作(如内存写、条件跳转等)以外,基本已经调试通了。 调试程序2(存储器读/写): 00: MOV 02: MOV 04: MOV 06: MOV 08: MOV 0A: READ 0B: READ 0C: READ

R1, 2

[08FF], R1 R3, [08FF] [08FE], R3 R2, [08FE] R1 R2 R3

//[08FF]=2 //R3=2 //[08FE]=2 //R2=2

SRT项目结题报告

主存地址 00 01 02 03 04 05 06 07 08 09 0A 0B 0C

指 令 Mov R1,02

MOV [08FF],R1

MOV R3,[08FF]

MOV [08FE],R3

MOV R3,[08FF]

READ R1 READ R2 READ R3

主存内容 2C,10 00,02 34,01 08,FF 30,30 08,FF 34,03 08,FE 30,20 08,FE D8,10 D8,20 D8,30

说明:这段程序主要是为了调试内存读写操作,被调试的指令为三条: MOV MOV READ

DR , [ADR] [ADR], DR DR

这个程序通过对RAM中的某一地址进行先写入再读出的操作,反复验证数据能否写入和读出。READ指令是为了将寄存器的内容再次读出,通过实验板上的指示灯看结果是否正确。

在调试过程中,我们发现在保证地址和数据都已经在RAM 6116相应的输入端,写信号及片选信号都已经有效的情况下,仍然不能实现写操作。经过反复的检查和测试,我们才发现在原理图设计的时候,将片选信号端(18管腿)和使能端(20管腿)接反了,这样使6116根本不能正常工作。发现问题之后,解决就比较简单了,只要通过割线、焊线,把两个信号换过来就行了。

本章小结

这一章我们详细介绍了整个实验测试板的调试步骤和内容。硬件电路的调试主要是针对原理图设计部分是否正确合理。结合我们的调试过程,在这一章中,列出了硬件电路的调试步骤,分析了几个主要的调试程序。

SRT项目结题报告

结束语

一学年的SRT项目到此已经结束。我们的设计方案是:控制器用微程序控制器,运算器由微可编程的16位双极微处理器AM29116芯片构成。在设计过程中,我们完成了新型实验机原理图的布线、制版,微程序的设计,EPROM表达式的改写,指令系统的确定及整个电路系统的调试。

在此,首先感谢清华大学计算机系的汤志忠教授、周继群老师和许忠信博士给予我们的种种帮助。特别感谢周继群老师对我们的指导和个方面对我们的帮助,使得我们顺利完成了这个项目。感谢同组同学杜江的合作和帮助。正是在这许多人的帮助下,我们才能顺利完成这个SRT项目。

SRT项目结题报告

参考文献

【1】 王城,周继群,蔡月茹.《计算机组成原理实验指导书与习题集》.

北京:清华大学出版社,1996.

【2】 王城,刘卫东,董长洪.《计算机组成与设计》(下册).北京:清华

大学出版社,2000.

【3】 香港长江贸易公司.《Bipolar Microprocessor Logic and

Interface》.California:Sunnyvale,1983:pp.6-15~6-50.

【4】 陈清山等.《最新世界存储器集成电路大全》.湖南:中南工业大学出

版社,1990:随机存取存储器(RAM),pp①91~95.

【5】 王尔乾,梁鹿亭,刘和益等.《TTL集成电路设计和应用手册》.北京:北京市半导体器件二厂,1982.

【6】 谢淑如,郑光钦,洋渝生.《Protel PCB 99SE 电路板设计》.北京:

清华大学出版社,2001.