实训心得

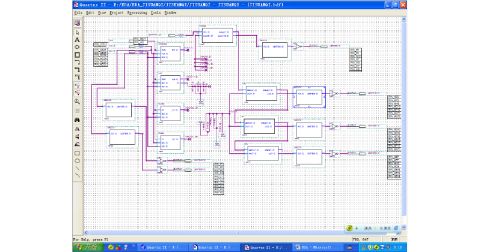

短暂的一周实训已经过去了,对于我来说这一周的实训赋予了我太多实用的东西了,不仅让我更深层次的对课本的理论知识深入了理解,而且还让我对分析事物的逻辑思维能力得到了锻炼,提高了实际动手能力,下面谈一下就这一周实训中我自己的一些心得体会。 一周的实训已经过去了,我们在老师提供的实践平台上通过自己的实践学到了很多课本上学不到的宝贵东西,熟悉了对Quartus Ⅱ软件的一般项目的操作和学到了处理简单问题的基本方法,更重要的是掌握了VHDL语言的基本设计思路和方法,我想这些会对我今后的学习起到很大的助推作用。此外,还要在今后的课本理论知识学习过程中要一步一个脚印的扎实学习,灵活的掌握和运用专业理论知识这样才能在以后出去工作的实践过程中有所成果。

最后还要感谢学校为我们提供这样专业的实践平台还有瓮老师在一周实训以来的不断指导和同学的热情帮助。总的来说,这次实训我收获很大。

同时,感谢大专两年来所有的老师,是你们为我解惑受业,不仅教授我专业知识,更教会我做人的道理。

这次EDA实训让我感觉收获颇多,在这一周的实训中我们不仅巩固了以前学过的知识,而且还学到了怎样运用EDA设计三种波形的整个过程和思路,更加强了我们动手能力,同时也提高了我们的思考能力的锻炼,我们在写程序的同时还要学会要改程序,根据错误的地方去修改程序。

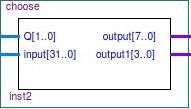

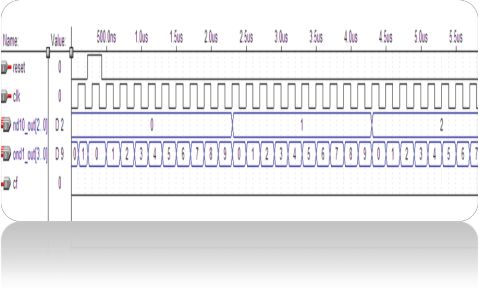

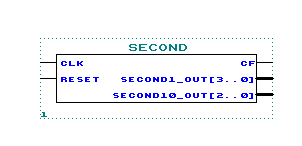

本文基于Verilog HDL的乒乓球游戏机设计,利用Verilog HDL语言编写程序实现其波形数据功能在分析了CPLD技术的基础上,利用CPLD开发工具对电路进行了设计和仿真,从分离器件到系统的分布,每一步都经过严格的波形仿真,以确保功能正常。

从整体上看来,实训课题的内容实现的功能都能实现,但也存在着不足和需要进一步改进的地方,

为我今后的学习和工作奠下了坚实的基础。通过此次的实训课题,掌握了制作乒乓球游戏机技术的原理及设计要领,学习并掌握了可编程逻辑电路的设计,掌握了软件、CPLD元件的应用,受益匪浅, 非常感谢瓮老师这一学期来的指导与教诲,感谢老师在学习上给予的指导,老师平常的工作也很忙,但是在我们学习的过程中,重来没有耽搁过,我们遇到问题问他,他重来都是很有耐心,不管问的学生有多少,他都细心的为每个学生讲解,学生们遇到的不能解决的,他都配合同学极力解决。最后祝愿瓮老师身体健康,全家幸福。

…… …… 余下全文