EDA实习报告 学院:电气信息工程学院专业:电子信息工程班级:姓名:学号:

1

实习目的及要求::

1、熟悉QuartusII软件的相关操作,掌握数字电路设计的基本流程。

2、介绍QuartusII的软件,掌握基本的设计思路,软件环境参数配置,仿真,管脚分配,下载等基本操作。

3、了解VHDL或原理图设计方法与定制IP模块的思想。

4、掌握并行加法器,减法器乘法器以及除法器的设计思路及工作原理。

5、设计一个能完成加减乘除功能并以十进制显示结果的简单计算器。 软硬件资源

硬件:ED2-70实验板

软件环境:QII9.0开发系统

题目设计:这个简单的计算器要求能够进行简单的四则运算,在程序设计中,通过设计、编制、调试一个模拟计算器的程序,加深对我们对编程语句及语义分析和理解,并实现对命令语句的灵活应用。这次实验目的就是实现简单计算器的功能。

二、流程图

? 当输入为00时输出加法结果

? 当输入为01时输出减法结果

? 当输入为10时输出乘法结果

? 当输入为11时输出除法结果

2

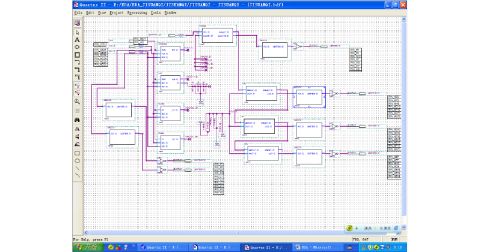

三.顶层原理图

四个模块输出均为十六进制数,为了输出方便观察,设计了8位除法器,将输出变为十进制数显示在数码管上。

DATAIN[1..0]为输入控制端,通过试验箱上两个拨码开关控制输入。A[3..0]和B[3..0]是两个四位二进制输入数,当DATAIN为00时进行加法运算,当DATAIN为01时进行减法运算,当DATA为10时进行乘法运算,当DATA为11是进行除法运算。结果用十进制显示三个共阳静态LED数码管上,除法的余数单独显示在右下角的七段驱动共阳数码管中的一个上。

3

四、各个模块

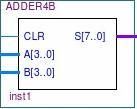

(1)加法器模块

1、封装元件

当CLR为‘1’时清零,输出为零

当CLR为‘0’时,输入两个四位二进制数,输出两个数之和,S[3..0]为和,S[4]为进位。

2、加法器程序

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity choose is

port(Q:in std_logic_vector(1 downto 0);

input: in std_logic_vector(31 downto 0);

output:out std_logic_vector(7 downto 0);

output1:out std_logic_vector(3 downto 0));

end choose;

architecture one of choose is

begin

process(Q)

begin

if Q="00" then output(7 downto 0)<=input(7 downto 0);

elsif Q="01" then

if input(12)='0' then output(7 downto 0)<=input(15 downto 8); else

if input(11 downto 8)="0000" then

output(7 downto 0)<="0000"&input(11 downto 8)+"01100100";

else output(7 downto 0)<="00010001"+not("0000"&input(11 downto

8))+"01100100";

end if;

4

end if;

elsif Q="10" then output(7 downto 0)<=input(23 downto 16);

elsif Q="11" then output(7 downto 0)<="0000"&input(31 downto 28); output1<=input(27 downto 24);

end if;

end process;

end one;

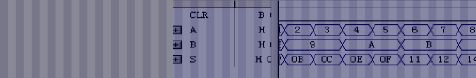

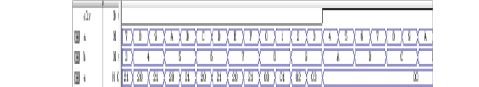

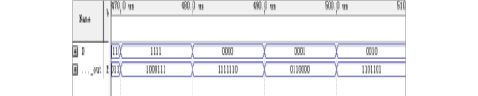

3、仿真结果

当CLR为1时,输出为0;当CLR为0时,进行加法运算。S[3..0]为相加后得到的和,S[7..4]为相加后的进位。

(2)减法器模块

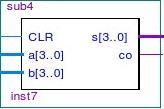

1、封装元件

2、减法器程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY ADDER4B IS

PORT(

CLR:IN STD_LOGIC;

A,B:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

S:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END ADDER4B;

5

ARCHITECTURE behave OF ADDER4B IS

SIGNAL SINT,AA,BB:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

process(CLR)

begin

if CLR='1' then AA<="00000000"; BB<="00000000";

else

AA<="0000"&A;

BB<="0000"&B;

end if;

end process;

SINT<=AA+BB;

S<=SINT;

end behave;

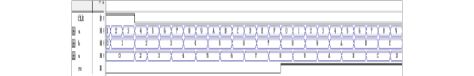

3、仿真结果

CLR为清零,当CLR为1时清零,输出为0;当CLR为0时进行减法运算,a、b为两个四位二进制输入,s为输出,当co为0时,代表s为正,当co为1时代表co为负,当被减数小于减数时,s为相减得到的结果的补码。

从左到右,前三个数码管用十进制显示结果:第一个代表正负,为0时代表正,为1时代表负。第五个为减数,第六个为被减数。

6

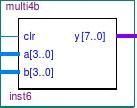

(3)乘法器模块

1、封装元件

当clr为‘1’时输出为0

当clr为‘0’时,a与b相乘输出y

2、乘法器的设计思想

用并行相乘的方法。通过开关和键盘,两组分别输入4bit的数据进行乘法运算时,先求出部分积,即求得二进制数据的乘数和被乘数逐位相乘,之后运用二进制加法进行加和。举例如下,10X9=90:

? --10 × 9 = 90

? -- 1 0 1 0

? -- X 1 0 0 1 =

? -- -------------

? -- 00001010

? -- 00000000 --部分积

? -- 00000000

? - 01010000

? ----------------------------

? -- 1011010 =90

? 这里加法的结果就是所求结果。

3、乘法器程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY sub4 IS

PORT(CLR:IN STD_LOGIC;

a:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

b:IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

7

co:OUT STD_LOGIC);

end sub4;

architecture behave of sub4 is

component ADD is

port(CLR:IN STD_LOGIC;

A:IN STD_LOGIC_VECTOR(3 DOWNTO 0); B:IN STD_LOGIC_VECTOR(3 DOWNTO 0); S:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); COUT:OUT STD_LOGIC);

end component;

signal c,cl:std_logic;

signal bb:std_logic_vector(3 downto 0);

signal ss:std_logic_vector(3 downto 0);

begin

process(CLR)

BEGIN

IF CLR='1'THEN

c<='1';

else c<='0';

end if;

end process;

bb(3 downto 0)<=not b(3 downto 0);

u:ADD PORT MAP(A=>a,B=>bb,CLR=>c,S=>ss,COUT=>cl);

process(c)

begin

if c='1' then s<="0000";co<='0';

else s<=ss+'1';co<=not cl;

end if;

end process;

end behave;

8

4、仿真结果

clr为清零,当clr为1时进行乘法运算,a、b为两个四位二进制输入,y为十六进制输出。

(4)除法器模块

1、封装元件

当clr为‘1’时,输出为0。当clr为‘0’时,a与b相除输出s,s高四位为商,低四位为余

2、除法器设计思想

?

?

?

?

?

?

?

?

3、除法器程序

library ieee;

use ieee.std_logic_1164.all;

9

f:=a; g:=b; e:=(others=>‘0’);--f等于被除数,g等于除数 for i in 1 to 15 loop --e为商 if (f>=g) then f:=f-g; e:=e+1; else exit; end if; end loop; s(7 downto 4)<=e;s(3 downto 0)<=f; 利用循环的思想设计除法器。S高四位为商,第四位为余数

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity multi4b is

port(clr:in std_logic;

a:in std_logic_vector (3 downto 0);

b:in std_logic_vector(3 downto 0);

y:out std_logic_vector(7 downto 0));

end multi4b;

architecture multi_arch of multi4b is

signal d0:std_logic_vector(3 downto 0);

signal d1:std_logic_vector(3 downto 0);

signal d2:std_logic_vector(3 downto 0);

signal d3:std_logic_vector(3 downto 0);

begin

process(clr,a,b)

begin

if clr='1' then y<="00000000";

else

if b(0)='0' then d0<="0000"; else d0<=a; end if;

if b(1)='0' then d1<="0000"; else d1<=a; end if;

if b(2)='0' then d2<="0000"; else d2<=a; end if;

if b(3)='0' then d3<="0000"; else d3<=a; end if;

y<=("0000"&d0)+("000"&d1&"0")+("00"&d2&"00")+("0"&d3&"000");

end if;

end process;

end multi_arch;

4、仿真结果

当clr=‘1’时清零,当clr=‘0’时进行除法运算。

a、b为四位二进制数,a为被除数,b为除数,s高四位为商,s低四位为余数。

10

(5)8位除法器

1、封装元件

作用:用于把十六进制显示的输出换成十进制显示。

方法:被除数除以10时,余数为个位;得到的商除以10,得到的余数为十位;得到的商再除以10,得到的余数为百位。

8位除法器程序

ibrary ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity Div is

port(

beichu,chu:in std_logic_vector(7 downto 0);

shang:out std_logic_vector(7 downto 0);

yu:out std_logic_vector(3 downto 0));

end Div;

architecture one of Div is

signal yushu:std_logic_vector(14 downto 0);

signal remain0,remain1,remain2,remain3,remain4,remain5,remain6,

remain7:std_logic_vector(14 downto 0);

signal diver0,diver1,diver2,diver3,diver4,diver5,diver6,

diver7:std_logic_vector(14 downto 0);

begin

process (beichu,chu)

begin

remain7 <="0000000"& beichu;

diver7 <= chu &"0000000";

if remain7 >= diver7 then

shang(7) <= '1';

remain6 <=remain7-diver7;

else

11

shang(7) <= '0';

remain6 <= remain7; end if;

diver6 <="0"& chu &"000000"; if remain6 >= diver6 then shang(6) <= '1';

remain5 <= remain6 - diver6; else

shang(6) <= '0';

remain5 <= remain6; end if;

diver5 <= "00"& chu &"00000"; if remain5 >= diver5 then shang(5) <='1';

remain4 <= remain5 - diver5; else

shang(5) <= '0';

remain4 <= remain5; end if;

diver4 <= "000"& chu &"0000"; if remain4 >= diver4 then shang(4) <= '1';

remain3 <= remain4 - diver4; else

shang(4) <= '0';

remain3 <= remain4; end if;

diver3 <= "0000"& chu &"000"; if remain3 >= diver3 then shang(3) <= '1';

remain2 <= remain3 - diver3; else

shang(3) <= '0';

remain2 <= remain3; end if;

diver2 <= "00000"& chu &"00"; if remain2 >= diver2 then shang(2) <= '1';

remain1 <= remain2 - diver2; else

12

shang(2) <= '0';

remain1 <= remain2; end if;

diver1 <= "000000"& chu &"0"; if remain1 >= diver1 then shang(1) <= '1';

remain0 <= remain1 - diver1; else

shang(1) <= '0';

remain0 <= remain1; end if;

diver0 <= "0000000"& chu; if remain0 >= diver0 then shang(0) <= '1';

yushu <= remain0 - diver0; yu<=yushu(3 downto 0); else

shang(0) <= '0';

yushu <= remain0;

yu<=yushu(3 downto 0); end if;

end process;

end one;

4、仿真结果

13

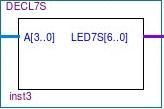

(6)数码管七段译码电路

1、封装元件

3、七段译码器程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DECL7S IS

PORT ( A:IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S:OUT STD_LOGIC_VECTOR(6 DOWNTO 0)); END;

ARCHITECTURE one OF DECL7S IS

BEGIN

PROCESS(A) BEGIN

CASE A IS

WHEN "0000" => LED7S <= "0111111";

WHEN "0001" => LED7S <= "0000110"; WHEN "0010" => LED7S <= "1011011"; WHEN "0011" => LED7S <= "1001111"; WHEN "0100" => LED7S <= "1100110"; WHEN "0101" => LED7S <= "1101101"; WHEN "0110" => LED7S <= "1111101"; WHEN "0111" => LED7S <= "0000111"; WHEN "1000" => LED7S <= "1111111"; WHEN "1001" => LED7S <= "1101111"; WHEN "1010" => LED7S <= "1110111"; WHEN "1011" => LED7S <= "1111100"; WHEN "1100" => LED7S <= "0111001"; WHEN "1101" => LED7S <= "1011110"; WHEN "1110" => LED7S <= "1111001"; WHEN "1111" => LED7S <= "1110001"; WHEN OTHERS => NULL;

END CASE;

END PROCESS;

14

END;

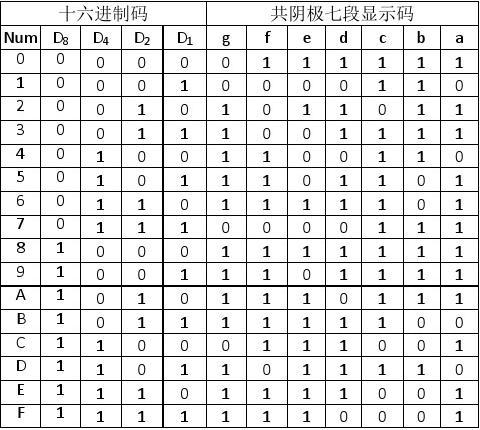

2、共阴极七段显示码十六进制转换表

仿真结果

15

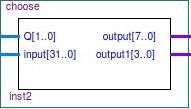

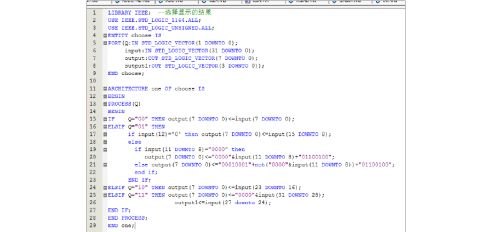

(7)选择模块

1、封装元件 ?

?

?

?

当Q为“00”时进行加法运算 当Q为“01”时进行减法运算 当Q为“10”时进行乘法运算 当Q为“11”时进行除法运算

2、程序

16

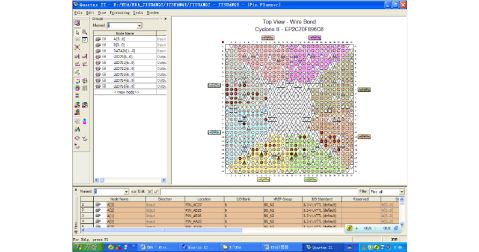

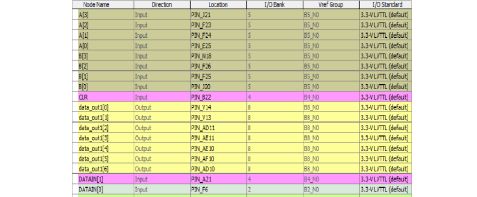

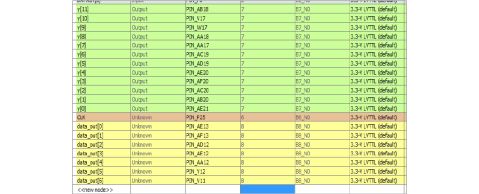

五、管脚锁定

17

六、实习心得

这周的实习已经过去了,我们在老师提供的实践平台上通过自己的实践学到了很多课本上学不到的宝贵东西,熟悉了对Quartus Ⅱ软件的一般项目的操作和学到了处理简单问题的基本方法,更重要的是 掌握了VHDL语言的基本设计思路和方法,我想这些会对我今后的学习起到很大的助推作用。此外,还要在今后的课本理论知识学习过程中要一步一个脚印的扎实学习,灵活的掌握和运用专业理论知识这样才能在以后出去工作的实践过程中有所成果。最后还要感谢学校为我们提供这样专业的实践平台还有实训老师在着周实习以来的不断指导和同学的热情帮助。总的来说,这次实习我收获很大。也能较好的完成这次实习任务,把计算器的仿真及编译还有下载完成。

首先,通过对这门课程相关理论的学习,我掌握EDA的一些基本的的知识,现代电子产品的性能越来越高,复杂度越来越大,更新步伐也越来越快。实现这种进步的主要原因就是微电子技术和电子技术的发展。前者以微细加工技术为代表,目前已进入超深亚微米阶段,可以在几平方厘米的芯片上集成几千万个晶体管;后者的核心就是电子设计自动化EDA(lectronic Design Automatic)技术。EDA是指以计算机为工作平台,融合了应用电子技术、计算机技术、智能化技术的最新成果而开发出的电子CAD通用软件包,它根据硬件描述语言HDL完成的设计文件,自动完成逻辑编译、化简、分割、综合、优化、布局布线及仿真,直至完成对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。其次,通过对课程的实验的学习,我对EDA的学习和理解有了更深刻的认识和体会。我们团队共四个人,做的是两层电梯控制器,作为这个实验的一员与负责人,我感到很有压力。因为只对课本知识的学习,我对实验做成功的把握不是很大,因此只能对数字逻辑与数字电路有初步的了解,而EDA是在数字电路发展到一定阶段的产物,因此学习起来也很费力。然而,在我们团队的共同努力下,我们最终成功地完成了这个实验,包括时序仿真和

硬件测试仿真,都取得了较好地效果。

18