数字系统设计综合实验报告

实验名称:1、加法器设计

2、编码器设计

3、译码器设计

4、数据选择器设计

…… …… 余下全文

数字系统设计实验报告

班级:计算机

姓名:

学号:

计数器设计实验

1、实验目的

1)学习计数器不同设计方法。

2)学习掌握VHDL中不同输出类型在具体应用时的区别(OUT、INOUT、BUFFER)。

3)学习掌握时序电路仿真方法。

2、实验内容

1)采用VHDL设计方法,设计一个60进制计数器,采用BCD码输出。

2)给出上述设计的仿真结果。

3、实验设备

1)清华同方PⅣ 2.4G\256M60G

2)ISE 6.2i—Windows软件系统

4、实验步骤

1)创建工程

2)程序输入

3)仿真

5、实验程序

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY cm IS

PORT(ai,bi,cin:IN STD_LOGIC;

si,cio: OUT STD_LOGIC);

END cm;

ARCHITECTURE Behavioral OF cm IS

…… …… 余下全文

PLD与数字系统设计实验报告

A组实验四:数字密码锁

使用Xilinx公司的Spartan3S 400AN开发板上的相关模块,利用ISE开发软件完成数字密码锁的设计,要求实现如下功能:

利用实验板上的4×3小键盘,设计4位密码锁,当输入密码正确时,在液晶屏上显示“OK”,否则,显示“ERROR”,在输入过程中,显示输入的数据个数,当有错误的输入时,显示“ERROR”,当全部输入正确时,才显示OK。

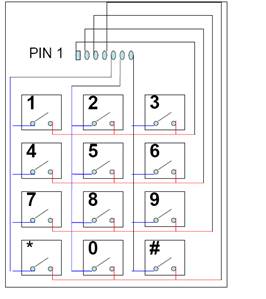

数字键盘又叫行列式键盘。用带IO口的线组成行列结构,按键设置在行列的交点上。例如用4×3的行列式结构可以构成12个键的键盘。实验中所用到的数字键盘原理如图1所示。

图1 4×3数字键盘

例如设置此模块的列为输入端口,行为输出端口。那么在按下某一个键时,该键所在的开关接通,由输入端口向输出端口输出一个有效电平,继而触发其他模块。

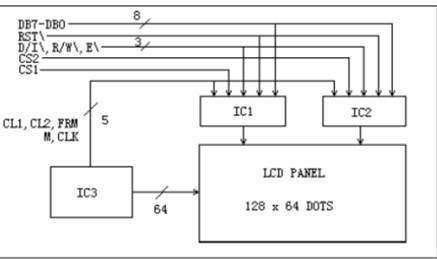

开发板上使用的是无字库的12864LCD显示器,12864LCD显示模块是由128*64个液晶显示点组成的一个128列*64行的阵列。每个显示点对应一位二进制数,1表示亮,0表示灭(但实验所用开发板上该模块实际是低电平表示亮、高电平表示灭)。存储这些点阵信息的RAM称为显示数据存储器。以下是关于显示屏的一些参数:

图2 128*64 LCD控制器结构框图

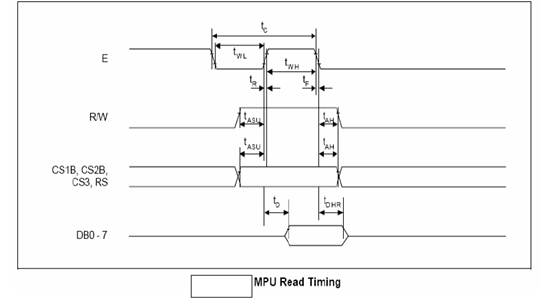

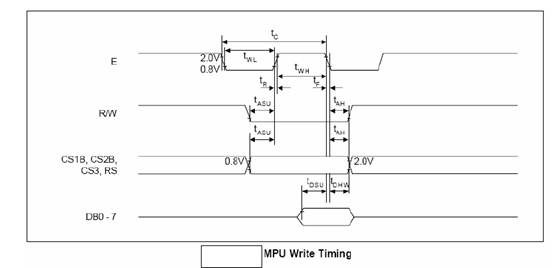

图3 128*64时序图

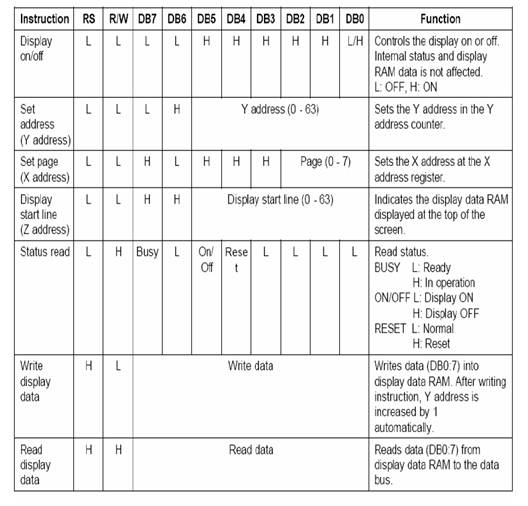

图4 指令功能表

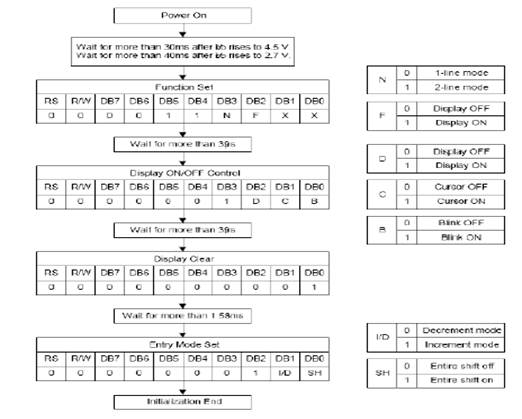

图5 初始化指令流程

要显示某个图形就是将相应的点阵信息写入到相应的存储单元中。图形的点阵信息可以由自己设计也可借助字模软件,问题的关键就是显示点在液晶屏上的位置(行和列)与其在存储器中的地址之间的关系。

…… …… 余下全文

《数字系统设计与Verilog HDL》

实验报告(一)

班级:自动1003班

姓名: 刘洋

学号: 06101103

实验一、ModelSim认识及四位比较器

一、 实验目的

1、了解及掌握ModelSim软件的基本功能;

2、通过ModelSim软件编写基本的程序进行仿真和调试。

二、 实验内容

1、熟悉ModelSim软件中各部分的功能及用法;

2、编写一个四位比较器设计程序以及测试该模块的测试程序,要求如下:

(1)输入两个四位二进制数a、b;

(2)若a<b,则输出LA_out=0,EQ_out=0,LE_out=1;

若a=b,则输出LA_out=0,EQ_out=1,LE_out=0;

若a>b,则输出LA_out=1,EQ_out=0,LE_out=0;

三、 实验步骤及源程序

新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:

module compare4(LA_out,EQ_out,LE_out,a,b,LA_in,EQ_in,LE_in);

output LA_out,EQ_out,LE_out;

input [3:0] a,b;

input LA_in,EQ_in,LE_in;

reg LA_out,EQ_out,LE_out;

…… …… 余下全文

数字电路设计实验报告

引言

本课程是面向智能车制作的课程,但是主要讲述的是一些关于智能车制作的一些最基本的基础知识。比如说一些单片机的知识和一些相应数字电路的知识。故我在这里利用一些所学的知识来设计一个数字时钟。该电路系统由秒信号发生器、“时、分、秒”计数器、显示器组成。秒信号产生器是整个系统的时基信号,它直接决定计时系统的精度,这里用多谐振荡器来实现。将标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。“分计数器”也采用60进制计数器,每累计60分钟,发出一个“时脉冲”信号,该信号将被送到“时计数器”。“时计数器”采用24进制计时器,可实现对一天24小时的累计。译码显示电路将“时”、“分”、“秒”计数器的输出状态送到七段显示译码器进行译码,通过六个七段数码管显示出来。

本作品的主要设计目的是熟练使用555定时器构成多谐振荡器的方法,掌握使用74LS160构成60进制计数器的方法以及使用74LS160构成24进制计数器的方法,理解在实际的设计电路中电压电流关系对整个电路功能的实现所具有的重要性。

关键词:数字电子钟;555定时器;60进制计数器;24进制计数器;共阳极七段数码管;74LS47译码器;

第一章:设计方案的选择

数字电子技术的复杂性和灵活性决定了数字电子钟的设计方案有多种,以下是本设计的方案选择。

1、信号源的选择

多谐振荡器,信号发生器,脉冲芯片以及石英晶体振荡器等方式都可以作为脉冲信号源,但是石英晶振产生的频率较高,需要用到分频器来对它进行分频处理,故在此我选择的是用555定时器制作的多谐振荡器,主要考虑的是它的易于制作和很好的稳定性。

…… …… 余下全文

《数字系统设计与Verilog HDL》

实验报告(五)

班级:自动1003班

姓名: 刘洋

学号: 06101103

实验五、自动售饮料机系统设计

一、 实验目的

1、了解及掌握状态机的基本构成用法;

2、通过ModelSim软件编写程序,用状态机可以编程设计简单的自动控制系统。

二、 实验内容

设计一个自动售饮料机。假定每瓶饮料售价为2.5元,可使用两种硬币,即5角和1元,机器有找零功能。

机器设计有2个投币孔,可用2个按键来代替。还设有2个输出孔,分别输出饮料和找零,提示用户取走饮料和零钱。

三、 实验步骤及源程序

新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:

module sell(yi_yuan,wu_jiao, get,half_out,sell_out,reset,clk);

parameter idle=0, half=1, one=2,two=3,three=4;

input yi_yuan,wu_jiao,reset,clk;

output get,half_out,sell_out;

reg get,half_out,sell_out;

reg[2:0] s;

always @(posedge clk)

begin

if(reset)

begin

…… …… 余下全文