数字系统设计实验报告

班级:计算机

姓名:

学号:

计数器设计实验

1、实验目的

1)学习计数器不同设计方法。

2)学习掌握VHDL中不同输出类型在具体应用时的区别(OUT、INOUT、BUFFER)。

3)学习掌握时序电路仿真方法。

2、实验内容

1)采用VHDL设计方法,设计一个60进制计数器,采用BCD码输出。

2)给出上述设计的仿真结果。

3、实验设备

1)清华同方PⅣ 2.4G\256M60G

2)ISE 6.2i—Windows软件系统

4、实验步骤

1)创建工程

2)程序输入

3)仿真

5、实验程序

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY cm IS

PORT(ai,bi,cin:IN STD_LOGIC;

si,cio: OUT STD_LOGIC);

END cm;

ARCHITECTURE Behavioral OF cm IS

BEGIN

si<=(ai xor bi)xor cin;

cio<=(ai and bi)or(cin and ai)or(cin and bi);

END Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity mn is

PORT(a,b:IN STD_LOGIC_VECTOR(3 downto 0);

ci:IN STD_LOGIC;

co:OUT STD_LOGIC;

s:OUT STD_LOGIC_VECTOR(3 downto 0));

END mn;

architecture Behavioral of mn is

component cm

PORT(ai,bi,cin:IN STD_LOGIC;

si,cio:OUT STD_LOGIC);

END component;

signal carry:STD_LOGIC_VECTOR(4 downto 0);

begin

carry(0)<=ci;

co<=carry(4);

add1: cm port map(a(0),b(0),carry(0),s(0),carry(1));

add2: cm port map(a(1),b(1),carry(1),s(1),carry(2));

add3: cm port map(a(2),b(2),carry(2),s(2),carry(3));

add4: cm port map(a(3),b(3),carry(3),s(3),carry(4));

end Behavioral;

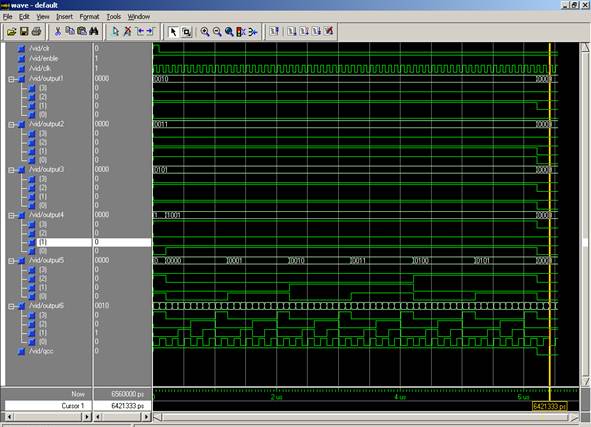

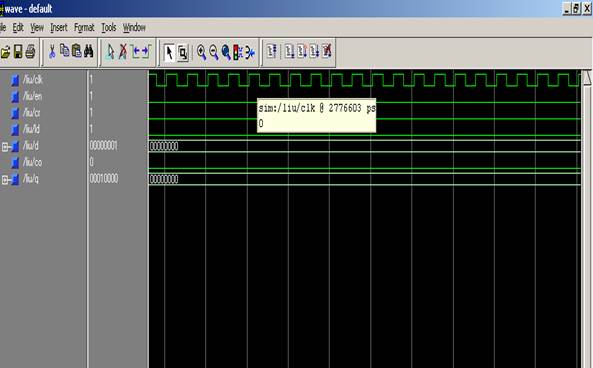

6、实验仿真结果

实验二、加法器设计实验

1、实验目的

1)学习了解加法器工作原理。

2)学习用VHDL语言设计全加器的设计方法。

3)学习使用元件例化的方法设计多位加法器。

2、实验原理

两个n位二进制数相加的过程,是从最低有效位开始相加,形成和数并传送进位最后得到结果。最低位只有加数和被加数相加,这种两个一位数相加称为半加;完成加数、被加数、低位的进位数三个一位数相加称为全加。实现半加运算的电路称为半加器,实现全加运算的电路称为全加器。

3、实验内容

1)用VHDL语言设计全加器。

2)用元件例化方法设计一个四位二进制加法器。

4、实验设备

1)清华同方PⅣ 2.4G\256M60G

2)ISE 6.2i—Windows软件系统

5、实验步骤

1)创建工程

2)程序输入

3)仿真

6. 实验程序

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity fulladder is

PORT(ai,bi,cin:IN STD_LOGIC;

si,cio:OUT STD_LOGIC);

end fulladder;

architecture behavioral of fulladder is

begin

si<=(ai xor bi) xor cin;

cio<=(ai and bi)or(ai and cin) or(bi and cin);

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity four is

Port ( a,b : in std_logic_vector(3 downto 0);

ci : in std_logic;

co : out std_logic;

s : out std_logic_vector(3 downto 0));

end four;

architecture Behavioral of four is

component fulladder

PORT(ai,bi,cin:IN STD_LOGIC;

si,cio:OUT STD_LOGIC);

end component;

signal carry:STD_LOGIC_VECTOR(4 downto 0);

begin

carry(0)<=ci;

co<=carry(4);

gen:for i in 0 to 3 generate

add:fulladder PORT map(

ai=>a(i),

bi=>b(i),

cin=>carry(i),

si=>s(i),

cio=>carry(i+1)

);

end generate gen;

end Behavioral;

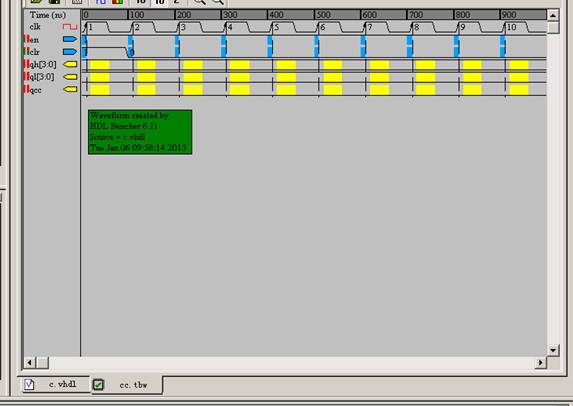

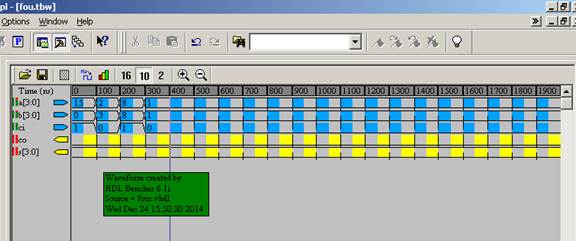

7.仿真结果

数字系统设计第三次实验

简易数字钟设计实验

1、实验目的

1)学习VHDL语言源程序输入方法。

2)学习使用元件例化的方法设计简易数字钟。

3)进一步加深对仿真过程和仿真结果的理解。

2、实验原理

数字钟是对输入时基秒脉冲进行计数,依次输出秒数值、分数值、小时数值,从而确定时钟时间。

3、实验内容

1)建立一个新的 工程。

2)在上述工程中,采用VHDL语言的方 法设计上述简易数字钟。

3) 通过仿真来验证设计结果。

4、实验设备

1)清华同方PⅣ 2.4G\256M60G

2)ISE 6.2i—Windows软件系统

3)多功能EDA实验系统(V型)

5、实验报告要求

1)实验目的、实验内容、实验设备、实验步骤。

2)写出设计程序。

3)画出简易数字钟的仿真波形。

6源程序:

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity counter24 is

Port ( en,clk,temp : in std_logic;

qh,ql : out std_logic_vector(3 downto 0);

qcc : out std_logic);

end counter24;

architecture Behavioral of counter24 is

signal temp_h:std_logic_vector(3 downto 0) := "0010";

signal temp_l:std_logic_vector(3 downto 0) := "0011";

begin

process(en,clk)

begin

if clk='1'and clk'event then

if en = '1' and temp='1'then

if temp_l="0011"and temp_h = "0010" then

temp_l <= "0000";

temp_h <= "0000";

else

if temp_l="1001" then

temp_l <= "0000";

temp_h <= temp_h + '1';

else

temp_l <= temp_l + '1';

end if;

end if;

end if;

end if;

end process;

qh <= temp_h;

ql <= temp_l;

qcc <= (not temp_l(3)) and (not temp_l(2)) and temp_l(1) and temp_l(0) and (not temp_h(3)) and (not temp_h(2)) and temp_h(1) and (not temp_h(0));

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity counter60 is

Port ( clk, en,clr : IN STD_LOGIC;

qh,ql : OUT STD_LOGIC_VECTOR (3 downto 0);

qcc: OUT std_logic);

end counter60;

architecture Behavioral of counter60 is

signal qccl: STD_LOGIC;

signal qtempl:STD_LOGIC_VECTOR (3 downto 0) ;

signal qtemph:STD_LOGIC_VECTOR (3 downto 0) ;

BEGIN

ql<=qtempl;

qccl<=qtempl(3) and not qtempl(2) and not qtempl(1) and qtempl(0) ;

qh<=qtemph;

qcc<=(not qtemph(3)) and qtemph(2) and (not qtemph(1)) and qtemph(0) and qtempl(3) and not qtempl(2) and not qtempl(1) and qtempl(0);

P1:PROCESS(clk,en,clr)

BEGIN

IF clr='1' THEN

qtempl<="1000";

ELSE

IF clk'event and clk='1' THEN

IF en='1' THEN

IF qtempl="1001" THEN

qtempl<="0000";

ELSE

qtempl<=qtempl+'1';

END IF;

END IF;

END IF;

END IF;

END PROCESS P1;

P2:PROCESS(clk,clr)

BEGIN

IF clr='1' THEN

qtemph<="0101";

ELSE

IF clk'event and clk='1' THEN

IF qccl='1'and en = '1' THEN

IF qtemph="0101" THEN

qtemph<="0000";

ELSE

qtemph<=qtemph+'1';

END IF;

END IF;

END IF;

END IF;

END PROCESS P2;

end Behavioral;

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

-- Uncomment the following lines to use the declarations that are

-- provided for instantiating Xilinx primitive components.

--library UNISIM;

--use UNISIM.VComponents.all;

entity shuzizhong is

Port ( clr,enble,clk : in std_logic;

output1,output2 : out std_logic_vector(3 downto 0);

output3,output4 : out std_logic_vector(3 downto 0);

output5,output6 : out std_logic_vector(3 downto 0);

qcc : out std_logic);

end shuzizhong;

architecture Behavioral of shuzizhong is

component counter60 is

port(clk, en,clr : IN STD_LOGIC;

qh,ql : OUT STD_LOGIC_VECTOR (3 downto 0);

qcc: OUT std_logic) ;

end component;

component counter24 is

port (en,clk,temp : in std_logic;

qh,ql : out std_logic_vector(3 downto 0);

qcc : out std_logic);

end component;

signal qcc1,qcc2,qcc3:std_logic;

signal temp1,temp2,temp3,temp4,temp5,temp6:std_logic_vector(3 downto 0);

begin

u1:counter60 port map(clk,enble,clr,temp5,temp6,qcc1);

u2:counter60 port map(clk,qcc1,clr,temp3,temp4,qcc2);

u3:counter24 port map(qcc2,clk,qcc1,temp1,temp2,qcc3);

output1 <= temp1;

output2 <= temp2;

output3 <= temp3;

output4 <= temp4;

output5 <= temp5;

output6 <= temp6;

qcc <= qcc3;

end Behavioral;

7仿真结果: