���ֵ����ӿγ���Ʊ���

�� �� �� �� ���ֵ�·��������

�� �� �� Ŀ ���ֵ���������·���

ר ҵ ���ӿ�ѧ�뼼��

�� �� 20##�����ӣ�3����

�� ��

ͬ �� ��

ָ �� �� ʦ

20##��1�� 4��

Ŀ¼

һ�� ����ժҪ... 4

���� �������ݼ�Ҫ��... 4

���� �����Ƚ�... 5

1. ����һ��... 5

2. ��������... 5

3. ������: 5

�ġ� ������˵... 6

1. 1Hz��ʱ�Ӳ�����·��... 6

2. У������ģ�飺... 7

3. �����ͽ�λģ�飺... 8

4. ����ģ�飺... 9

5. ��ʾģ�飺... 9

6. ֱ����ѹ��Դ��... 9

7. PCB����ͼ��... 10

�塢 ��װ���Թ���... 10

���� ��ƹ��������������⼰��������... 10

�ߡ� �ܽ�... 11

�ˡ� Ԫ�����嵥... 12

�š� �Ը���ƵĽ���... 13

ʮ�� �ο�����... 14

һ�� ����ժҪ

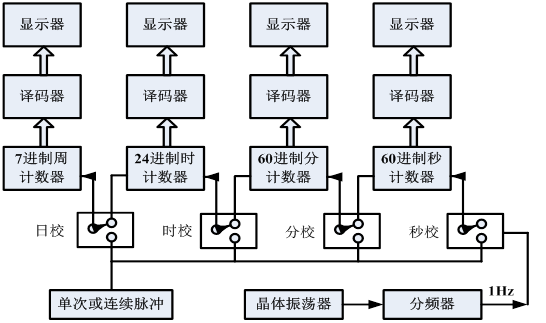

���ֵ�������һ����������ʾ�롢�֡�ʱ���յļ�ʱװ�ã��봫ͳ�Ļ�е����ȣ���������ʱȷ����ʾֱ�ۡ���е����װ�õ��ŵ㣬����õ��˹㷺��Ӧ�ã�С���ճ������еĵ����ֱ�����վ����ͷ�������ȹ��������Ĵ�����ʾ�����ӡ������ε���������Ŀ������һЩ�ض���Ӳ����оƬ������ɷ�Ƶ����λ�����룬��ʾ�ȹ��������մ��һ������ʵʱ��ʾ��ǰʱ���磺ʱ���֡�������ڵĵ���ʱ�ӣ�����Ҫ����п��Ե��٣��Զ���λ�ȹ��ܡ������ֵ�������ʯӢ���������ͷ�Ƶ����ɵ������巢������Уʱ��·����ʮ�����롢�ּ�������24���ƻ�12���Ƽ�ʱ���������Լ��롢�֡�ʱ��������ʾ���ֵȹ��ɡ�

���� �������ݼ�Ҫ��

1. �ɾ����·����1Hz�ı����źţ�

2. �롢��Ϊ00-59��ʮ���Ƽ�������

3. ʱΪ00-23��ʮ�Ľ��Ƽ�������

4. ����ʾ��1-��Ϊ�߽��Ƽ�������

5. ���ֶ�У�����ֱܷ�����롢�֡�ʱ���յ�У����ֻҪ�����������ֶ�λ�ã��ɷֱ���롢�֡�ʱ���ս����ֶ���������������������������У����

���� �����Ƚ�

1. ����һ��

555��ʱ����ƵĶ�г��������������Ϊ1s�����塣�����ź�������������м��㣬�����ۼӵĽ���ԡ�ʱ�������֡������롱��������ʾ���������롱����ʾ����������������������ɵ���ʮ���Ƽ�����·ʵ�֣����֡�����ʾ��·���롱��ͬ����ʱ������ʾ����������������������ɵĶ�ʮ�Ľ��Ƶ�·��ʵ�֡����м�ʱ�������λ�������ʾ������555��ʱ���ܹ�������Ĺ���ʩ���ش�����������̬�������Ͷ�г����������ʹ�������㣬������ʩ���ش������Ļ����ϸĽӳɶ�г������

2. ��������

���Ҳ���Բ��õ�Ƭ�����п��ơ��������������źŴ�XTAL2�������Ƭ�ڵ�ʱ�ӷ������ϡ�ʱ�ӷ�����Ϊ����Ƶ������CPU�ṩ����ʱ���ź�P1��P2��ÿ��ʱ���������������ģ��ࣩP1��P2��CPU��������ʱ��P1��P2Ϊ��������ָ��AT89S52��Ƭ��������Э��������

3. ������:

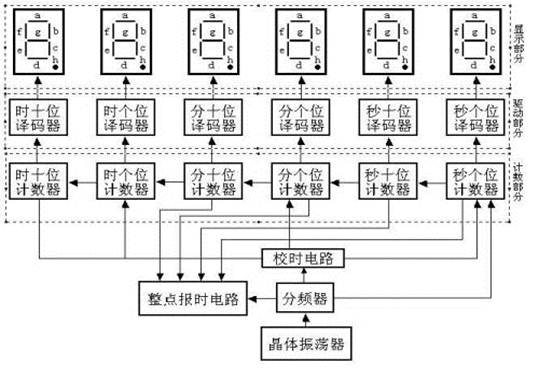

����ʯӢ�������������ŵ�·ʵ�֡�����ʵ����ѡ��÷�������ϵͳ��ͼ���£�

�ġ� ������˵

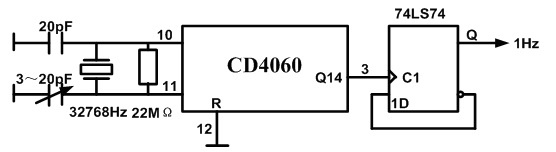

1. 1Hz��ʱ�Ӳ�����·��

ʱ�Ӳ�����·������ʯӢ�������ʯӢ�����������ڵ����������Ե�Ч��һ�����ݺ�һ�����貢�����ٴ���һ�����ݵĶ������磬�������������г��㡣���ھ���������������ʹ������Ƶ�ʵľ����൱�Ľӽ����������խ��Ƶ�ʷ�Χ�ڣ������ЧΪһ����У���ˣ�����������˲����Ϻ��ʵĵ������ͻ���ɲ���г���·���������г���·�ӵ�һ����������·�оͿ��Թ������Ҳ���·����·����Ƶ�ʼ�ȡ����ʯӢ����IJ���г��Ƶ�ʣ���R��C����ֵ�ء�

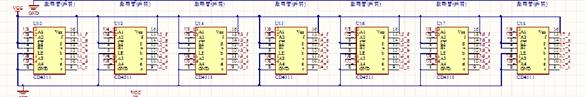

����������·�����ֵ������ṩ��һ��Ƶ���ȶ�ȷ��32768Hz�ķ����źţ������һУ�����ݿ��Զ��¶Ƚ��в����������Ƶ��ȷ�Ⱥ��ȶ��ȣ�ʹ�ȶ�������10^-4���ɱ�֤�����ӵ���ʱȷ���ȶ������Dz���32768����Ϊ�˵õ�1Hz�����壬����Ҫ����15�ζ���Ƶ����������ѡ��CD4060��14�ζ���Ƶ��Ƶ����74HC74D������оƬ��ɵĶ���Ƶ������15�εĶ���Ƶ�����յõ�1Hz�����塣���ģ��ĵ�·ͼ���£�

2. У������ģ�飺

�������ģ������ֱ����CD4060��Q13��������У�Ե�·��ʱ�ӣ���һ��������ѡ��У�Ժ�������ʱ��У�Ե�Ƶ���ڴ˴ο�����Ϊ32768/��2^13�� =4Hz����������ĵ�·ͼΪ��

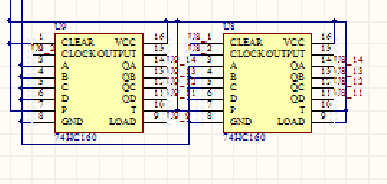

3. �����ͽ�λģ�飺

���λ��60���ƣ����ֽ��ƣ�ʱ���ƣ����ڽ��ƣ�

������Ƭ10���Ƶ�74ls160��ȡ������ʽ�����У���·ͼ�������£�

����u3�Ľ�λ����ˣ�output����u4��ʱ������ˣ�clock�ˣ���ͨ��74hc04 ������һ������������ͨ�ġ�

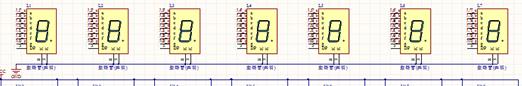

��ͼ��ʾ��ʱ�������·�����λ����ʮλ���������ָ�λ�ͷ�ʮλ��������ʱ��λ��ʱʮλ�����������ڼ�������·���ɣ��������λ����ʮλ���������ָ�λ�ͷ�ʮλ������Ϊ60���Ƽ�������ʱ��λ��ʱʮλ������Ϊ24���Ƽ����������ڼ�����Ϊ7���Ƽ�������

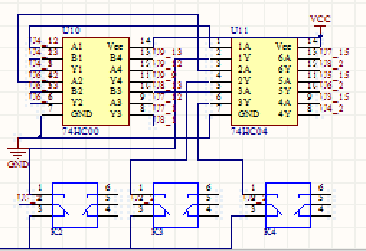

4. ����ģ�飺

�˴�����ģ��Ƚϼ��Dz���ר�õ�����оƬCD4511��ʵ�֡�CD4511��һ���������������� LED ������ܣ���ʾ���� BCD �롪�߶������������ص㣺����BCDת����������������ơ��߶����뼰�������ܵ�CMOS��·���ṩ�ϴ������������ֱ������LED��ʾ������·ͼ���£�

5. ��ʾģ�飺

�����������ģ���֪�����������ʾ�ܹ�����7������������ܵľ�̬��ʾ��ʽ���Ƚϼ�������ֱ�Ӹ��ϵ���ͼ��

6. ֱ����ѹ��Դ��

�ڵ��ӵ�·�У�ͨ������Ҫ��ѹ�ȶ���ֱ����Դ���硣�����ɵ�Դ��ѹ�����������˲�����ѹ��·���IJ�����ɡ�����Ʋ��õ�ֱ����ѹ��Դ������Ϊ220V�Ľ����磬���Ϊ5V���ҵ��ȶ���ѹ��

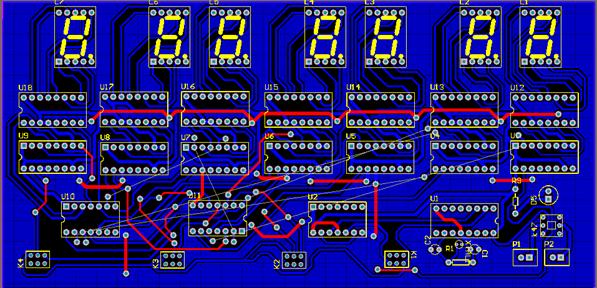

7. PCB����ͼ��

�塢 ��װ���Թ���

1��ʹ��multisim������ܽ��з��棬ȷ����оƬ�ķ�Ƶ��ʹ���������������

2��ʹ���������д��ߵ��ԣ�ȷ����·��������

3��PCB���ߡ�

4�����������õİ���ж�·����

���� ��ƹ��������������⼰��������

�ڼ�������״���Ĺ�����,���ֱ�����ͨ�ĵط�ȴδͨ��״��,���鷢�����������ñ��ʼ�δ��������ڲ���ֱ�Ӵ�����.

�ڼ��CD4511������·�Ĺ����з�������ܲ���������ʾ��״��,�����鷢����Ҫ�����ڽӴ�����������,���а����ߵĽӴ�������оƬ�ĽӴ�����,��ʵ�������,������м��ζ�����ʱ��ʱ��,��ʱ����ʧ.��5V��Դ������ܽ��м��,һ�˽ӵ�,��һ�˽Ӵ�ÿһ�ζ�����,���ֶ�������������ʾ��,�������ñ�ŷķ�����ÿһ�����Ƿ�Ӵ�����,�ڼ������з����м�������ʱ�ܽ�ͨ,��ʱ���ܽ�ͨ,�ѽӴ����õ������½ӹ�������������ʾ��.���������оƬ�Ӵ�����������,�����ñ�ŷķ������м������ű�����ͨ�ĵط�ȴδͨ,�����ĵ���״������,��������Ϊ��CD4511��оƬ�γ�,���������ĵ�״�����µ���������,ʹ�������ڿ�,���������ȵؽ�оƬ�����������,�˺�����������ʾ,����ʵ���л�����һ�黵��LED����ܺ����黵��CD4511,�����������������ʾ��

�ߡ� �ܽ�

ͨ������ʵ������֪ʶ���˸�������˽⣬�������õ���ʵ��������������ѧϰ���Ӽ������������壬Ҳ�ﵽ����������Ŀ�ġ���ʵ���У���Ҳ�����˺ܶ���ۣ������Ҷ���ͬ��һһ�˷��ˣ��������Э����������⣬ʹ�������˺����˹�ͬ��������Ҫ�ԡ����Ժ�ĵ�·������Ҳ���������ʶ���ŶӺ�������Ͷ����ķ�չ֮�У�ʵ������������������Ҫ��������ʵ�������������������ý�ѧ��ԶԶ�����ģ�����ӿ�������ʵ������Ҳ��һ��Ԥ�ݺ�����ҵ��ƹ�����ͨ���γ���ƣ��������ҳ�����״����ʵ����Ҫ�IJ�࣬�����Ժ��ѧϰ�ڼ估ʱ�������֪ʶ��Ϊ��ְ����ʽ�������ó�ֵ�֪ʶ�����������Ӷ����̴�У������������ת���ڡ�

��Ϊ����ѧϰ��ϵ���л���ɲ��֣��γ������Ȼ�����ڶ������ܽ��У����������о��Զ��������塣����һ����Ҫ���ܣ���������ѧϰ�ɹ�������ѧϰ�ɹ�������ѧϰ�ɹ����ѿ�����ѧ����ϵͳ��������֪ʶ�������Ե�Ӧ����ʵ����ƹ������������۵ĸ߶ȶ���ƹ������ִ������һЩ������ԵĽ�������롣����ѧϰ�ɹ�����һ������ѧϰ��ʵ�ʹ��������ж����룬��ͨ���ۺϷ������ҳ�ѧϰ�д��ڵIJ��㣬�Ա�Ϊ����ѧϰ�ƻ����ı�ѧϰ�����뷽���ṩʵ�����ݡ�

�ڽ��е�·���ӵ�ʱ����ȷ��һ�ж���������֮��ʱ����ʾ���������⣬������ʦ��ָ�����ϸ��������dz������������������⣬�������Ƕ��������������ϸ���Ե�·��������ԭ��Ӧ���������ӡ�������ʱ��·�ﵽ24Ҫ�����ʱ��λ����ʱ�Ӳ�����ô���ף����������ѧ����������Ҫ����һ�����ŵ�·����ʱé���ٿ���

�ɹ������ڲ���������ǰ��ʵ�ֵģ������������Dz��ܻ��ġ����꣬������������Ҫ����������ϸ˼�����ֲ���飬�ҳ����յ�ԭ����и����������Ż��н������Ż�һ�������Լ���Ŀ�꿿�����Ż�ȡ���Լ���Ҫ��ijɹ���

�ˡ� Ԫ�����嵥

�š� �Ը���ƵĽ���

�˴ε����ֵ����ӿγ������Ȼ�ܰѵ�·ͼ�ӳ���,����������ʾ,�����ڵ�·������ԭ��������ʮ����Ϥ���ܵ���˵,ͨ����ε����ʵ�����һ������ǿ��ʵ��Ķ���������

ʮ�� �ο�����

1. ���ֵ��Ӽ�������������棩�廪��ѧ����ѧ������ ��

2. ������Դ���㽭����ѧԺ������ϢѧԺ��ѩͬѧ�����ֵ��Ӽ����γ���Ʊ��档

3. �ٶ��Ŀ�������ϡ�

4. 74HC00�� 74HC04��PDFоƬ���ϡ�

�ڶ�ƪ�����ֵ����ӿγ���Ʊ���-����

�浵���� �ɼ�����

������ͨ��ѧ����ѧԺ

�� �� �� �� �� �� ��

�����γ����� ���ֵ��Ӽ����γ����

�� Ŀ �� ���ֵ����ӿγ���ơ��������������� ������

�� Ժ �� �� �� Ժ ���� ��

רҵ�༶ 10����2��

ѧ������ 20100210410201 �� �������� ���� ��

ѧ������ �� �� �� �� �������� ������

ָ����ʦ �� �� �� ������

20 12 �� 12 �� 18 ��

Ŀ��¼

��1�� �γ�������ݼ�Ҫ��... 3

��2�� Ԫ�����嵥����Ҫ��������... 5

��3�� ԭ����ƺ�������... 10

��4�� ���ֵ����ӵ�ʵ��... 15

��5�� ʵ���ĵ�... 16

��6�� �����... 17

��1�� �γ�������ݼ�Ҫ��

1.1 �����Ӽ��

20����ĩ�����Ӽ�������˷��ٵķ�չ�������ƶ��£��ִ����Ӳ�Ʒ�����������ĸ��������������ƶ�������������ķ�չ�������Ϣ���̶ȵ���ߣ�ͬʱҲʹ�ִ����Ӳ�Ʒ���ܽ�һ����ߡ���Ʒ���»����Ľ���ҲԽ��Խ�졣�������ѳ�Ϊ�����ճ������бز����ٵ���������Ʒ���㷺���ڸ��˼�ͥ�Լ���վ����ͷ���糡���칫�ҵȹ��������������ǵ����ѧϰ�����������ִ�������ķ��㡣�������ּ��ɵ�·�����ķ�չ�Ͳ������Ƚ���ʯӢ������ʹ�����Ӿ�����ʱȷ�������ȶ������ɵ�·�����С������С�����ܶࡢЯ��������ŵ㡣

��˱�����ƾ������ּ��ɵ�·��һЩ�����ŵ�·�����һ������ʽ�����ӣ�ʹ�����ʱ�估���ڵ���ʾ���ܡ���������Ӳ������ֵ�·ʵ�ֶԡ�ʱ�������֡������롱������ʾ�ļ�ʱװ�á�����ʱ����ʾ����ʱȷ����ʾֱ�ۡ����ȡ��ȶ����ŵ㣬��·װ��ʮ��С��,��װʹ��Ҳ������ܹ�����ѵ�ϲ����

1.2 ���Ŀ��

1. �����������·��ʱ������·����������·ϵͳ����ơ���װ�����Է�������

2. ��һ��������ѧ������֪ʶ�����������ѧ֪ʶ�����ͽ��ʵ���������������

�� 3. ��ߵ�·���֣����������ų����ϵ�������

1.3 ���Ҫ��

��

1. ���һ���С�ʱ�������֡������롱��23Сʱ59��59�룩��ʾ������Уʱ���ܵĵ����ӡ�

2. ����С��ģ���ɵ�·��ɵ����ӣ�����ʵ�����Ͻ�����װ�����ԡ�

�� 3. ������ͼ������·ͼ��д����ơ�ʵ���ܽᱨ�档 ��

4. ���㱨ʱ����59��59��ʱ����źţ���Ƶ����1s���ڽ���ʱ��Ϊ���㡣 ��

��2�� Ԫ�����嵥����Ҫ��������

2.1 Ԫ�����嵥

��1��74LS160�� 6Ƭ��

��2��74LS247��6Ƭ��

��3��74LS00��1Ƭ��

��4�������߶�������ʾ����6Ƭ��

��5��CD4013��1Ƭ��

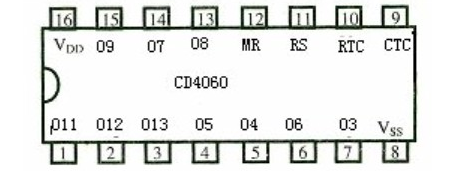

��6��CD4060 (1Ƭ)

��7��4012 (1Ƭ)

��8�����衢�����ݡ����ߡ���˿�ȣ����ɣ�

2.2 ��ҪԪ�����������м�������

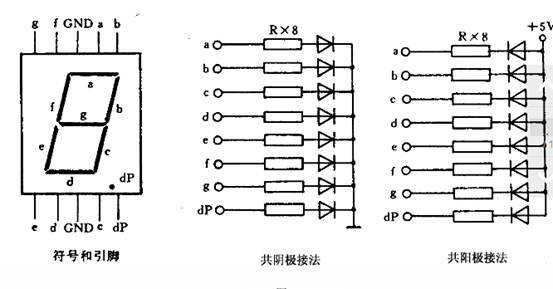

1.�����߶���ʾ��

��������ܣ���ͼ����dp��ʾ����������ʾС���㡣ͨ���߶η�������������IJ�ͬ��ϣ�������ʾ�������֡���ĸ�Լ��������š�

LED������еķ�������ܹ����������ӷ�����

1���������ӷ����ѷ�������ܵ���������һ�ɹ���������ʹ��ʱ���������ӵأ���������������ߵ�ƽ�Ķη�������ܾ͵�ͨ������������͵�ƽ��������ʵ����ʹ�õ�LED��ʾ��Ϊ�������ӷ�

2���������ӷ����ѷ�������ܵ���������һ�ɹ���������ʹ��ʱ���������ӣ�5V����������������͵�ƽ�Ķη�������ܾ͵�ͨ������������ߵ�ƽ��������

ע�� ������ʹ�õ��ǹ���������ܡ�

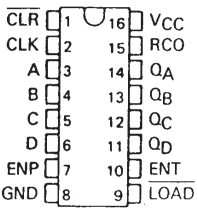

2. 74LS160оƬ����

74LS160��ʮ����ͬ�����������첽���������ܽ�ͼ����������ͼ��ʾ��

RCO ������

ENP �������ƶ�

QA-QD �����

ENT �������ƶ�

CLK ʱ�������

CLR �첽����ˣ��͵�ƽ��Ч��

LOAD��ͬ����������ˣ��͵�ƽ��Ч��

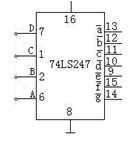

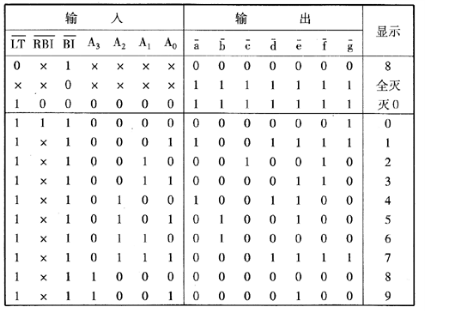

3. ��������74LS247��

74LS247�����Ź���˵������ͼ��6 ��2��1��7��Ϊ�������루�������������9��15Ϊ���������8��16��Ϊ��Դ��������

74LS247���������ܱ�

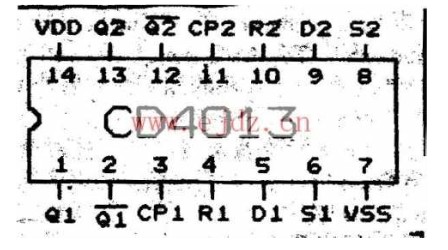

4 CD4013

CD4013��һ˫D������,��������ͬ�ġ�������������ʹ��������ɡ�ÿ���������ж��������ݡ���λ����λ��ʱ�������Q��Q�������������������λ�Ĵ�������ͨ����Q������ӵ��������룬�������������ʹ���������ʱ�������ش���ʱ������D����˵�����ƽ���͵�Q����ˡ���λ��λ��ʱ���أ����ֱ�����λ��λ���ϵĸߵ�ƽ��ɡ�

5 CD4060

��CD4060��һ������14�������ƴ��м�����λ��ɡ������Ľṹ������RC�����·��CRΪ�ߵ�ƽʱ������������������ʹ����Ч�����еļ�����λ��Ϊ���Ӵ���������CP1(��CP0)���½��ؼ������Զ����ƽ��м�������ʱ����������ʹ��˹���ش�������ʱ���������½�ʱ�������ơ�

��3�� ԭ����ƺ�������

3.1���ּ�ʱ�������˼��

Ҫ�빹�������ӣ�����Ӧѡ��һ������Դ�������Զ��ز����ȶ��ı�ʱ�������źš�������Դ�����������źŵ�Ƶ�ʽϸߣ���ˣ���Ҫ���з�Ƶ��ʹ�ø�Ƶ�����źű���ʺ��ڼ�ʱ�ĵ�Ƶ�����źţ������������źš���Ƶ��Ϊ1Hz����������Ƶ��������������źŵ��������н��м��������ڼ�ʱ�Ĺ����ǣ�60��=1�֣�60��=1Сʱ��24Сʱ=1�죬����Ҫ�ֱ����60���ƣ�24���Ƽ������������������źš�������������źž�����������������������ʾ�����ǡ�ʱ�������֡������롱����������ʾ������

3.2���ֵ�����������ͼ

ͼ3-1

��һ��������

�������źž���6�����������ֱ�õ����롱��λ��ʮλ�����֡���λ��ʮλ�Լ���ʱ����λ��ʮλ�ļ�ʱ�����롱���֡�������Ϊ��ʮ���ƣ�СʱΪ��ʮ�Ľ��ơ�

��1����ʮ���Ƽ���

�ɷ�Ƶ�������������źţ������͵����롱�����������ۼӼ������������Ӧ���һ����֮������Ŀ���ۼӣ����ﵽ60��ʱ����һ����λ�źţ����ԣ�ѡ����Ƭcc40192��һƬcc4011�����ʮ���Ƽ���������ʵ����ʮ���Ƽ��������У����롱ʮλ�������ƣ����롱��λ��ʮ���ơ�

��2����ʮ�Ľ��Ƽ���

��12��1��Сʱ�������ǰ��ա�01����02����03������������22����23����00����01����02�������������ɼ����ģ������ճ������еļ�ʱ������ͬ���ڴ�ʵ���У���������Ƭcc40192��һƬcc4011����ɵ�ͬ����ʮ�ļ������������첽�����ʵ�����23����00�ķ�ת�����С�24��Ϊ����״̬����ʾ�����У���ʱ��ʮλ��3���ƣ���ʱ����λ��ʮ���� ��

��������ʾ��

��ϵͳ���߶η������������ʾ��������������֣���ʾ�������֣���������ʾ����������ʾ����74LS48��������Ӧ����ʾ���ǹ�������ʾ����

��������Ƶ--�����·

����CD4060�����輰�������ӳ�һ����Ƶ--�����·������ͼ��

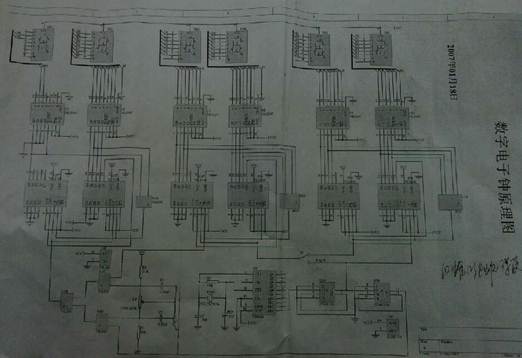

3.3���ֵ�����ԭ��ͼ

3.4���ֵ����ӽ���ͼ

3.5���ֵ����ӵ���װ�����

��ͼ3-1����ʾ��������ϵͳ��ɿ�ͼ�����źŵ�����ּ���װ�������������ÿһ����ָ��������еĸ������ܵ�·��

����ʱ�������ʱ����ϲ�ͬ������������ţ�����������ң��������Ӷ༶��������ʱ�������ʾ�ַ��仯�ܿ죬ģ�����壬���������ڵ�Դ��������������ģ����ڼ��ɵ�·�����ĵ�Դ��Vcc����ź�˲����ݡ�ͨ���ü�ʮ���Ĵ������0.01��F��С�����ಢ����

��4�� ���ֵ����ӵ�ʵ��

PCB������

PCB�巴��

��5�� ʵ���ĵ�

ͨ��������ֵ����ӵĿγ���ƣ����ǰ�ѧ���Ķ�����ʵ�����ϡ���������ж�����ѧ��֪ʶ���˸���һ�������⣬���Ҹ���һ������Ϥ��оƬ�Ľṹ�������˸�оƬ�Ĺ���ԭ����������ʹ�÷�����Ҳ�������Լ�����˼�������������ͨ���鿴�����������������ϰ�ߡ�

��Ȼ��ֻ��һ��ѧ��ĩ�Ŀγ���ƣ���ͨ����ογ���������˽��˿γ���Ƶ�һ�㲽�衢�����������Ӧע���һЩ���⡣�Ҿ����������Ǻ�����Ҫ����ģ���������ͬѧ�ǶԴ�����ʱ��̬�Ⱥʹ���������������˽��˸���оƬ�ܹ����ʲô���Ĺ��ܣ�ʹ��оƬʱӦ��ע����ЩҪ�㣬ͬһ����·��������ЩоƬʵ�֣�����оƬʵ��ͬһ�����ܵ�����

��֮����ογ��������ѧ���˺öණ�������ֿγ���ƶ�һ����ѧ���Ƿdz���Ҫ�ġ��ڴ���Ҫ��л��ͬ��Ĵ���ر����żѣ�Ȼ�dz���л����ʦ������ָ�������dz���лѧУ�������ṩ������ѧϰ���ᣡ

��6�� �����

[1] ���������.��������·�����ʵ�顾M��.�Ϻ����Ϻ���ͨ��ѧ�����磬1988.

[2] ��ʯ����.���ֵ��Ӽ���������M��.�����.�������ߵȽ��������磬2006. 3.

[3]���й����ɵ�·��ȫ����дίԱ���.�й����ɵ�·��ȫTTL���ɵ�·��M��.������������ҵ�����磬1985.

[4] ����������.���Ӽ��������γ���ơ�M��.�人�����пƼ���ѧ�����磬2009.

[5] �춨������.���ӵ�·������ʵ�顾M��.�������廪��ѧ�����磬2004.

�� л