一、实验目的

1、 掌握组合逻辑电路的功能测试。

2、 验证半加器和全加器的逻辑功能。

3、 学会二进制数的运算规律。

二、实验元器件

数电实验箱、集成芯片(74LS00、74LS10、74LS54、74LS86)、导线。

三、实验内容

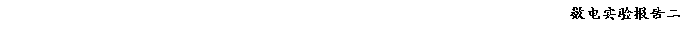

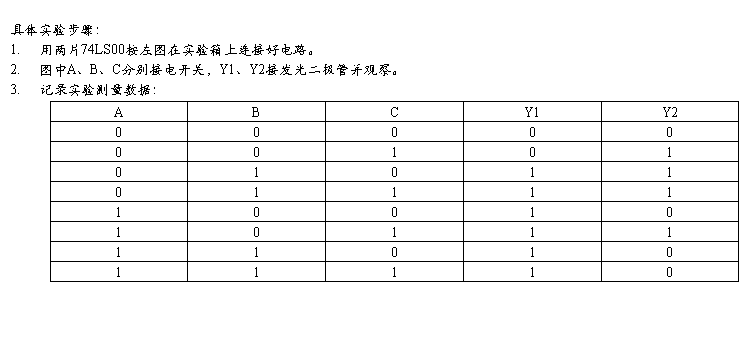

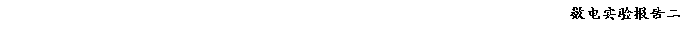

1、 组合逻辑功能路功能测试。

用两片74LS00组成图2-3所示的逻辑电路。

…… …… 余下全文

一、实验目的

1、 掌握组合逻辑电路的功能测试。

2、 验证半加器和全加器的逻辑功能。

3、 学会二进制数的运算规律。

二、实验元器件

数电实验箱、集成芯片(74LS00、74LS10、74LS54、74LS86)、导线。

三、实验内容

1、 组合逻辑功能路功能测试。

用两片74LS00组成图2-3所示的逻辑电路。

…… …… 余下全文

四位全加器

11微电子 黄跃 1117426021

【实验目的】

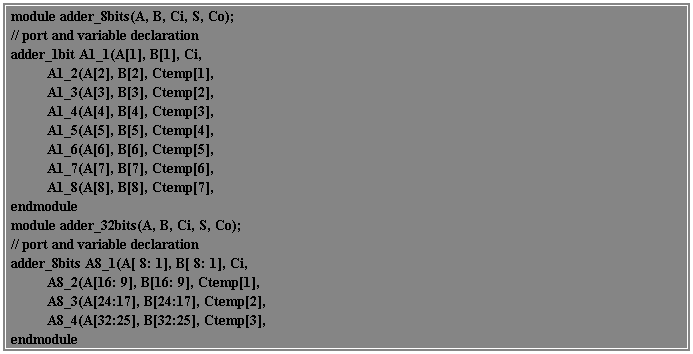

采用modelsim集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。

【实验内容】

加法器是数字系统中的基本逻辑器件。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。

实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0).

【实验原理】

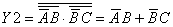

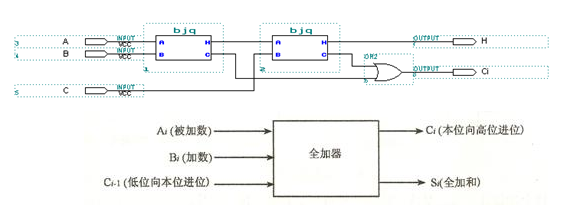

全加器

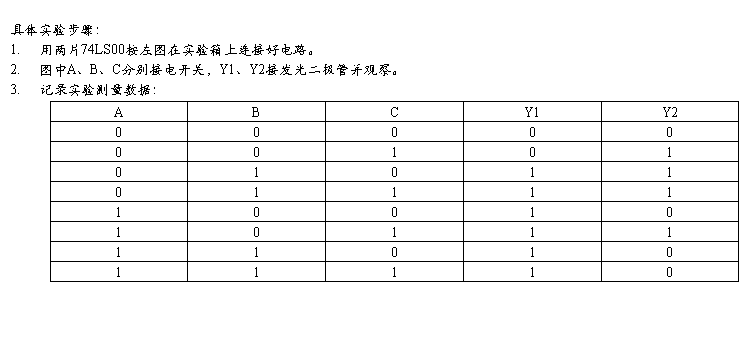

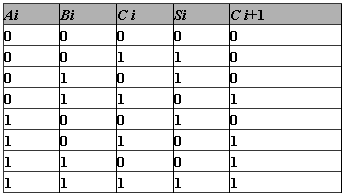

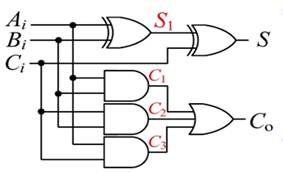

除本位两个数相加外,还要加上从低位来的进位数,称为全加器。图4为全加器的方框图。图5全加器原理图。被加数Ai、加数Bi从低位向本位进位Ci-1作为电路的输入,全加和Si与向高位的进位Ci作为电路的输出。能实现全加运算功能的电路称为全加电路。全加器的逻辑功能真值表如表2中所列。

表2 全加器逻辑功能真值表

图4 全加器方框图

图5 全加器原理图

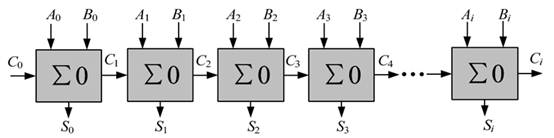

多位全加器连接可以是逐位进位,也可以是超前进位。逐位进位也称串行进位,其逻辑电路简单,但速度也较低。

四位全加器

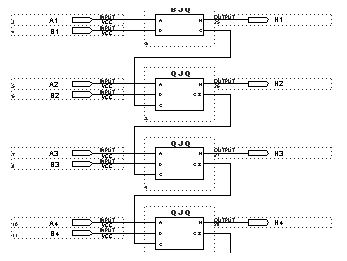

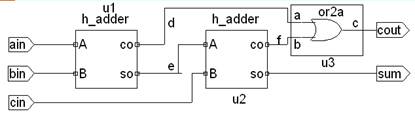

如图9所示,四位全加器是由半加器和一位全加器组建而成:

【实验步骤】

(1)建立新工程项目:

打开modelsim软件,进入集成开发环境,点击File→New project建立一个工程项目adder_4bit。

建立文本编辑文件:

点击File→New在该项目下新建Verilog源程序文件adder_4bit.v

并且输入源程序。

(2)编译和仿真工程项目:

在verilog主页面下,选择Compile— Compile All或点击工具栏上的按钮启动编译,直到project出现status栏全勾,即可进行仿真。

…… …… 余下全文

专业班级: 2010级电子2班

学号: 10200207 姓名:周 娟

EDA 技术实验报告

实验项目名称:在QuartusII中用原理图输入法设计1位加法器

实验日期: 20##-5-10 实验成绩:

实验评定标准:

一、 实验目的

熟悉利用QuartusII的原理图输入方法设计简单组合电路,掌握层次化设 计的方法。

二、 实验器材

电脑一台 ,试验箱一个

三、 实验内容(实验过程)

…… …… 余下全文

南昌大学实验报告

南昌大学实验报告

学生姓名: 学 号: 专业班级:

实验类型:□ 验证 □ 综合 □ 设计 □ 创新 实验日期: 实验成绩:

实验一 全加器的设计

(一) 实验目的

以一位二进制全加器为例熟悉利用QuartusII的原理图输入方法和文本输入法设计简单组合电路;学习多层次工程的设计方法。

(二) 实验要求

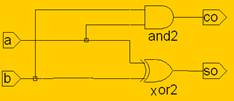

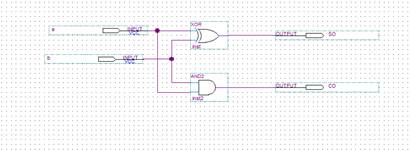

⑴用文本方法实现半加器,再采用层次设计法用原理图输入完成全加器的设计;

⑵给出此项设计的仿真波形;

⑶用发光LED指示显示结果。

(三)实验步骤:

1.(1)建立工作库文件夹,建立半加器工程h_adder,输入半加器VHDL代码并存盘。

library ieee;

use ieee.std_logic_1164.all;

entity h_adder is

port ( a, b :in std_logic;

co,so :out std_logic);

…… …… 余下全文

4位全加器的设计实验报告

班级:通信12-2班 学号:12090216 姓名:韦建萍

一、实验目的

熟悉利用Quartus II 的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个4位全加器的设计,掌握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。

二、 实验原理

一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出 cout 与相邻的高位加法器的最低进位输入信号 cin 相接。

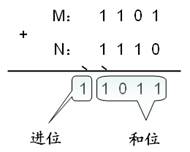

加法器举例说明:设M = 1101 ,N = 1110,CIN=0, 则

1、 半加器(设其名为h_adder)的电路:

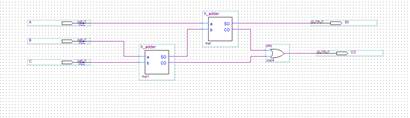

2、 全加器(设其名为f_adder)的电路:

三、实验内容和步骤

1、完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真;

半加器电路原理设计图如图:

半加器电路仿真图如图:

全加器电路原理设计图如图:

全加器电路仿真图如图:

2、建立一个更高层次的原理图设计,利用以上获得的1位全加器构成4位全加器,并完成编译、综合、适配、仿真。

4位全加器电路原理图如图:

4位全加器仿真图如图:

四、仿真分析及心得体会

仿真分析:

四位全加器S0为和位,C0为进位,当a0=1,b0=1时,S0=0,C0=1,就是和位为零,进位进1。以此类推,当a1=1,b1=0,C0=1时,和位S0=0,进位C0=1。

…… …… 余下全文

1. 掌握一位全加器的工作原理和逻辑功能

2.掌握串行进位加法器的工作原理和进位延迟

3.掌握超前进位的工作原理

4.掌握减法器的实现原理

5.了解加法器在CPU中的地位

6.掌握FPGA开发平台进行简单的I/O数据交互

实验内容:

1.实现16位加减器的调试仿真

2. 16位计算器设计

实验原理:

2.1 一位全加器(FA)

全加器是一个能对一位二进制数及来自低位的进位进行相加,产生本位和及向高位进位的逻辑电路。该电路有3个输入变量,分别是2个加数Ai 和 Bi,低位进位输入 Ci ,2个输出变量,分别是全加和 Si,进位输出 Ci+1。

一位全加器的逻辑表达式:Si = Ai?Bi?Ci 、 Ci+1=Ai Bi+BiCi+CiAi

图表1:一位全加器真值表

由一位全加器的输入输出关系,得到电路图 :

图表2 一位全加器的电路图和代码

2.2多位串行进位全加器

多位全加器可由一位全加器将进位串接构成。高位进位生成速度慢,每一位的相加结果都必须等到低一位的进位产生以后才能建立起来,所以位数越多时间越长。

图表3多位串行进位全加器示意图及代码

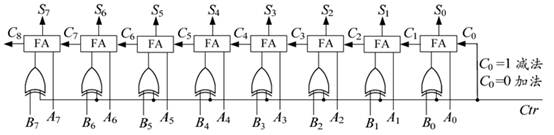

2.3多位串行进位全减器

原理:

? 用负数补码加法实现,减数当作负数求补码

? 共用加法器

? 用“异或”门控制求反,最低进位位加一

图表4 多位串行进位全减器电路图

…… …… 余下全文