摘自EDACN,一位大侠自己的fpga学习心得!

标签: fpga verilog 分类: 学习笔记---FPGA篇 20##-01-23 12:48

…… …… 余下全文

FPGA设计与应用

分频器设计实验报告

班级:05101班

姓名:李原

学号:1100500133

日期: 2013 年 9 月 23 日

实验性质:验证性 实验类型:必做

开课单位:电信院 学时:2学时

一、实验目的

1、了解Quartus II软件的功能;

2、掌握Quartus II的HDL输入方法;

3、掌握Quartus II编译、综合、适配和时序仿真;

4、掌握Quartus II管脚分配、数据流下载方法;

…… …… 余下全文

回想起自己学FPGA,已经有一段时间了,从开始的茫然,到

后来的疯狂看书,设计开发板,调电路,练习各种FPGA实例,到最后能独立完成项目,一路走来,感受颇多,拿出来和大家分享,顺便介绍下自己的一点经验所得,希望对初学者有所帮助。

废话不说了,下面进入正题,学习FPGA我主要经历了这么几个阶段:

①、Verilog语言的学习,熟悉Verilog语言的各种语法。

②、FPGA的学习,熟悉QuartusII软件的各种功能,各种逻辑算法设计,接口模块(RS232,LCD,VGA,SPI,I2c等)的设计,时序分析,硬件优化等,自己开始设计简单的FPGA板子。

③、NiosII的学习,熟悉NiosII的开发流程,熟悉开发软件(SOPC,NiosII IDE),了解NiosII的基本结构,设计NiosII开发板,编写NiosII C语言程序,调试板子各模块功能。 先来说说第一个阶段,现在主要的硬件描述语言有VHDL,Verilog两种,在本科时老师一般教VHDL,不过现在

Verilog用的人越来越多,其更容易上手(与C语言语法比较类似),也更灵活,现在的IC设计基本都用Verilog。像systemC,systemVerilog之类的应该还在萌芽阶段,以后可能会有较大发展。鉴于以上原因我选择了Verilog作为我学习的硬件描述语言。

其实有C语言的基础,学起Verilog的语言很简单,关键要有并行的概念,所有的module,assign,always都是并行的,这一点与软件语言有明显不同。这里推荐几本评价比较好的学习Verilog的书籍:

①、《verilog 数字系统设计教程》,这本书对于入门是一本很好的书,通俗易懂,让人很快上手,它里面的例子也不错。但本书对于资源优化方面的编程没有多少涉及到。

②、《设计与验证Verilog HDL》,这本书虽然比较薄,但是相当精辟,讲解的也很深入,很多概念看了这本书有种豁然开朗的感觉,呵呵。

…… …… 余下全文

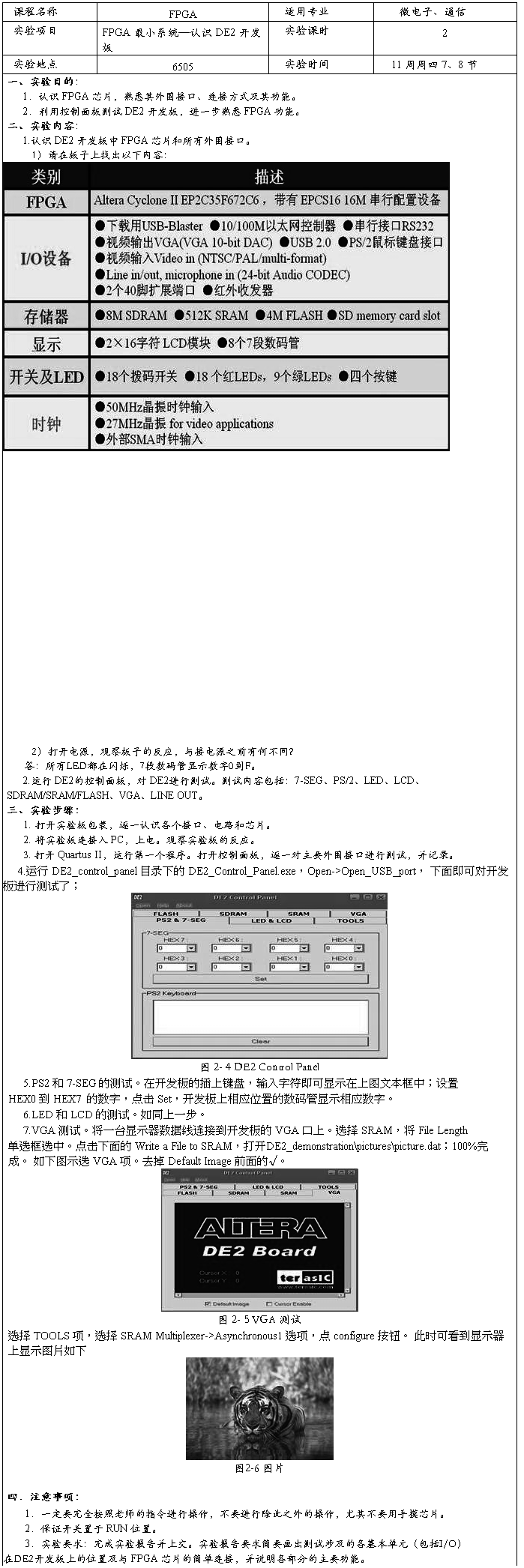

FPGA 实验任务书—实验一

实验心得体会:

通过这一次实验,我熟悉了DE2开发板的使用,也了解了FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

DE2是Altera公司针对大学教学及研究机构推出的FPGA多媒体开发平台。DE2 为用 户提供了丰富的外设及多媒体特性,并具有灵活而可靠的外围接口设计。DE2 能帮助使用 者迅速理解和掌握实时多媒体工业产品设计的技巧,并提供系统设计的验证。DE2 平台的 实际和制造完全按照工业产品标准进行,可靠性很高。

为了使用DE2开发板,我也学会使用QuartusII。通过读DE2开发板使用指南和QuartusII入门介绍可以获得必要的知识。Altera Quartus II 作为一种可编程逻辑的设计环境, 由于其强大的设计能力和直观易用的接口,越来越受到数字系统设计者的欢迎。我也了解了Quartus II软件的一些优点:数十年来一直在缩短编译时间,编译时间平均每年减少20%。Altera高级布局布线算法支持您根据四个成本标准,迅速找到最佳结果——时序、拥塞、走线长度以及功耗,从而缩短了编译时间。

…… …… 余下全文

信号与信息处理综合实验报告

实验一 FPGA使用入门实验报告

学院: 信息与通信工程学院

班级:

1

信号与信息处理综合实验报告

一.实验目的

(1) 掌握ISE 13.2集成开发环境和Modelsim软件的使用方法;

(2) 熟悉S6 Card实验板的使用方法。

(3) 掌握使用Verilog HDL语言实现常用组合逻辑和时序逻辑的方

法。

(4) 了解Chipscope的功能与使用方法。

二. 实验内容

(1) 熟悉S6 CARD实验板;

(2) 熟悉ISE集成开发环境;

(3) 3比特加法器仿真与上板实验

(4)m序列产生器仿真与在板Chipscope调试。

三. 实验过程依照指导书进行

四. 实验代码分析

(1)3bit加法器(见注释)

module m_seq_gen(

//端口I/O定义

input clk,//定义clk为输入类型

input reset,//定义resert为输入类型

output seq//定义seq为输出类型

);

//内部信号说明

reg [3:0] state;//定义变量state,为寄存器型,位宽为4

//功能定义

always @(posedge clk or negedge reset)//当clk上升沿来到或者reset下降沿来到,//触发敏感事件,执行以下程序

begin

if(!reset)//如果不是reset下降沿来到

state <= 4'b1111;//state输出结果为4位的二进制数字1111 else

begin

state[3:1] <= state[2:0];//state从第二位到第四位输出结果为其第一位//到第三位的数值

state[0] <= ^(state & 4'b1001);//state第一位输出结果为state原来的//值与二进制数1001相与的结果

…… …… 余下全文

实验1:状态机

实验目的:学习FPGA设计软件

教学基本要求:掌握软件流程,掌握状态机编程

实验内容提要:设计一个状态机

1. 你觉得上面这段代码中,q 到底在怎样变化?(实验1ppt14页)

答:在上述代码中,q变化如下:首先判断复位信号 rst 是否为 0,如果是 0 则q复位为0;否则当时钟信号上升沿到来时,将d的值赋给q,再判断a的值,如果a为1,则将b赋值给次态q,如果a为其他值,则将现态q赋给次态q。

2. 本页中,q 到底在怎样变化?(实验1 ppt15页)

答:如果异步复位信号rst为0,则q置0;rst不为0时,当时钟上升沿到来时,判断a的值,如果a=1,则将b的值赋给q的次态,如果a是其他值,则将q的现态赋给q的次态,结束这个判断语句后,将d赋值给q。

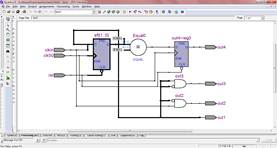

3. 画出你理解的这个电路的原理图(ppt16页)

4.Out1 out2 out3 out4有什么区别?

out1的上升沿与下降沿和50MHz时钟的上升沿始终保持一致,周期变为50MHz时钟的6倍,实现周期扩展;out2的上升沿与clkin的上升沿保持一致,下降沿与out1的上升沿保持一致,可将clkin的数据记录下来以起数据使能作用;out3的上升沿恰好是out2的下降沿,比out2慢一拍,是更适合使用的前端使能;out4的上升沿与out3的下降沿保持一致,可以减少延迟。

2. 红绿灯实验中,该状态机最少几个触发器可以实现?

该逻辑情况下红绿灯状态机最少只需8个触发器即可实现。将3个计时计数触发器合并,并将溢出、使能触发器达成的功能改由计数数值在各状态下的交替变化,使用组合逻辑代替触发器,达成减少触发器使用的设计方案。

实验2 数字钟设计

实验目的:掌握FPGA语言设计方法

教学基本要求:学习基本的VHDL语言结构和设计

…… …… 余下全文