西南科技大学

实验报告

课程名称: FPGA技术

实验名称 基于HDL十进制计数、显示系统设计

姓 名:

学 号:

班 级:

指导教师:

实验题目

一、 实验原理

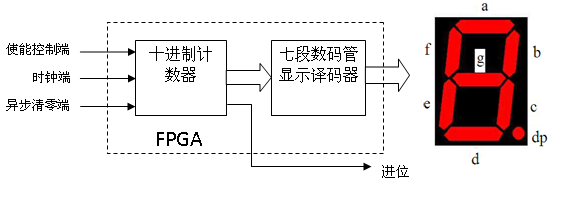

1、实验内容:设计具有异步复位、同步使能的十进制计数器,其计数结果可以通过七段数码管、发光二极管等进行显示。

图2.1系统原理图

2、模块端口信号说明

设计任务表述:

输入信号:

clk_50m ---系统采样时钟

clk -------待计数的时钟

clr ---------异步清零信号,当clr=1,输出复位为0,当clr=0,正常计数

ena---------使能控制信号,当ena=1,电路正常累加计数,否则电路不工作

输出信号:

q[6:0]---------驱动数码管,显示计数值的个位

COM---------共阳级数码管公共端(接地,电路板原理图)

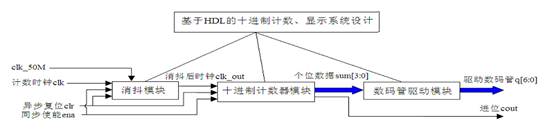

3、以自顶向下的设计思路进行模块划分

整个系统主要设计的模块是:十进制计数模块和数码管驱动模块,由于实验板的按键为实现硬件防抖,则需要将按键输入的时钟clk,先通过消抖模块消抖后,再输出至后续使用。

图2.2系统模块划分和引脚连线图

由以上分析可知本设计总共包括3个模块:

1)十进制计数器(cnt10.v)模块。

2)驱动七段数码管的模块(led.v)。

3)由于实验板上按键需要进行消抖,所以需要一个消抖模块(debounce_module),待计数的时钟clk输入至计数器前,先通过消抖模块。

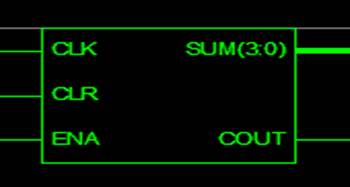

1)十进制计数器模块(cnt10.v)实验原理

输入:

CLK -------待计数的时钟

CLR ---------异步清零信号,当CLR =1,输出复位为0,当CLR =0,正常计数

ENA---------使能控制信号,当ENA=1,电路正常累加计数,否则电路不工作

输出:

SUM[3:0]---------- 计数值的个位。即,在CLK上升沿检测到SUM=9时,SUM将被置0,开始新一轮的计数。

COUT ------------计数值的十位进位,即:只有在时钟CLK上升沿检测到SUM=9时,COUT将被置1,其余情况下COUT=0。

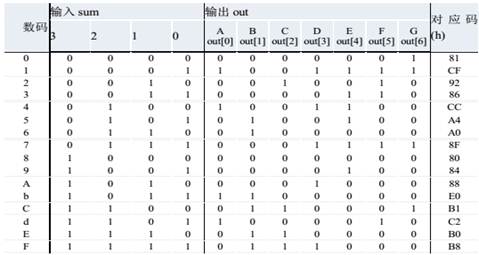

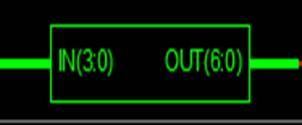

2)数码管显示驱动模块(led.v)实验原理

输入:sum[3:0] -------待显示的数值。

输出:out[6:0] ----------驱动数码管的七位数值(注意下表中out的对应位)。

表 2-1 共阳极数码管驱动模块输入与输出关系表

注:这是一个组合逻辑电路, 可以考虑用 always, 或者 assign 语句设计。

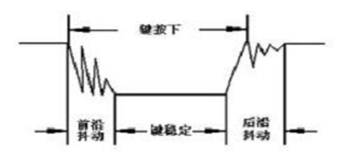

3)消抖模块设计原理

(1)按键抖动产生的原因:

通常的按键所用开关为机械弹性开关, 当机械触点断开、 闭合时, 由于机械触点的弹性作用, 一个按键开关在闭合时不会马上稳定地接通, 在断开时也不会一下子断开。 因而在闭合及断开的瞬间均伴随有一连串的抖动, 为了不产生这种现象而作的措施就是按键消抖。

图2.3按键抖动波形图

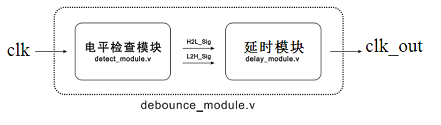

(2)消抖模块原理框图简介

图2.4消抖模块框图

电平检查模块:检测输入的按键是否被按下或者释放, 并分别将 H2L_Sig,L2H_Sig 拉高,

并随后拉低, 给出按键的操作信息。

延时模块:对输入的信号变化时刻进行计时并观察信号的变换情况, 对输出端口进行恰

当地赋值。

二、 实验步骤

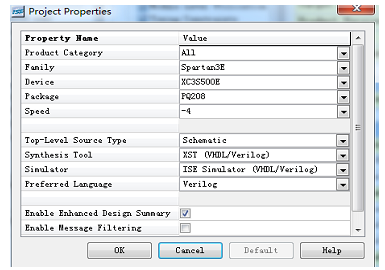

(一)新建一个工程,为工程命名、指定存储路径和目标芯片等。(在 E 盘或者 DATA 盘的根目录下, 以自己的学号为文件名建立工程)。建议工程名、路径名中不要使用中文,file->New Project。

(二)选择 Top-level 的类型是 HDL。

(三)做好器件、EDA工具的正确选择,才能使得正常完成锁定引脚、下载的操作。本次实验中仍采用ISE自带的综合和仿真工具。

图2.5器件和 EDA 工具选择界面

(四)建立新Verilog HDL模块编辑窗口,分别按照十进制计数器(cnt10.v),数码管驱动模块(led.v)的目标要求进行设计,各模块在综合后,采用波形的方式编辑测试激励波形,对相关模块进行功能仿真,实现模块的验证、修正。

注:在编辑测试激励文件时,应考虑测试的完备性。

1)、十进制计数器(cnt10.v)程序代码如下:

module cnt10(CLK,CLR,ENA,COUT,SUM);

input CLK,CLR,ENA;

output [3:0] SUM;

output COUT;

reg [3:0] SUM;

reg COU;

always @(posedge CLK or posedge CLR) begin

if(CLR)

SUM<=4'b0000;

else if(ENA&&SUM==4'd10)

SUM<=4'b0000;

else if(ENA&&SUM<4'd10)

SUM<=SUM+1'b1;

end

always @(posedge CLK or posedge CLR) begin

if(CLR)

COUT<=1'b0;

else if(ENA&&SUM==4'd10)

COUT<=1'b1;

else

COUT<=1'b0;

end

Endmodule

2)、数码管驱动模块(led.v)的程序代码:

module led(IN,OUT);

input[3:0]IN;

output[6:0]OUT;

reg [6:0]OUT;

always @(IN)

begin

case(IN)

4'b0000:OUT<=7'b1000000;

4'b0001:OUT<=7'b1111001;

4'b0010:OUT<=7'b0100100;

4'b0011:OUT<=7'b0110000;

4'b0100:OUT<=7'b0011001;

4'b0101:OUT<=7'b0010010;

4'b0110:OUT<=7'b0000010;

4'b0111:OUT<=7'b1111000;

4'b1000:OUT<=7'b0000000;

4'b1001:OUT<=7'b0010000;

4'b1010:OUT<=7'b0001000;

4'b1011:OUT<=7'b0000011;

4'b1100:OUT<=7'b1000110;

4'b1101:OUT<=7'b0100001;

4'b1110:OUT<=7'b0000110;

4'b1111:OUT<=7'b0001110;

endcase

end

endmodule

(五)用 Verilog HDL 将 cnt10.v 和 led.v 组合为一个模块, 完成综合、 功能仿真, 分形,修正设计。

1)、顶层模块程序代码(cnt10led.v):

`timescale 1ns / 1ps

module cnt10led(CLK_50M,CLK,CLR,ENA,COUT,DATA_OUT);

input CLK_50M,CLK,CLR,ENA;

output COUT;

output[6:0] DATA_OUT;

wire Pin_Out;

wire[3:0] DATA_IN;

//reg COUT;

debounce_module u0( CLK_50M, CLR,CLK, Pin_Out);

cnt10 u1(Pin_Out, CLR, ENA, COUT, DATA_IN);

led u2(DATA_IN, DATA_OUT);

endmodule

注:由于本次设计的时钟周期可以较长,系统对时序没有要求,可以省略个子模块的时序仿真。

(六)拷贝消抖模块代码: debounce_module.v, delay_module.v, detect_module.v,组合完成消抖模块。

1)、detect_module.v程序代码如下:

module detect_module(CLK,RSTn,Pin_In,H2L_Sig,L2H_Sig);

input CLK;

input RSTn;

input Pin_In;

output H2L_Sig;

output L2H_Sig;

parameter T100US = 16'd1999;

reg [10:0]Count1;

reg isEn;

always @ ( posedge CLK or posedge RSTn )

if( RSTn )

begin

Count1 <= 11'd0;

isEn <= 1'b0;

end

else if( Count1 == T100US )

isEn <= 1'b1;

else

Count1 <= Count1 + 1'b1;

reg H2L_F1;

reg H2L_F2;

reg L2H_F1;

reg L2H_F2;

always @ ( posedge CLK or posedge RSTn )

if( RSTn )

begin

H2L_F1 <= 1'b1;

H2L_F2 <= 1'b1;

L2H_F1 <= 1'b0;

L2H_F2 <= 1'b0;

end

else

begin

H2L_F1 <= Pin_In;

H2L_F2 <= H2L_F1;

L2H_F1 <= Pin_In;

L2H_F2 <= L2H_F1;

end

assign H2L_Sig = isEn ? ( H2L_F2 & !H2L_F1 ) : 1'b0;

assign L2H_Sig = isEn ? ( !L2H_F2 & L2H_F1 ) : 1'b0;

Endmodule;

2)、delay_module.v程序代码如下:

module delay_module(CLK, RSTn, H2L_Sig, L2H_Sig, Pin_Out);

input CLK;

input RSTn;

input H2L_Sig;

input L2H_Sig;

output Pin_Out;

parameter T1MS = 25'd19_999;

reg [15:0]Count1;

reg isCount;

reg rPin_Out;

reg [1:0]i;

always @ ( posedge CLK or posedge RSTn )

if( RSTn )

Count1 <= 16'd0;

else if( isCount && Count1 == T1MS )

Count1 <= 16'd0;

else if( isCount )

Count1 <= Count1 + 1'b1;

else if( !isCount )

Count1 <= 16'd0;

reg [3:0]Count_MS;

always @ ( posedge CLK or posedge RSTn )

if( RSTn )

Count_MS <= 4'd0;

else if( isCount && Count1 == T1MS )

Count_MS <= Count_MS + 1'b1;

else if( !isCount )

Count_MS <= 4'd0;

always @ ( posedge CLK or posedge RSTn )

if( RSTn )

begin

isCount <= 1'b0;

rPin_Out <= 1'b0;

i <= 2'd0;

end

else

case ( i )

2'd0 :

if( H2L_Sig ) i <= 2'd1;

else if( L2H_Sig ) i <= 2'd2;

2'd1 :

if( Count_MS == 4'd10 ) begin isCount <= 1'b0; rPin_Out <= 1'b1; i <= 2'd0; end

else isCount <= 1'b1;

2'd2 :

if( Count_MS == 4'd10 ) begin isCount <= 1'b0; rPin_Out <= 1'b0; i <= 2'd0; end

else isCount <= 1'b1;

endcase

assign Pin_Out = rPin_Out;

Endmodule

3)、组合模块(debounce_module.v)程序代码如下:

module debounce_module ( CLK, RSTn, Pin_In, Pin_Out);

input CLK;

input RSTn;

input Pin_In;

output Pin_Out;

wire H2L_Sig;

wire L2H_Sig;

detect_module U1

(

.CLK( CLK ),

.RSTn( RSTn ),

.Pin_In( Pin_In ), // input - from top

.H2L_Sig( H2L_Sig ), // output - to U2

.L2H_Sig( L2H_Sig ) // output - to U2

);

delay_module U2

(

.CLK( CLK ),

.RSTn( RSTn ),

.H2L_Sig( H2L_Sig ), // input - from U1

.L2H_Sig( L2H_Sig ), // input - from U1

.Pin_Out( Pin_Out ) // output - to top

);

endmodule

(七)将消抖模块,十进制计数器模块(cnt10.v),数码管驱动模块(led.v)组合为一个系统。

(八)硬件测试平台设计。

三、实验结果及分析

(一)、完成十进制计数器(cnt10.v)程序代码的编写之后,保存文件,然后对此模块进行综合。

方法为在sources窗口选中待综合模块cnt10,在process窗口双击Synthesize-XST,综合完后可以双击Synthesize-XST下的View RTL Schematic,得到综合后的电路图为:

图1、模块(cnt10)的综合电路图

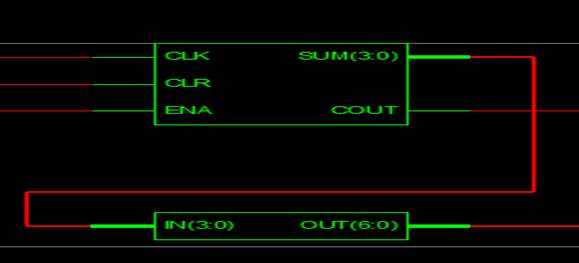

(二)、完成数码管驱动模块(led.v)程序代码的编写之后,然后对此模块进行综合。由(一)同理可得:综合后的(led.v)模块电路图为:

图2、模块(led.v)的综合电路图

(三)、Verilog HDL 将 cnt10.v 和 led.v 组合为一个模块(cnt10led.v)。然后再同理进行综合此模块。得到综合后的电路图为:

图3、模块(cnt10led.v)的综合电路图

(四)、将消抖模块,十进制计数器模块(cnt10.v),数码管驱动模块(led.v)组合为一个系统。然后再对此整体综合模块进行综合,得到整体的综合电路图为:

图4、整体模块的综合电路图

(五)、分析整个过程正确之后,接下来进行引脚锁定,进行引脚锁定处理,加入用户约束文件(*.ucf)文件即可。

(六)双击Implement Design进行布局布线,生成下载文件,载入硬件电路中,即可看到数码管上显示0,按下按键,数字即加1。整个设计过程正确。

四、实验思考题解答(实验指导书要求的思考题)

1、如何用两个或一个 always 实现十进制计数模块? 写出相应代码。

答:程序代码如下:

1)、always @(posedge CLK or posedge CLR)

begin

if(CLR)

begin

SUM=4'b0000;

ADD=1'b0;

end

else

begin

if(ENA)

if(SUM == 4'b1001)

begin

SUM = 4'b0000;

ADD = 1'b1;

end

else

begin

SUM = SUM+1'b1;

ADD = 1'b0;

end

else

begin

SUM = SUM;

ADD = ADD;

end

end

end

endmodule

2)、两个always如下:

always @(CLR)

begin

if(CLR)

flag = 1;

else

flag = 0;

end

always @(posedge CLK)

begin

if(flag)

begin

SUM=4'b0000;

ADD=1'b0;

end

else

begin

if(ENA)

if(SUM == 4'b1001)

begin

SUM = 4'b0000;

ADD = 1'b1;

end

else

begin

SUM = SUM+1'b1;

ADD = 1'b0;

end

else

begin

SUM = SUM;

ADD = ADD;

end

end

end

endmodule

2、如何always,或assign实现数码管的驱动设计?写出相应代码。

答:程序代码如下:

always @(data_in)

begin

begin

case(data_in)

4'b0000: data_out <= 7'b1111110;

4'b0001: data_out <= 7'b0110000;

4'b0010: data_out <= 7'b1101101;

4'b0011: data_out <= 7'b1111001;

4'b0100: data_out <= 7'b0110011;

4'b0101: data_out <= 7'b1011011;

4'b0110: data_out <= 7'b1011111;

4'b0111: data_out <= 7'b1110000;

4'b1000: data_out <= 7'b1111111;

4'b1001: data_out <= 7'b1111011;

4'b1010: data_out <= 7'b1110111;

4'b1011: data_out <= 7'b0011111;

4'b1100: data_out <= 7'b1001110;

4'b1101: data_out <= 7'b0111101;

4'b1110: data_out <= 7'b1001111;

default: data_out <= 7'b1000111;

endcase

end

end

3、比较实验一与实验二的实验过程,说明原理图的输入法与HDL输入法的不同应用环境。

答:通过做实验一和实验二,通过比较可以得出:实验一中应用的是原理图完成十进制计数器的显示,而原理图输入法比较直观,便于我们理解,但是在做的过程中,工作量相对较大,需要反复绘制八张原理图,所以原理图设计比较适合相对简单的电路,门电路较少的电路;在实验二中是通过应用HDL语言描述,在设计过程中,可以按功能分成多个模块,按我们的需要进行调用,并且还有利于自顶向下的设计。所以适用于较复杂的电路。

4、CHIPSCOPE调试和仿真有何区别?

答:CHIPSCOPE是一款调试阶段的调试工具(逻辑分析仪),它在工程里加入采集数据的内核,当程序下载到芯片里运行时,它可以采集要观察到的信号并在计算机上显示出来,与功能仿真不同,它只能检查局部,针对部分“出问题”的地方的检验,这个过程必须设计FPGA硬件。

五、体会

通过上一次实验的操作训练。因而本次实验中对软件的操作就比较熟悉了,通过本次试验,虽然完成的功能和实验一类似,但是完成的过程却不一样,在本次实验中,操作最多的就是写代码了,用HDL语言来完成十进制计数器及显示的功能,感受最深的就是程序代码的书写,感觉跟以前学的C语言有一定的差别,C语言中是用函数构成的,而HDL语言是由module模块组成的,对各个模块按需调用。针对第一次试验过程,本次实验过程较为简单了许多,虽然完成的是同一个功能,但是是分别从两个方面进行完成的,实验一中应用的是原理图完成十进制计数器的显示,需要绘制多个原理图,过程原理虽简单但操作比较繁琐,通过本次实验过后,用HDL语言来实现此功能,变得更加简单,所以学号HDL语言对我们来说是至关重要的,同时还有利于我们对FPGA这门课程的理解以及学习。