集成门电路功能测试实验报告

一、 实验预习

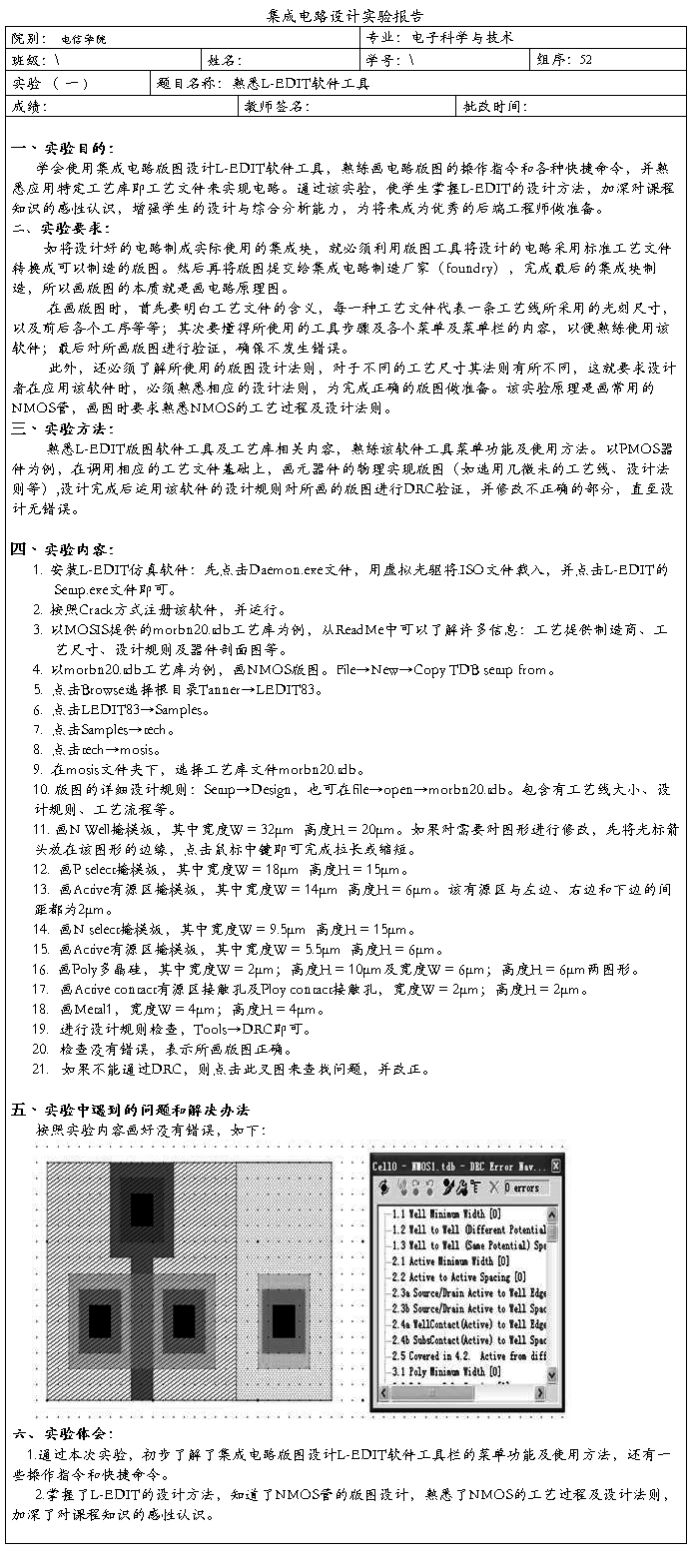

1. 逻辑值与电压值的关系。

2. 常用逻辑门电路逻辑功能及其测试方法。

3. 硬件电路基础实验箱的结构、基本功能和使用方法。

二、 实验目的

测试集成门电路的功能

三、 实验器件

集成电路板、万用表

四、 实验原理

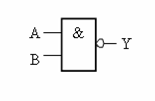

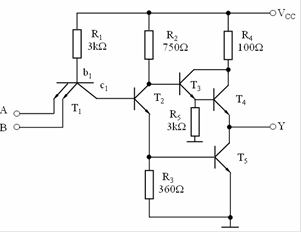

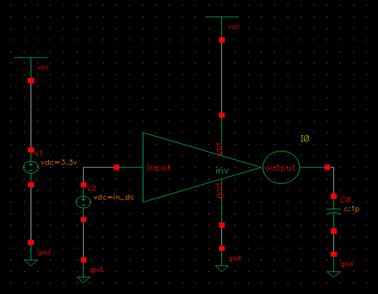

TTL与非门74LS00的逻辑符号及逻辑电路:

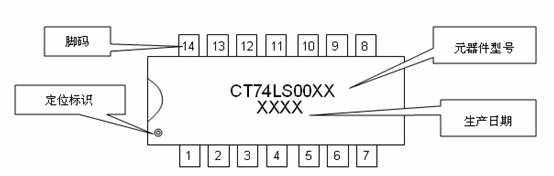

双列直插式集成与非门电路CT74LS00:

数字电路的测试:

常对组合数字电路进行静态和动态测试,静态测试是在输入端加固定的电平信号,测试输出壮态,验证输入输出的逻辑关系。动态测试是在输入端加周期性信号,测试输入输出波形,测量电路的频率响应。常对时序电路进行单拍和连续工作测试,验证其状态的转换是正确。本实验验证集成门电路输入输出的逻辑关系,实验在由硬件电路基础实验箱和相关的测试仪器组成的物理平台上进行。

硬件电路基础实验箱广泛地应用于以集成电路为主要器件的数字电路实验中,它的主要组成部分有:

(1) 直流电源:提供固定直流电源(+5V,-5V)和可调电源(+3~15V,-3~15V)。

(2) 信号源:单脉冲源(正负两种脉冲);连续脉冲。

(3) 逻辑电平输出电路:通过改变逻辑电平开关状态输出两个电平信号:高电平“1”和低电平“0”。

(4) 逻辑电平显示电路:电平显示电路由发光二极管及其驱动电路组成,用来指示测试点的逻辑电平。

(5) 数码显示电路:动态数码显示电路和静态数码显示电路,静态数码显示电路由七段LED数码管及其译码器组成。

(6) 元件库:元件库装有电位器、电阻、电容、二极管、按键开关等器件。

(7) 插座区与管座区:可插入集成电路,分立元件。

…… …… 余下全文

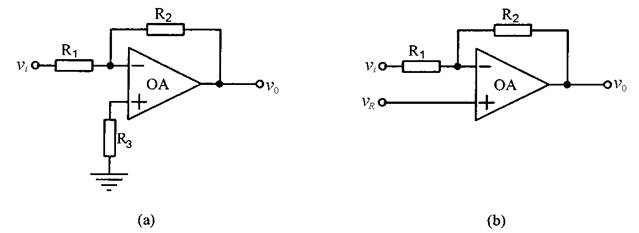

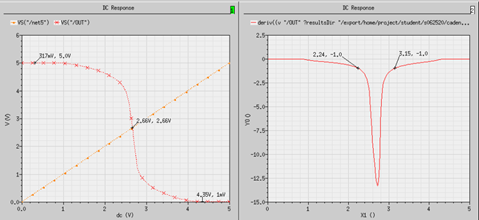

输入输出关系:

输入输出关系:

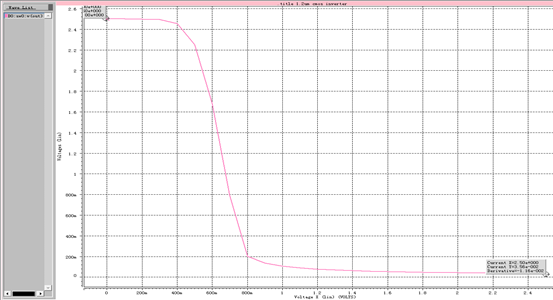

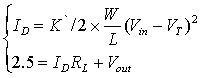

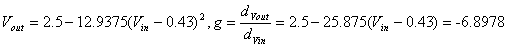

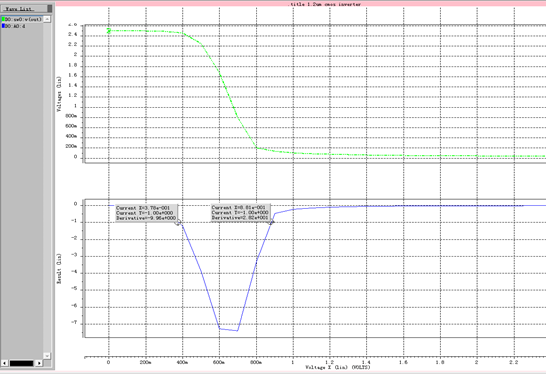

,器件实际工作在线性区

,器件实际工作在线性区

,

,  ,

,

0.04633V

0.04633V

时,NMOS 工作在饱和区

时,NMOS 工作在饱和区

0.7932

0.7932

、

、 、

、 、

、 、

、 。

。

、输出低电平

、输出低电平 、输入高电平

、输入高电平 、输入低电平

、输入低电平 、阈值电压

、阈值电压 。所以,噪声容限为:

。所以,噪声容限为: