ЪЕбщБЈИц

вЛЁЂЪЕбщУћГЦ

ОВЬЌЫцЛњДЂДцЦїЪЕбщ

ЖўЁЂЪЕбщФПЕФ

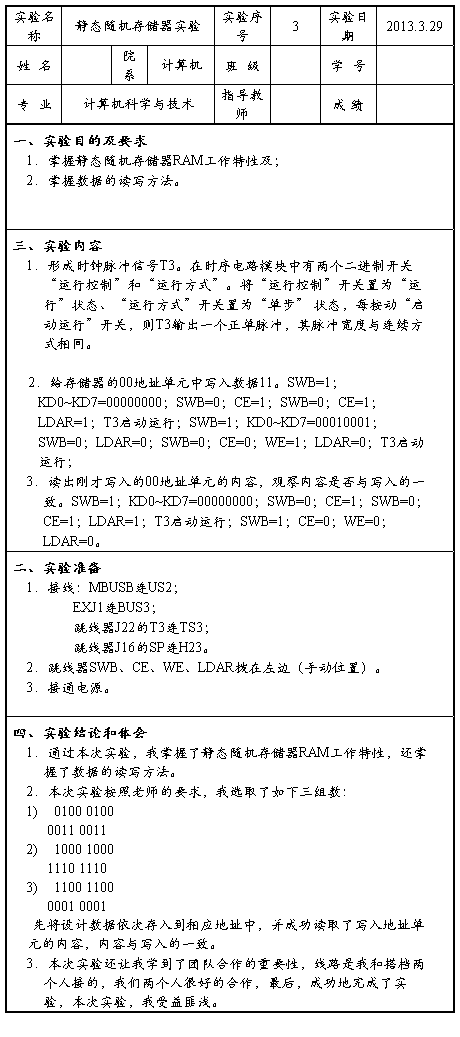

еЦЮеОВЬЌЫцЛњДЂДцЦїRAMЕФЙЄзїЬиадКЭЪ§ОнЕФЖСаДЗНЗЈ

Ш§ЁЂЪЕбщЩшБИ

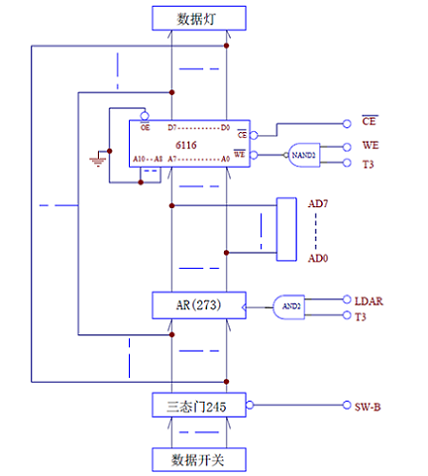

TDN-CM++МЦЫуЛњзщГЩдРэНЬбЇЪЕбщЯЕЭГвЛЬзЃЌЕМЯпШєИЩЁЃ

ЫФЁЂЪЕбщдРэ

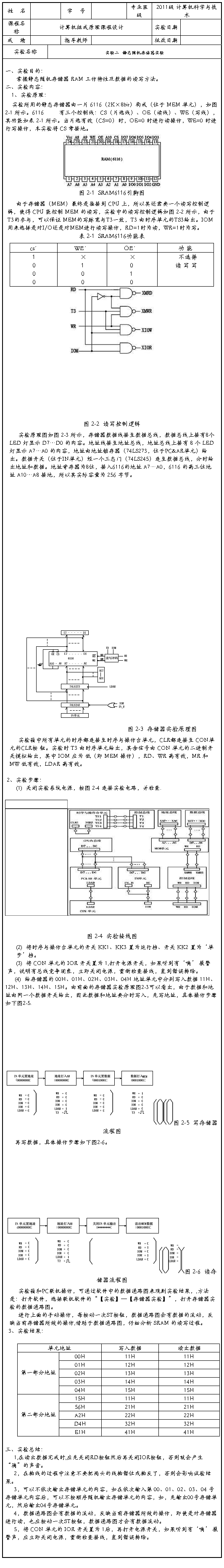

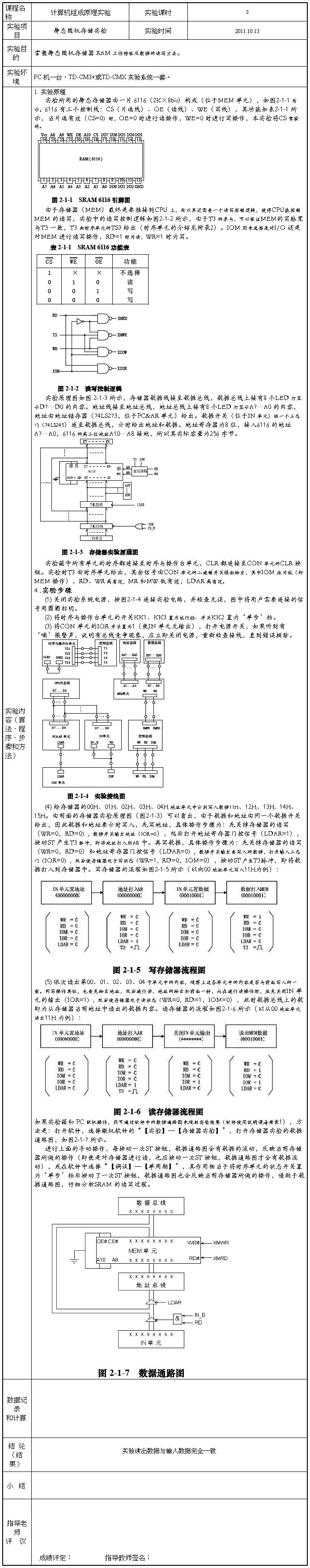

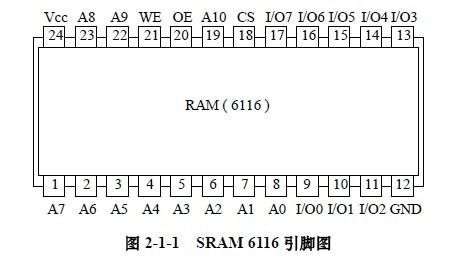

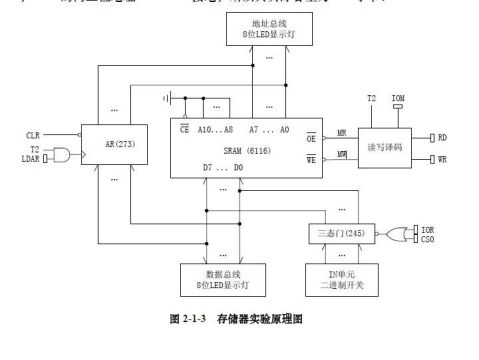

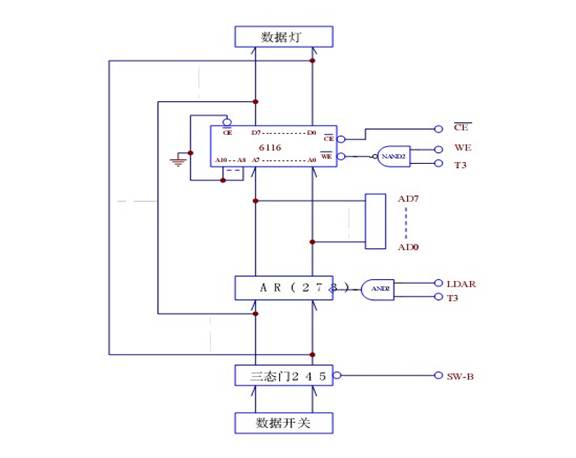

ЪЕбщЫљгУЕФАыЕМЬхОВЬЌДцДЂЦїЕчТЗдРэШчЭМ1ЫљЪОЃЌЪЕбщжаЕФОВЬЌДцДЂЦїгЩвЛЦЌ6116(2K×8)ЙЙГЩЃЌЦфЪ§ОнЯпНгжСЪ§ОнзмЯпЃЌЕижЗЯпгЩЕижЗЫјДцЦї(74LS273)ИјГіЁЃЕижЗЕЦADO~AD7гыЕижЗЯпЯрСЌЃЌЯдЪОЕижЗЯпФкШнЁЃЪ§ОнПЊЙиОШ§ЬЌУХ(74LS245)СЌжСЪ§ОнзмЯпЃЌЗжЪБИјГіЕижЗКЭЪ§ОнЁЃ

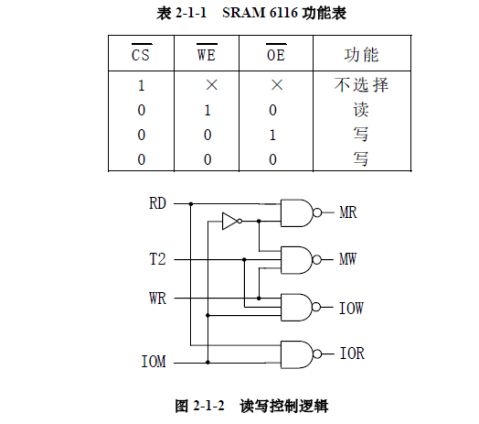

вђЕижЗМФДцЦїЮЊ8ЮЛЃЌНгШы6116ЕФЕижЗA7--AOЃЌЖјИпШ§ЮЛA8ЁЊA1OНгЕиЃЌЫљвдЦфЪЕМЪШнСПЮЊ256зжНкЁЃ6116гаШ§ИіПижЦЯпЃКCE(ЦЌбЁЯп)ЁЂ0E(ЖСЯп)ЁЂWE(аДЯп)ЁЃЕБЦЌбЁгааЇ(CE=O)ЪБЃЌOE=OЪБНјааЖСВйзїЃЌWE=0ЪБНјаааДВйзїЁЃБОЪЕбщжаНЋ0EГЃНгЕиЃЌвђДЫ6116ЕФв§НХаХКХWE=1ЪБНјааЖСВйзїЃЌ WE=0ЪБНјаааДВйзїЁЃ

дкДЫЧщПіЯТЃЌвЊЖдДцДЂЦїНјааЖСВйзїЃЌБиаыЩшжУПижЦЖЫCE=OЁЂWE=OЃЌЭЌЪБгаT3ТіГхЕНРДЃЌвЊЖдДцДЂЦїНјаааДВйзїЃЌБиаыЩшжУПижЦЖЫCE=OЁЂWE=1ЃЌЭЌЪБгаT3ТіГхЕНРДЃЌЦфЖСаДЪБМфгыT3ТіГхПэЖШвЛжТЁЃ

ЪЕбщЪБНЋT3ТіГхНгжСЪЕбщАхЩЯЪБађЕчТЗФЃПщЕФTS3ЯргІВхПзжаЃЌЦфТіГхПэЖШПЩЕїЃЌЦфЫќЕчЦНПижЦаХКХгЩЁАSWITCH UNITЁБЕЅдЊЕФЖўНјжЦПЊЙиФЃФтЃЌЦфжаSW-BЮЊЕЭЕчЦНгааЇЃЌLDARЮЊИпЕчЦНгааЇЁЃ

ЭМ1 ДцДЂЦїЪЕбщдРэЭМ

ЭМ1 ДцДЂЦїЪЕбщдРэЭМ

ЁЁ ЁЁ грЯТШЋЮФ