数字钟实验报告

数字钟实验报告

课题名称:数字钟的设计与制作

组员:王庆刘盛清杨隽

姚琦邱健斌

姓名:

班级:电气信息I类112班

实验时间:

实验时间:

实验地点:

实验地点:

指导老师:

目录

一、实验目的--------------------------------------------------------------------------------------------------------------3

二、实验任务及要求-----------------------------------------------------------------------------------------------------3

三、实验设计内容--------------------------------------------------------------------------------------------------------3

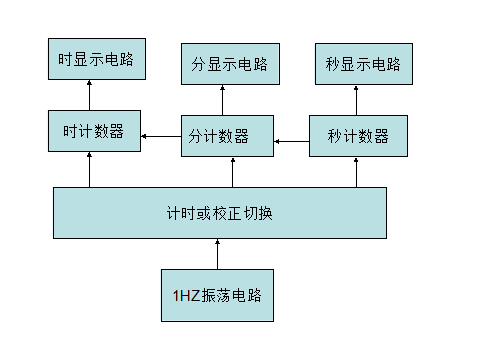

(一)、设计原理及思路---------------------------------------------------------------------------------------------3

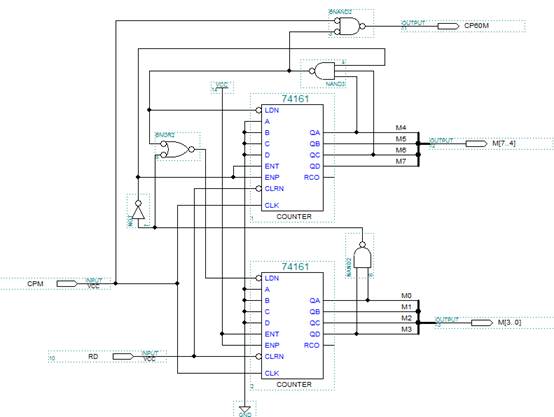

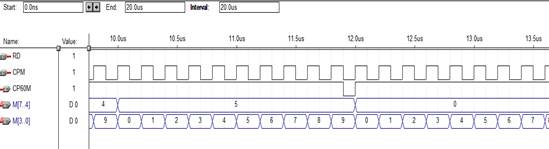

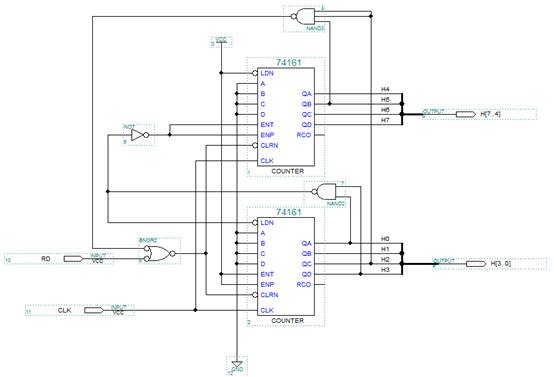

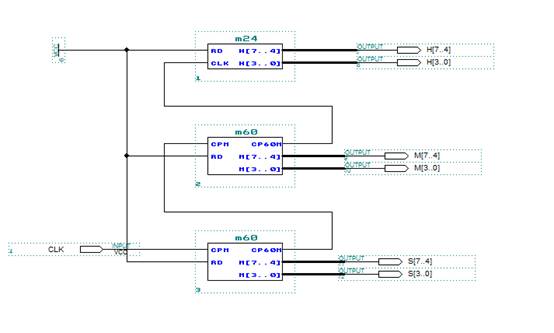

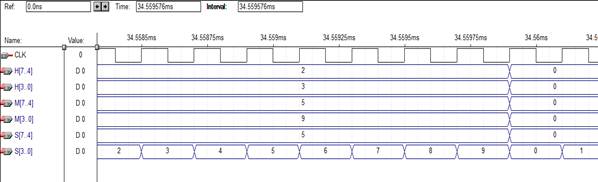

(二)、数字钟电路的设计 ----------------------------------------------------------------------------------------4

(1)电路组成------------------------------------------------------------------------------------------------------4

…… …… 余下全文