实验题目

实验报告正文一律使用A4打印纸打印或手写,页眉上标明“《XXXX》课程实验”字样。页面设置上边距2.5cm,下边距2 cm,右边距2 cm(左装订),多倍行距1.25倍。正文用宋体5号字,页眉和页脚同宋体小5号字并居中。

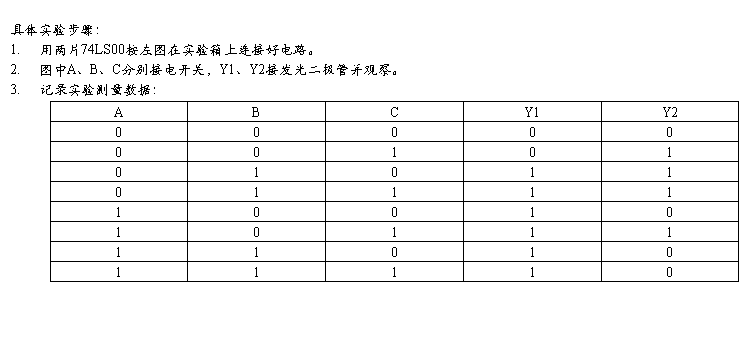

1、 实验内容

用MAX+plus II 10.1设计一位全加器

2、 实验目的与要求

设计一位全加器,并且熟悉MAX+plus II 10.1使用环境。

3、 实验环境

MAX+plus II 10.1

4、 设计思路分析(包括需求分析、整体设计思路、概要设计)

用两个半加器和一个或门,设计一位全加器。

5、 详细设计

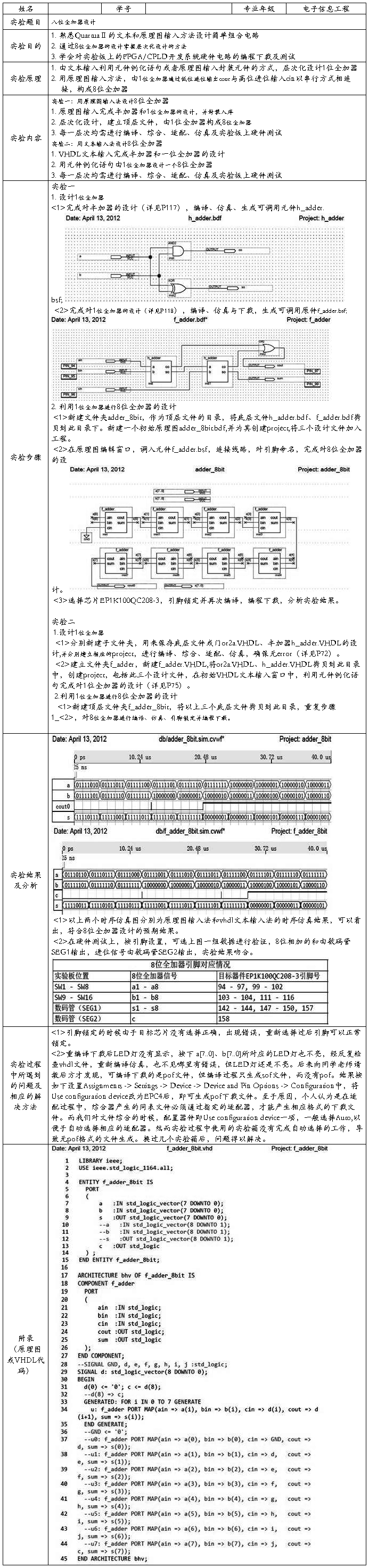

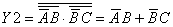

一位全加器可以用两个半加器和一个或门连接而成,半加器由一个与门,一个非门,同或门来实现。

在MAX+plus II 10.1环境操作步骤如下:

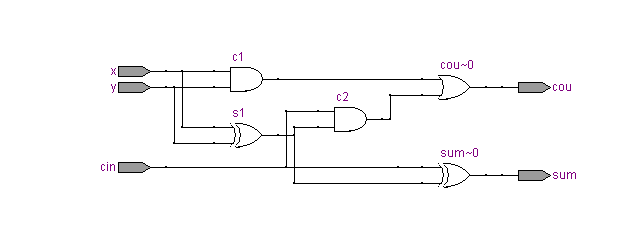

1、半加器的设计 2、全加器的设计 3、分配管脚 4、编译

5、仿真 6、下载 7、观察结果

6、 实验结果与分析

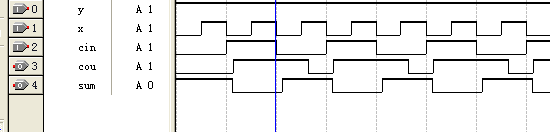

…… …… 余下全文

南昌大学实验报告

南昌大学实验报告