改进型电容三点式振荡电路的设计

摘要

高频信号发生器主要用来向各种电子设备和电路提供高频能量或高频标准信号,以便测试各种电子设备和电路的电气特性。

高频信号发生器主要是产生高频正弦振荡波,故电路主要是由高频振荡电路构成。振荡器的功能是产生标准的信号源,广泛应用于各类电子设备中。为此,振荡器是电子技术领域中最基本的电子线路,也是从事电子技术工作人员必须要熟练掌握的基本电路。

本次课设设计了改进型电容三点式高频振荡器,介绍了设计步骤,比较了各种设计方法的优缺点,总结了不同振荡器的性能特征。使用Protel2004DXP制作PCB板,并使用环氧树脂铜箔板和FeCl3进行了制板和焊接。使用实验要求的电源和频率计进行验证,实现了设计目标。

1 实验原理

1.1 振荡的原理

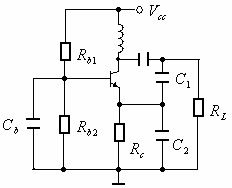

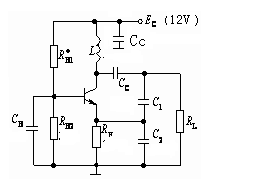

三点式LC正弦波振荡器的组成法则(相位条件)是:与晶体管发射极相连的两个电抗元件应为同性质的电抗,而与晶体管集电极—基极相连的电抗元件应与前者性质相反。图1-1所示为满足组成法则的基本电容反馈LC振荡器共基极接法的典型电路。当电路参数选取合适,满足振幅起振条件时,电路起振。当忽略负载电阻、晶体管参数及分布电容等因素影响时,振荡频率 可近似认为等于谐振回路的固有振荡频率

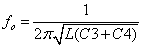

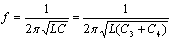

可近似认为等于谐振回路的固有振荡频率 ,即

,即

(1)

(1)

式中  近似等于

近似等于 与

与 的串联值

的串联值

(2)

(2)

图1-1 电容反馈LC振荡器

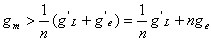

由图1-1所画出的分析起振条件的小信号等效电路如图1-2所示。

图1-2 分析起振条件的小信号等效电路

由图1-2分析可知,振荡器的起振条件为:

(3)

(3)

式中

为LC振荡回路的等效谐振电阻;

为LC振荡回路的等效谐振电阻;

电路的反馈系数  (4)

(4)

由式(3)看出,由于晶体管输入电阻 对回路的负载作用,反馈系数

对回路的负载作用,反馈系数 并不是越大越容易起振,反馈系数太大会使增益A降低,且会降低回路的有载

并不是越大越容易起振,反馈系数太大会使增益A降低,且会降低回路的有载 值,使回路的选择性变差,振荡波形产生失真,频率稳定性降低;所以,在晶体管参数一定的情况下,可以调节负载和反馈系数,保证电路起振。

值,使回路的选择性变差,振荡波形产生失真,频率稳定性降低;所以,在晶体管参数一定的情况下,可以调节负载和反馈系数,保证电路起振。 的取值一般在0.1—0.5 之间。

的取值一般在0.1—0.5 之间。

图1所示的振荡器,由于晶体管各电极直接和振荡回路元件L、 、

、 并联,而晶体管的极间电容(主要是结电容)又随外界因素(如温度、电压、电流等)的变化而变化,因此振荡器的频率稳定性不够高。为了提高振荡器的频率稳定性,实际中更多的采用能够减小晶体管与回路之间耦合的改进型电容反馈振荡器。

并联,而晶体管的极间电容(主要是结电容)又随外界因素(如温度、电压、电流等)的变化而变化,因此振荡器的频率稳定性不够高。为了提高振荡器的频率稳定性,实际中更多的采用能够减小晶体管与回路之间耦合的改进型电容反馈振荡器。

1.2 电容三点式振荡器

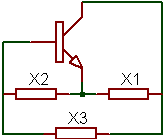

电容三点式振荡器的基本电路如图1-3所示

图2-1电容三点式振荡器

由图可见:与发射极连接的两个电抗元件为同性质的容抗元件C1和C2;与基极和集电极连接的为异性质的电抗元件L,根据前面所述的判别准则,该电路满足相位条件。

其工作过程是:振荡器接通电源后,由于电路中的电流从无到有变化,将产生脉动信号,因任一脉冲信号包含有许多不同频率的谐波,因振荡器电路中有一个LC谐振回路,具有选频作用,当LC谐振回路的固有频率与某一谐波频率相等时,电路产生谐振。虽然脉动的信号很微小,通过电路放大及正反馈使振荡幅度不断增大。当增大到一定程度时,导致晶体管进入非线性区域,产生自给偏压,使放大器的放大倍数减小,最后达到平衡,即AF=1,振荡幅度就不再增大了。于是使振荡器只有在某一频率时才能满足振荡条件,于是得到单一频率的振荡信号输出。该振荡器的振荡频率 为:

为:

反馈系数F为:

若要它产生正弦波,必须满足F= 1/2-1/8,太小不容易起振,太大也不容易起振。一个实际的振荡电路,在F确定之后,其振幅的增加主要是靠提高振荡管的静态电流值。但是如静态电流取得太大,振荡管工作范围容易进入饱和区,输出阻抗降低使振荡波形失真,严重时,甚至使振荡器停振。所以在实用中,静态电流值一般ICO=0.5mA-4mA。

电容三点式振荡器的优点是:1)振荡波形好。2)电路的频率稳定度较高。工作频率可以做得较高,可达到几十MHz到几百MHz的甚高频波段范围。

电路的缺点:振荡回路工作频率的改变,若用调C1或C2实现时,反馈系数也将改变。使振荡器的频率稳定度不高。

2 改进型电容三点式振荡电路设计

电容三点式课分为三种:考毕兹振荡器、克拉泼振荡器、西勒振荡器。

2.1 考毕兹振荡器

电容三点式振荡器(又称考毕兹振荡器)如图2-1所示。

电容三点式振荡器(又称考毕兹振荡器)如图2-1所示。

图 2-1考毕兹振荡器

理论计算振荡器的频率为:

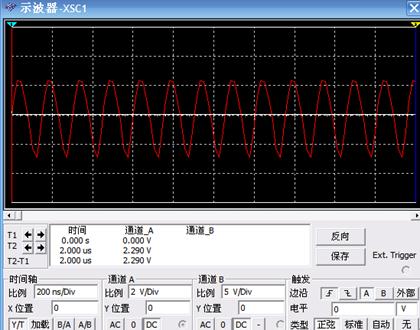

观察到的振荡波形如图2-2所示

从波形看出其震荡极不稳定,测试其波形频率为f 6.5MHz

6.5MHz

调解C1C2改变频率时,反馈系数也改变。由于极间电容对反馈振荡器的回路电抗均有影响,所以对振荡器频率也会有影响。而极间电容受环境温度、电源电压等因素的影响较大,所以电容三点式振荡器的频率稳定度不高。为克服共基电容三点式振荡器的缺点,可对其进行改进,即克拉泼电路和西勒电路。

图2-2考毕兹振荡器输出信号波形

2.2 串联型改进电容三端式振荡器(克拉泼电路)

电容三点式改进型“克拉泼振荡器”如图2-3所示。

图2-3 克拉泼振荡电路

电路特点是在共基电容三点式振荡器的基础上,用一电容C3,串联于电感L支路。

功用主要是以增加回路总电容和减小管子与回路间的耦合来提高振荡回路的标准性。使振荡频率的稳定度得以提高。

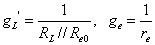

因为C3为可调电容远小于C1或C2,所以电容串联后的等效电容约为C3。电路的振荡频率为:

与共基电容三点式振荡器电路相比,在电感L支路上串联一个电容。但它有以下特点:

1、振荡频率改变可不影响反馈系数;

2、振荡幅度比较稳定。

3、电路中C3为可变电容,调整它即可在一定范围内调整期振荡频率。

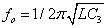

但C3不能太小,否则导致停振,所以克拉泼振荡器频率覆盖率较小,仅达1.2-1.4; 为此,克拉泼振荡器适合与作固定频率的振荡器 。观察到的振荡波形如图2-4所示

图2-4克拉波振荡器输出信号波形

改进后的电路波形比原电容三点式振荡器稳定度高了很多,这是因为晶体管一部分接入的形式与回路连接,接入系数p越小,耦合越弱。减弱了晶体管对回路的影响。

2.3 西勒振荡器

电容三点式的改进型“西勒振荡器”如图2-5所示

图2-5西勒振荡器

电路特点是在克拉泼振荡器的基础上,用一电容C4,并联于电感L两端。功用是保持了晶体管与振荡回路弱藕合,振荡频率的稳定度高,调整范围大。电路的振荡频率为:

特点:1.振荡幅度比较稳定; 2.振荡频率可以比较高,如可达千兆赫;频率覆盖率比较大,可达1.6-1.8;所以在一些短波、超短波通信机,电视接收机中用的比较多。

频率稳定度是振荡器的一项十分重要技术指标,它表示在一定的时间范围内或一定的温度、湿度、电压、电源等变化范围内振荡频率的相对变化程度,振荡频率的相对变化量越小,则表明振荡器的频率稳定度越高。

改善振荡频率稳定度,从根本上来说就是力求减小振荡频率受温度、负载、电源等外界因素影响的程度,振荡回路是决定振荡频率的主要部件。因此改善振荡频率稳定度的最重要措施是提高振荡回路在外界因素变化时保持频率不变的能力,这就是所谓的提高振荡回路的标准性。

提高振荡回路标准性除了采用稳定性好和高Q的回路电容和电感外,还可以采用与正温度系数电感作相反变化的具有负温度系数的电容,以实现温度补偿作用。

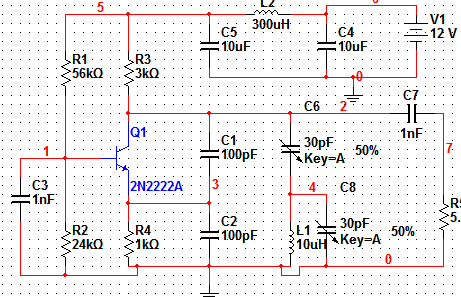

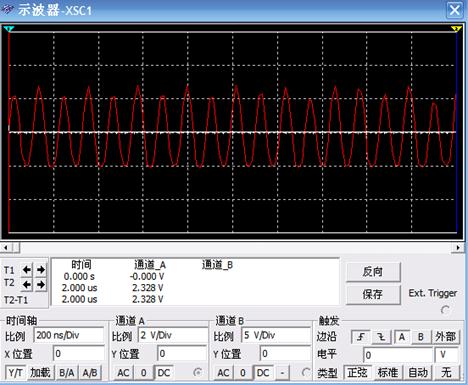

输出信号的幅值、频率等用实时监测法测试,信号波形如图2-6所示,调整C6、C3观测震荡信号的波形和频率变化。

图2-6西勒振荡器输出信号波形

3 改进型电容三点式电路设计

3.1 电路选择

从以上的讨论,分析不同振荡电路的性能指标及电路复杂程度。

采用西勒振荡电路,因为西勒振荡器的接入系数与克拉泼振荡器的相同,由于改变频率主要通过C4完成的,C4的改变并不影响接入系数p,所以波段内输出较平稳。而且C4改变,频率变化较明显,故西勒振荡器的频率覆盖系数较大,可达1.6~1.8。

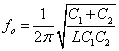

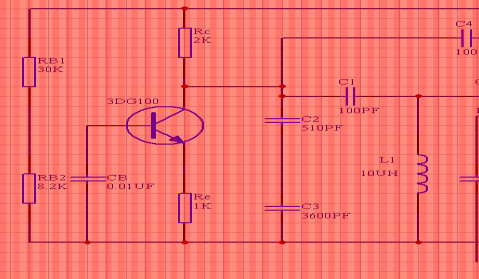

3.2 原理图设计

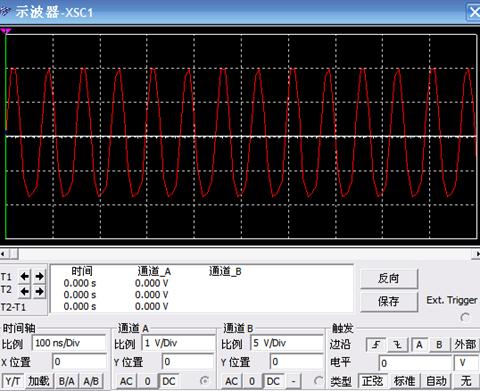

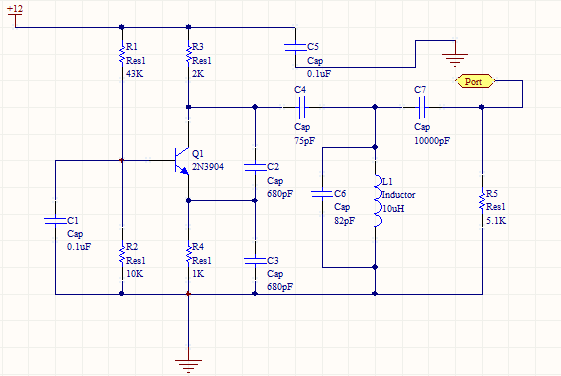

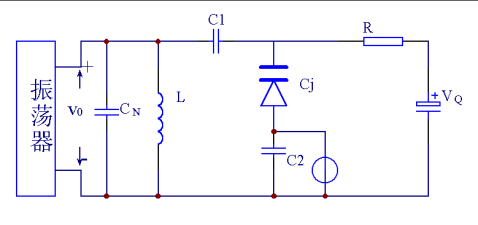

图3-1 改进型电容三点式振荡电路原理图

3.2.1 电路结构

总的电路结构如图3-1所示。

电路由三部分组成

1 三极管放大器;(起能量控制作用)

2 正反馈网络;(由三点式回路组成)

3 选频网络;(由三点式回路的谐振特性完成选频功能)。

3.2.2 静态工作点的设置

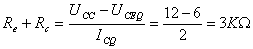

合理地选择振荡器的静态工作点,对振荡器的起振,工作的稳定性,波形质量的好坏有着密切的关系。-般小功率振荡器的静态工作点应选在远离饱和区而靠近截止区的地方。根据上述原则,一般小功率振荡器集电极电流ICQ大约在0.8-4mA之间选取,故本实验电路中:

选ICQ=2mA VCEQ=6V β=100

则有

则有

为提高电路的稳定性Re值适当增大,取Re=1KΩ则Rc=2KΩ

因:UEQ=ICQ·RE 则: UEQ =2mA×1K=2V

因: IBQ=ICQ/β 则: IBQ =2mA/100=0.02mA

一般取流过Rb2的电流为5-10IBQ , 若取10IBQ

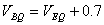

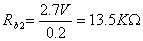

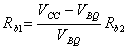

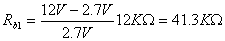

因:

则: 取标称电阻12K?。

则: 取标称电阻12K?。

因:

因:

3.2.3 选管

由于高频振荡器的振荡频率较高,在选管时应注意选超高频小功率三极管。特征频率fT也要比音频振荡管的要求高。通常选fT> (3-10) f0 (f0为振荡器的中心频率)。fT高则管子的高频性能好,晶体管内部相移小,有利于稳频。在高频工作时,振荡器的增益仍较大,易于起振。本次课设选用9014 NPN型号的晶体管,满足了振荡器的频率和功率要求。

3.2.4 振荡回路元件的确定

回路中的各种电抗元件都可归结为总电容C和总电感L两部分。确定这些元件参量的方法,是根据经验先选定一种,而后按振荡器工作频率再计算出另一种电抗元件量。从原理来讲,先选定哪种元件都一样,但从提高回路标准性的观点出发,以保证回路电容Cp远大于总的不稳定电容Cd原则,先选定Cp为宜。若从频率稳定性角度出发,回路电容应取大一些,这有利于减小并联在回路上的晶体管的极间电容等变化的影响。但C不能过大,C过大,L就小,Q值就会降低,使振荡幅度减小,为了解决频稳与幅度的矛盾,通常采用部分接入。反馈系数F=C1/C2,不能过大或过小,适宜1/8—1/2。

因振荡器的工作频率为:

因振荡器的工作频率为:

当LC振荡时,f0=4MHz L=10μH

本电路中,则回路的谐振频率fo主要由C4、C6决定,即

有

有

取C4 =75pf,C6=82pf,因要遵循C2,C3>>C4,C6,C2/C3=1/8—1/2的条件,故取C2=680pf,则C3=680pf。

对于晶体振荡,只需和晶体并联一可调电容进行微调即可。

为了尽可能地减小负载对振荡电路的影响,振荡信号应尽可能从电路的低阻抗端输出。例如发射极接地的振荡电路,输出宜取自基极;如为基级接地,则应从发射极输出。

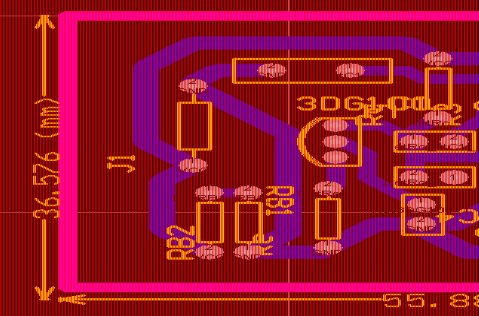

3.3 印制PCB电路板

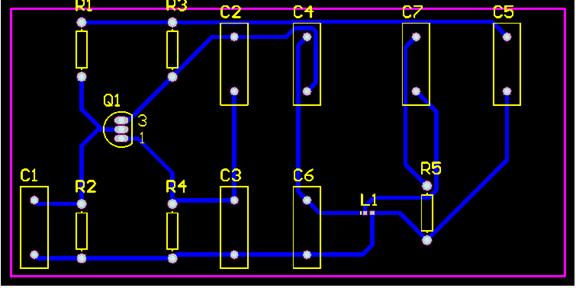

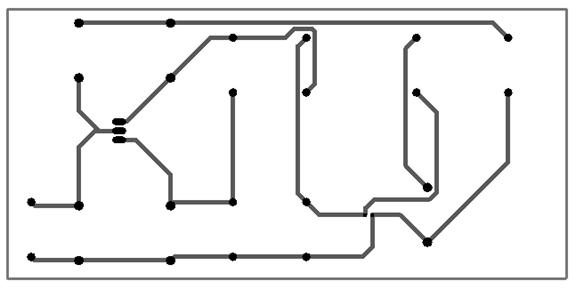

使用Protel2004DXP完成原理图的设计之后,可以生成PCB电路板,本电路板采用自动布线设计,电路板见图3-2。

图3-2 改进型电容三点式振荡电路PCB图

3.3.1 转印、腐蚀、焊接电路板

在Protel中选择:文件à页面设置à高级àtop Overlayà隐藏所有元件。将生成的线路图(图3-3)按照1:1的比例打印在转印纸上。

图3-3 印制线路图

使用热转印机将图3-3印制在环氧树脂铜箔板上,使用FeCl3溶液进行腐蚀。腐蚀之后按照焊点打孔,之后按照元件位置焊接相应元件。

4 结论

按照PCB电路板相应的位置接入+12V电源,在C7的一端接频率计,观察频率计的读数,可发现振荡频率在3.8~4.2MHz附近浮动,在误差允许范围内符合本电路设计的4MHz的设计要求。

振荡电路接通电源后,有时不起振,或者在外界信号强烈触发下才起振(硬激励),在波段振荡器中有时只在某一频段振荡,而在另一频段不振荡等。所有这些现象无非是没有满足相位平衡条件或振幅平衡条件。如果在全波段内不振荡,首先要看相位平衡条件是否满足。对三端振荡电路要看是否满足对应的相位平衡判断标准。此外,还要在振幅平衡条件所包含的各种因素中找原因。

1、静态工作点选的太小。

2、电源电压过低,使振荡管放大倍数太小。

3、负载太重,振荡管与回路间耦合过紧,回路Q值太低。

4、回路特性阻抗ρ或介入系数pce太小,使回路谐振阻抗RO太低。

5、反馈系数kf太小,不易满足振幅平衡条件。但kf并非越大越好,应适当选取。

有时在某一频段内高频端起振,而低频端不起振,这多半是在用调整回路电容来改变振荡频率的电路中,低端由于C增大而L/C下降,致使写真阻抗降低所起。反之,有时低端振高端不振,原因可能有:

1、选用晶体管fT不够高。

2、管的电流放大倍数β太小。

第二篇:三点式LC正弦波振荡器

***************学校

高频电子线路

课程设计报告

设计题目: 三点式LC正弦波振荡器 系 部:

专 业:

班 级:

学生姓名:

学 号:

成 绩:

20xx年 月

“高频电子线路”课程设计任务书

1.时间:20xx年06月6日~20xx年06月10日

2. 课程设计单位:***************学校

3. 课程设计目的:掌握“高频电子线路”课程的基本概念、基本原理,加深对高频电子系统的工作原理和电路调试方法的理解。

4. 课程设计任务:

①了解电路图绘制软件的相关常识及其特点;

②熟悉电路图绘制软件的使用方法;

③理解高频电子系统的布局布线规则;

④作好实习笔记,对自己所发现的疑难问题及时请教解决;

⑤联系自己专业知识,熟练设计高频电子线路的,总结自己的心得体会; ⑥参考相关的的书籍、资料,认真完成实训报告。

⑦作好笔记,对自己所发现的疑难问题及时请教解决;

⑧联系自己所学知识,总结本次设计经验;

⑨认真完成课程设计报告。

高频课程设计报告

2

前言:

振荡器是不需外信号激励、自身将直流电能转换为交流电能的装置。凡是可以完成这一目的的装置都可以作为振荡器。

一个振荡器必须包括三部分:放大器、正反馈电路和选频网络。放大器能对振荡器输入端所加的输入信号予以放大使输出信号保持恒定的数值。正反馈电路保证向振荡器输入端提供的反馈信号是相位相同的,只有这样才能使振荡维持下去。选频网络则只允许某个特定频率 f0能通过,使振荡器产生单一频率的输出。

振荡器能不能振荡起来并维持稳定的输出是由以下两个条件决定的;一个是反馈电压 Uf 和输入电压 Ui 要相等,这是振幅平衡条件。二是Uf 和Ui 必须相位相同,这是相位平衡条件,也就是说必须保证是正反馈。一般情况下,振幅平衡条件往往容易做到,所以在判断一个振荡电路能否振荡,主要是看它的相位平衡条件是否成立。

振荡器的用途十分广泛,它是无线电发送设备的心脏部分,也是超外差式接收机的主要部分各种电子测试仪器如信号发生器、数字式频率计等,其核心部分都离不开正弦波振荡器。功率振荡器在工业方面(例如感应加热、介质加热等)的用途也日益广阔。

正弦波是电子技术、通信和电子测量等领域中应用最广泛的波形之一。能够产生正弦波的电路称为正弦波振荡器。通常,按工作原理的不同,正弦振荡器分为反馈型和负载型两种,前者应用更为广泛。在没有外加输入信号的条件下,电路自动将直流电源提供的能量转换为具有一定频率、一定波形和一定振幅的交变振荡信号输出。

课程设计报告:

一、设计方案

电路基本原理

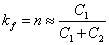

LC调频振荡器的电路由LC正弦波振荡器与变容二极管调频电路所组成,其中晶体管VT组成电容三点式振荡器。VT接成共基组态 C(B)为基极耦合电容。VT的静态工作点由R(B1)、R(B2)、R(E)及R(C)所决定,即:

U(BQ)=R(B2)Ucc/[R(B1)+R(B2)] (1) U(EQ)=U(BQ)-U(BE)≈I(CQ)R(E) (2) 3

I(CQ)=[Ucc-U(CEQ)]/[R(B)+R(C)] (3) I(BQ)=I(CQ)/β (4) I(CQ)一般为1~4mA。I(CQ)偏大,振荡幅度增加,但波形失真加重,频率稳定性变差。L1、C1与C2、C3组成并联谐振回路,其中C3两端的电压构成振荡器的反馈电压U(BE),以满足相位平衡条件∑ф=2n。比值C2/C3=F决定反馈电压的大小,当A(VO)=1时,振荡器满足振荡平衡条件,电路的起振条件为A(VO)F>1。为减小晶体管的极间电容对回路振荡频率的影响,C2、C3的取值要大。如果选C1〈〈C2,C1〈〈C3,则回路的谐振频率f0主要由C1决定,即:

f0=1/2π√L1C1 如果取C1为几十皮法,C2、C3可取几百皮法至几千皮法。反馈系数F一般取1/2~1/8。调频电路由变容二极管VD(C)及耦合电容Cc组成,R1与R2为变容二极管提供静态时的反向支流偏置电压U(Q),即U(Q)=[R2/(R1-R2)]Ucc。电阻R3称为隔离电阻,常取R3〉〉R2,R2〉〉R1,以减小调制信号u(Ω)对U(Q)的影响。C5与高频扼流圈L2给u(Ω)提供通路,C6起高频滤波作用。 变容二极管VDc通过Cc部分接入振荡回路,有利于提高主振荡频率f0的稳定性, 减小调制失真。变容管部分接入振荡回路的等效电路,接入系数p及回路总电容C(∑) 分别为:

p=Cc/(Cc+Cj)

C(∑)=C1+CcCj/(Cc+Cj)

式中,C(j0)——变容二极管的结电容,它与外加电压的关系为:

Cj=C(j0)/(1-u/U)

式中,C(j0) ——变容管零偏压时的结电容;

U(D) ——变容管PN结内建电位差(硅管 =0.7V,锗管 =0.3V);

二. 单元参数设计

本设计基于LC振荡器原理,通过变化变容二极管两端的电压来改变电容, 以达到改变频率,从而实现设计的要求。完成了调频的要求本设计包括三点式振 荡器模块、放大器模两块部分。其系统框图如图所示。

1、LC三点式振荡组成原理图

其振荡频率f=1

2?LC。当X1 和X2为

容性,X3为感性时称为电容反馈振荡器,其中

4

C=C1C2;当X1 和X2为感性,X3为容性时称 C1?C2

为电容反馈振荡器,其中 L=L1+L2。当我们相应

的变化电容值时就能使频率作出相应的变化,以达到左图三点式振荡组成到调频的目的。

此设计的关键是在没有加载音频信号时利用LC振荡器振荡出主频6.5MHz。后面用放大器对调制的信号进行放大。

(1)、LC振荡模块设计

西勒振荡器

西勒振荡器其振荡频率为f=12?LC,式中C=1+C4,这种振荡器111??C1C2C3

较易起振,振荡频率也较为稳定,波形失真较小,当参数设置得当时,其频率覆盖系数

较大。

(2)、变容二极管调频原理

所谓调频,就是把要传送的信息(例如语言、音乐)作为调制信号去控制载波(高频振荡信号)的瞬时频率,使其按调制信号的规律变化。

??设调制信号: ???t??V?cos?t,载波振荡电压为:at?Aocos?ot

根据定义,调频时载波的瞬时频率??t?随???t?成线性变化,即

(2-1)

则调频波的数字表达式如下: KfV????af?t??Aocos??ot?sin?t????? ??t???o?KfV?cos?t??o???cos?t

或

式中: af?t??Aocos??ot?mfsin?t? (2-2) ???KfV?是调频波瞬时频率的最大偏移,简称频偏,它与调制信号的振幅成正比。比例常数Kf亦称调制灵敏度,代表单位调制电压所产生的频偏。 式中:mf?KfV????????fF称为调频指数,是调频瞬时相位的最大偏移,它的大小反映了调制深度。由上公式可见,调频波是一等幅的疏密波,可 5

以用示波器观察其波形。

如何产生调频信号?最简便、最常用的方法是利用变容二极管的特性直接产生调频波,其原理电路如图2—1所示。

图2-1 变容二极管调频原理电路

变容二极管Cj通过耦合电容C1并接在LCN回路的两端,形成振荡回路总电容的一部分。因而,振荡回路的总电容C为:

C?CN?Cj

振荡频率为: (2-3)

f?1

2?LC?1

2?L(CN?Cj) (2-4)

加在变容二极管上的反向偏压为:

VR?VQ?直流反偏?????调制电压???O?高频振荡,可忽略?

变容二极管利用PN结的结电容制成,在反偏电压作用下呈现一定的结电容(势垒电容),而且这个结电容能灵敏地随着反偏电压在一定范围内变化,

由此可得出振荡回路总电容的变化量为:

(2-6)

由式可见:它随调制信号的变化规律而变化,式中?C?C???CN?CjQ???Cj??Cmcos?t Cm是变容二极管结电容变化的最大幅值。我们知道:当回路电容有微量变化?C时,振荡频率也会产生?f的变化,其关系如下:

6

?f1?C??f02C (2-7)

式中,是f0未调制时的载波频率;C0是调制信号为零时的回路总电容,显然

Co?CN?CjQ

由公式(2-4)可计算出f0(调频中又称为中心频率)。

f0?

即: 12?L(CN?CjQ)

将(2-6)式代入(2-7)式,可得: ?f(t)?1(f0/C0)Cmcos?t??fcos?t2 (2-8)

频偏: ?f?1(f0/C0)Cm2 (2-9)

????振荡频率: ft?fo??ft?fo??fcos?t (2-10)

由此可见:振荡频率随调制电压线性变化,从而实现了调频。其频偏?f与回路的中心频率f0成正比,与结电容变化的最大值Cm成正比,与回路的总电容C0成反比。

为了减小高频电压对变容二极管的作用,减小中心频率的漂移,常将图2—1中的耦合电容C1的容量选得较小(与Cj同数量级),这时变容二极管部分接入振荡回路,即振荡回路的等效电路如图1—3所示。理论分析将证明这时回路的总电容为

'C0?CN?C1?Cj/(C1?Cj) (2-11)

回路总电容的变化量为:

'C0?CN?C1?Cj/(C1?Cj) (2-12)

回路总电容的变化量为:

?C'?P2?Cj

(2-13) 7

频偏: 1?f'?P2?(f0/C0)Cm?P2?f2 (2-14)

式中,P?C1?C1?CjQ?称为接入系数。

Cj~?R曲线决定。从关于直流反偏工作点电压的选取,可由变容二极管的

曲线中可见,对不同的?R值,其曲线的斜率(跨导)SC??Cj??各不相同。?R较小时,SC较大,产生的频偏也大,但非线性失真严重,同时调制电压不宜过

VC?R较大时,SC较小,大。反之,达不到所需频偏的要求,所以Q一般先选在j~

?R曲线线性较好,且SC较大区段的中间位置,大致为手册上给的反偏数值,例:2CC1C,VQ?4V。本实验将具体测出实验板上的变容二极管的Cj~?R曲线,并由同学们自己选定VQ值,测量其频偏?f的大小。

三.调试步骤

1、按设计电路安装元器件

由于调频振荡器的工作频率较高,晶体管的结电容、引线电感、分布电容及测量仪器对电路的性能影响均不能忽略。因此,在电路装调及测试时应尽量减小这些分布参数的影响。安装时应合理布局,减小分布参数的影响。电路元件不要排得太松,引线尽量不要平行,否则会在元件或引线之间产生一点的分布参数,引起寄生反馈。多级放大器应排成一条直线,尽量减小未级和前级之间的耦合。地线应尽可能粗,以减小分布电感引起的高频损耗,制印刷电路板时,地线的面积应尽量大。为减小电源内阻形成的寄生反馈,应采用滤波电容(C)及滤波电感(L)组成的(∏)型或(T)型滤波电路,一般(L)为几十微亨至几百微亨,(C)为几百皮法至几十千皮法。

2、测试点选择

正确选择测试点,减小仪器对被测电路的影响。在高频情况下,测量仪器的输入阻抗(包含电阻和电容)及连接电缆的分布参数都有可能影响被测电路的谐振频率及谐振回路的Q值,为尽量减小这种影响,应正确选择测试点,使仪器的输入阻抗远大于电路测试点的输出阻抗。对于图2所示电路,高频电压表接于C点,示波器接于E点,数字频率计接于A点,(C4)的值要小,以减小数字频率计的输入阻抗对谐振回路的影响。所有测量仪器如高频电压表,示波器,扫描仪,数字频率计等的地线及输入电缆的地线都要与被测电路的地线连接好,接线尽量短。

3、调试

8

一般高频电路的实验板应为印刷电路板,以保证元器件可靠焊接及连接导线固定,使电路的分布参数基本固定。高频电路的调试方法与低频电路的调试方法基本相同,也是先调整静态工作点,然后观测动态波形并测量电路的性 能参数。所不同的是按照理论公式计算的电路参数与实际参数可能相差较大,电路的调试要复杂一些。

4频率稳定度

?f/f0?5?10?3/小时

心得体会:

在这次课程设计中,动手能力得到进一步的提高。和模拟电子技术课程设计比,具有更大的难度和更强的挑战性。

此次课程设计不但锻炼了我们最基本的高频电子线路的设计能力,更重要的是让我们更深刻的认识了高频电子线路这门课程在实际中的应用。还是有书到用时方恨少的感觉呀。

在此次设计时我们也遇到了不少的困难和问题,但在同伴们的共同努力下,辛苦的去专研去学习,最终都克服了这些困难,使问题得到了解决。其中遇到的问题很多都是在书上不能找到的,所以我们必须自己查找相关资料,利用图书馆和网络,这是一个比较辛苦和漫长的过程,你必须从无数的信息中分离出对你有用的,然后加以整理,最后才学习到变为自己的并用到设计中的问题去。

要设计一个电路总得先仿真成功之后才能实际接线,但最后的成品却不完全与仿真时一样,因为在实际接线中有着各种各样的条件限制,如在实际中因芯片本身的特性而未达到成功。所以,在设计时应考虑这些差异,从中找出最合适的设计方法。

附图:

9

10