数据选择器、译码器、全加器实验

一、实验目的

1、熟悉数据选择器的功能。

2、熟悉译码器的工作原理和使用方法。

3、设计应用译码器,进一步加深对它的理解。

4、学习用中规模集成电路的设计方法。

二、实验所用仪器和芯片

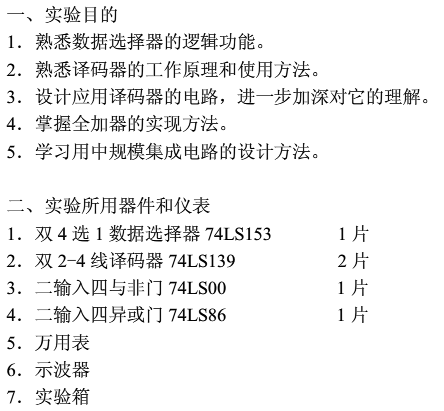

1、双4选1数据选择器 74LS153 1片

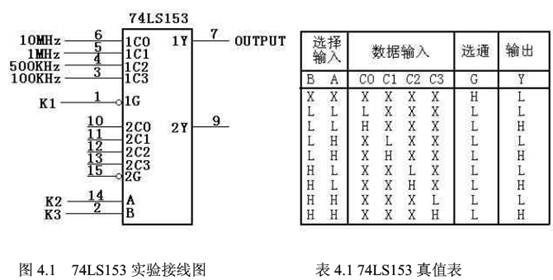

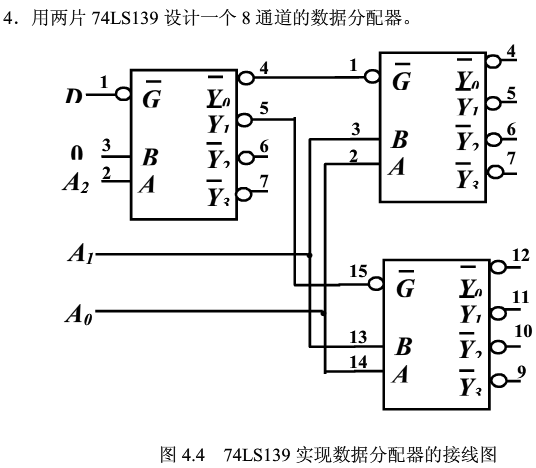

2、双2线-4线译码器 74LS139 2片

3、四两输入与非门 74LS00 1片

3、TEC-5(TDS-2)实验系统 1台

三、实验内容

1、用Quartus II设计一个4选1的数据选择器

4个输入端输入4组周期不同的信号,改变数据选择引脚的电平和使能端(低电平有效)的电平,产生四种不同的组合,观察每种组合下数据选择器的的输出信号情况;

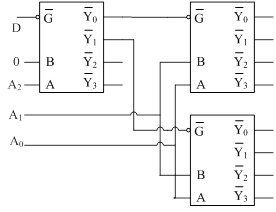

2、用2线-4线译码器设计一个3线-8线译码器,框图如下:

3、用数据选择器(1片74LS153)设计实现一位全加器,实现电路并验证其正确性。

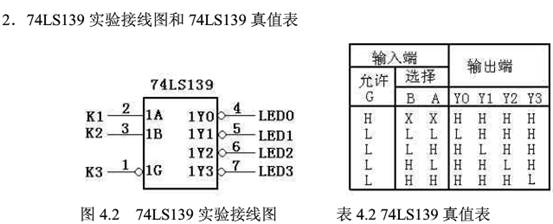

附74LS153和74LS139管脚图

输入 输入 输出

Vcc G2 A1 2D3 2D2 2D1 2D0 2Y 输出

Vcc G2 A1 2D3 2D2 2D1 2D0 2Y 输出  Vcc G2 A1 B2 2Y0 2Y1 2Y2 2Y3

Vcc G2 A1 B2 2Y0 2Y1 2Y2 2Y3

G1 A0 1D3 1D2 1D1 1D0 1Y GND

G1 A0 1D3 1D2 1D1 1D0 1Y GND  G1 A1 B1 1Y0 1Y1 1Y2 1Y3 GND

G1 A1 B1 1Y0 1Y1 1Y2 1Y3 GND

输入 输出 输入 输出

第二篇:实验二 数据选择器 译码器 全加器实验

实验二 数据选择器 译码器 全加器实验