实验三 译码器和数据选择器

一、 实验目的

1. 熟悉中规模集成译码器电路的原理及功能;

2. 掌握中规模集成译码器的使用方法及功能测试方法;

3. 了解集成译码器的应用。

二、实验仪器设备和材料

1. TPE-AD型数字电路实验箱 1台

2. 3线-8线译码器74LS138 1块

3. 双四输入与非门74LS20 1块

4. 四两输入与非门74LS00 1块

5. 双四选一数据选择器74LS153 1块

三、实验内容

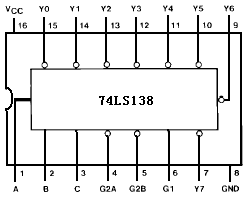

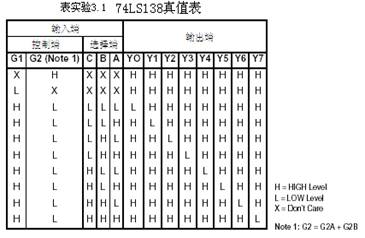

1. 74LS138逻辑功能测试

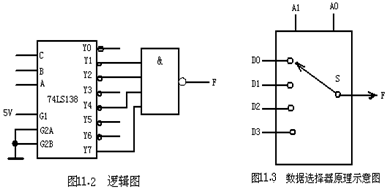

2. 用74LS138和74LS20构成一位全减器

3. 用74LS138实现一个数据分配器

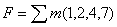

4. 用74LS138和74LS153构成一个四通道数据传输系统

四、实验数据及相关图表

①74LS138脚管分布图

74LS138管脚分布图

74LS138真值表

②74LS138实现一个数据分配器

②74LS138实现一个数据分配器

③数据选择器(图如上)

多通道数据传输:

五、实验总结

本次的实验不像上次那么简单,对于逻辑电路的应用需要更熟练。74LS138的功能是将每个输入的二进制代码译成对应的输出高,低电平的信号,它是编码的反操作。在实验过程中因为要控制更多的输入和观察记录等更多的输出,每一步都要准确无误才会得到正确的结果。

对双四数据选择器74LS153的使用相对困难。首先是原理的理解,其次是线路的分配。把74LS138和74LS153综合运用起来才能实现多通道数据传输。应该先对电路的数字逻辑进行详细的分析,可以提高学习的效率也能加强对实验的理解。

第二篇:触发器 数据选择器和译码器实验报告3

CPLD/FPGA设计实验报告

实验名称: 时序电路设计基础

实验目的: 掌握Quartus II 软件的基本使用方法,完成基本时序电路设计

实验内容:

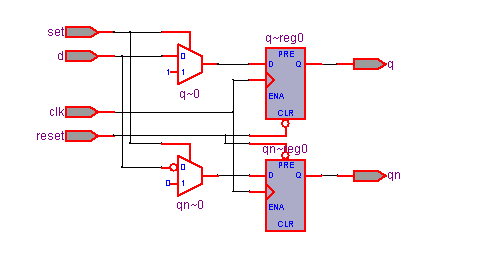

实验一 D触发器

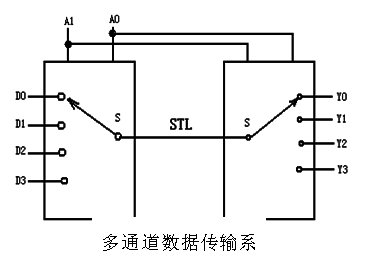

一、 创建工程

工程名称:dff_asyn 顶层实体文件名:dff_asyn

器件: EP1C3T100C6 (要求:Cyclone系列任意器件)

二、 创建文件

创建Verilog HDL文件,实现同步置数异步清零带Q_n输出的D触发器。

module dff_asyn(q,qn,d,clk,set,reset);

input d,clk,set,reset;

output reg q,qn;

always @ (posedge clk or negedge reset)

begin

if (~reset)

begin

q<=1'b0;

qn<=1'b1;

end

else if (set)

begin

q<=1'b1;

qn<=1'b0;

end

else

begin

q<=d;

qn<=~d;

end

end

endmodule

三、 编译工程

报告中下列数据是多少

四、 仿真电路

1、创建VWF文件

2、设定“End Time”为20us

3、在VWF文件中添加Node OR Bus

4、编辑波形

5、仿真

6、画出仿真结果

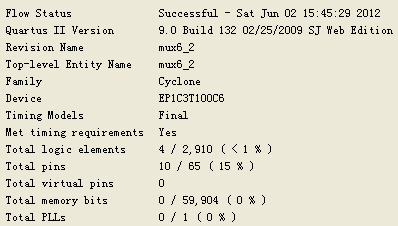

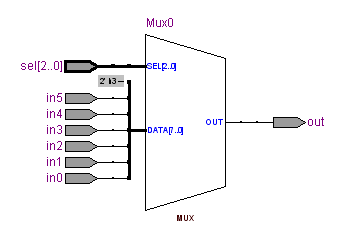

实验二 数据选择器

一、 创建工程

工程名称: mux6_1 顶层实体文件名: mux6_1

器件: EP1C3T100C6 (要求:Cyclone系列任意器件)

二、 创建文件

创建Verilog HDL文件,实现6选1数据选择器。

module mux6_1(out,in0,in1,in2,in3,in4,in5,sel);

input in0,in1,in2,in3,in4,in5;

input [2:0] sel;

output reg out;

always @ (in0,in1,in2,in3,in4,in5,sel)

case (sel)

3'b000: out=in0;

3'b001: out=in1;

3'b010: out=in2;

3'b011: out=in3;

3'b100: out=in4;

3'b101: out=in5;

default: out=3'b111;

endcase

endmodule

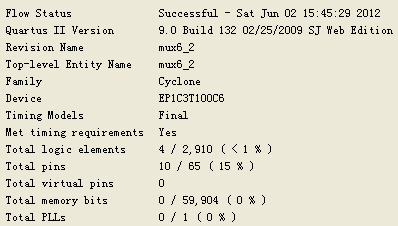

三、编译工程

报告中下列数据是多少

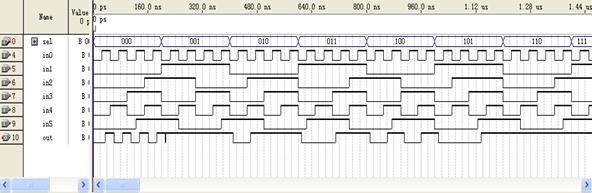

四、 仿真电路

1、创建VWF文件

2、设定“End Time”为20us

3、在VWF文件中添加Node OR Bus

4、编辑波形

5、仿真

6、画出仿真结果

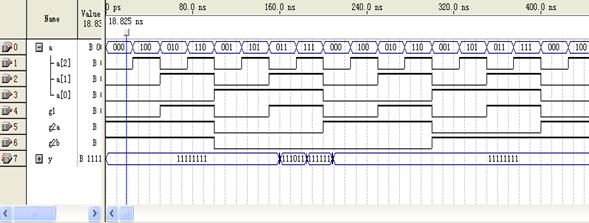

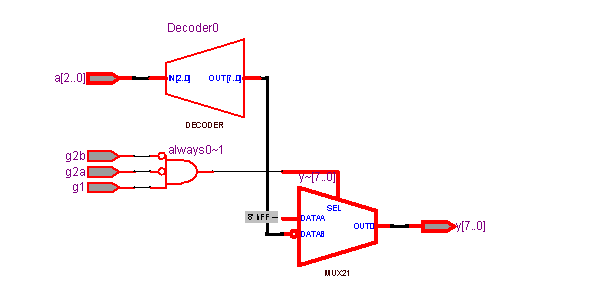

实验三 3-8译码器(使用Always语句实现)

一、创建工程

工程名称: tt74138 顶层实体文件名: tt74138

器件: EP1C3T100C6 (要求:Cyclone系列任意器件)

二、 创建文件

创建Verilog HDL文件,实现3-8译码器(使用Always语句实现)。

module tt74138(a,y,g1,g2a,g2b);

input [2:0] a;

input g1,g2a,g2b;

output reg [7:0] y;

always@ (a,y,g1,g2a,g2b)

begin

if (g1&~g2a & ~g2b)

begin case(a)

3'b000:y=8'b1111_1110;

3'b001:y=8'b1111_1101;

3'b010:y=8'b1111_1011;

3'b011:y=8'b1111_0111;

3'b100:y=8'b1110_1111;

3'b101:y=8'b1101_1111;

3'b110:y=8'b1011_1111;

3'b111:y=8'b0111_1111;

endcase

end

else y=8'b1111_1111;

end

endmodule

三、编译工程

报告中下列数据是多少

四、 仿真电路

1. 创建VWF文件

2. 设定“End Time”为20us

3. 在VWF文件中添加Node OR Bus

4. 编辑波形

5. 仿真

6. 画出仿真结果