<时序逻辑电路设计实验>实验报告

学生姓名:文超周李旭

班级学号: 1138019 1138033

指导老师: 潘秀琴

<实验报告内容>

一、实验名称:时序逻辑电路设计实验

二、实验学时: 5学时

三、实验目的:

1、掌握Verilog HDL 时序电路的设计方法,重点练习条件语句、always模块、和寄存器型变量使用方法。

2、了解常用时序逻辑电路(计数器)中清零和使能控制的概念,以及同步清零、异步清零、同步置数、异步置数的区别。

四、实验内容

1、用Verilog HDL设计同步二进制加法计数器,并对其进行功能仿真。

2、用Verilog HDL设计加减可控的二进制计数器,并对其进行功能仿真。

五、实验原理

计数器是最常用的时序逻辑电路,从计算机的微处理器地址发生器到频率计都需要用到计数器。常见计数器有加法计数器和减法计数器。加法计数器时根据二进制加法原理,每来一个脉冲计数值加1;减法计数器根据二进制减法原理每来一个脉冲计数器值减1。同一计数器兼具有加法和减法功能,成为加减可控计数器或可逆计数器。

六、实验步骤

1、认真阅读实验目的、内容及要求,清楚实验的具体步骤。

2、根据实验要求查阅相关学习资料,整理完成本实验任务的基本思路并完成实验的代码编写。

3、逻辑功能代码编写:根据确定的实现方案,在软硬件实验环境下,用VerilogHDl语言进行可编程逻辑电路功能设计,完成程序代码编写。

4、逻辑功能检查:认真分析所编写代码是否能够实现实验任务所要求的功能,如果有不符合的地方,对代码逻辑电路功能描述进行修改,确认正确进入下一步。

5、编译并进行代码修改和完善:对编写完成的代码进行编译,并对编译过程中出现的错误进行语法修改,直至编译完全通过。

6、功能仿真:建立波形文件,对所涉及时序电路进行功能仿真,认真分析时序所描述的功能与所要求的功能是否符合,如果不符合重复本部分规定的内容或者程序中变量端口模块的定义应用是否正确等内容,直至功能仿真完全正确。

七、实验结果

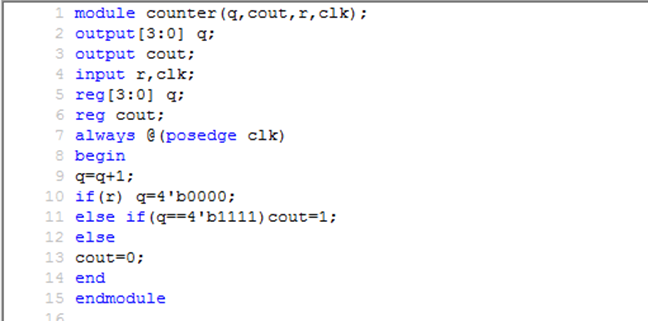

1、同步二进制加法计数器

文本输入;

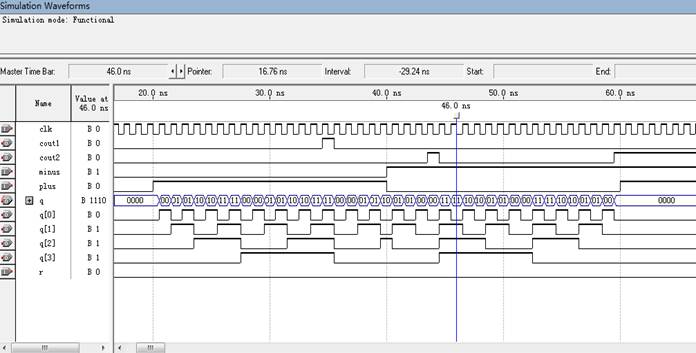

波形图:

2、加减可控的二进制计数器

八、心得体会

本次试验主要掌握和理解了时序电路的设计思路和设计方法,还复习了条件语句、always模块、和寄存器型变量使用方法,对常用时序逻辑中清零和使能控制有了初步的认识,知道了同步清零、异步清零、同步置数、异步置数的区别。

九、附录:<程序代码>

1、同步二进制加法计数器

module counter(q,cout,r,clk);

output[3:0] q;

output cout;//进位输出

input r,clk;

reg[3:0] q;

reg cout;

always @(posedge clk)

begin

q=q+1;

if(r) q=4'b0000;

else if(q==4'b1111)cout=1;

else

cout=0;

end

endmodule

2、加减可控的二进制计数器

module plus_minus_counter(clk,r,q,cout1,cout2,plus,minus);//加减可控的二进制计数器

input clk,r,plus,minus;//plus做加法,minus做减法

output [3:0]q;

output cout1,cout2;//cout1为进位输出,cout2为借位输出

reg [3:0]q;

reg cout1,cout2;

always @(posedge clk)

begin

if (r) q=4'b00;

else if(plus && minus)

q=4'b00;

else if(plus)

begin

q=q+1;

if(q==4'b1111)

cout1=1;

else cout1=0;

end

else if(minus)

begin

q=q-1;

if (q==4'b0000)

cout2=1;

else

cout2=0;

end

end

endmodule

第二篇:实验四 时序逻辑电路设计(1)