目录

1课程设计要求·····································································3

2 电路功能描述····································································3

3 设计方案·············································································3

4设计原理图··········································································4

5 VHDL语言············································································4

6仿真截图···············································································6

7心得体会···············································································11

8参考文献···············································································11

1. 课程设计要求

1.1.红、黄、绿灯分别控制显示;

1.2.每一个状态分别分配一个时间显示(两位十进制,倒计时);

1.3.符合实际交通规律。

2.电路功能描述

本设计是实现交通灯的控制,模拟实现了红、绿、黄灯指挥交通的功能。本设计适用东西和南北方向的车流量大致相同的路口,红灯显示时间30S,绿灯显示时间25S,黄灯显示时间5S,同时用数码管指示当前的状态(红、绿、黄灯)的剩余时间。当有紧急状况发生时,两个方向都禁止通行,并且显示红灯,当紧急状况解除后,重新计时并且指示时间。

3.设计方案

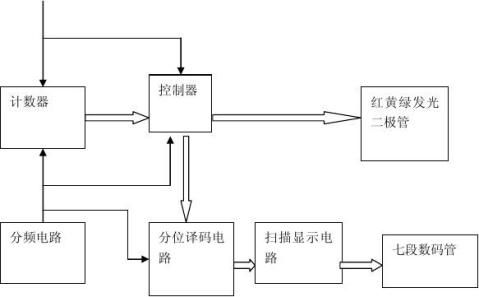

根据设计要求,需要控制显示红、黄、绿三个灯的亮灭状态及显示的时间。这个设计主要由两部分组成,红黄绿灯的显示模块,显示时间模块。由实际的交通情况可知,东西方向的显示情况是一致的,南北方向的显示情况也是一致 ,故在设计的时候就只考虑两种状态,将东西方向合成一种,南北方向合成一种。红黄绿灯的显示模块用两组共6个灯显示,时间显示模块用LED数码管显示。

此外,本交通灯控制器设置的红黄绿显示方式是参照一些城市的显示规律,红灯30S,绿灯25S,黄灯5S,同时用数码管指示当前状(红、绿、黄灯)的剩余时间。另外还设有一个紧急状态,当特殊情况发生时,两个方向都禁止通行,指示红灯,紧急状态解除后,重新计时并指示时间。时间采用倒计时的方式显示。

本设计采用VHDL语言编程,描述各个硬件模块实现的功能,使红、黄、绿灯的转换有一个准确的转换顺序和时间间隔,并进行仿真,通过仿真的结果,得出实验的结果。

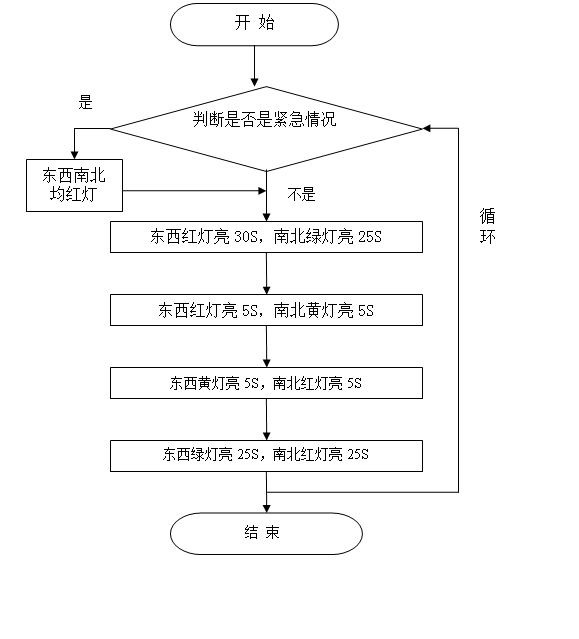

在正常情况下的一个完整周期内,交通灯控制器系统一共有四种状态,分别是东西红、南北绿,东西红、南北黄,东西绿、南北红,东西黄、南北红。其运行方式为东西红、南北绿→东西红、南北黄→东西绿、南北红→东西黄、南北绿,东西黄、南北绿结束后再回到东西红、南北绿的状态,整个周期持续60s。urgency为紧急控制信号,为高电平时系统转换为东西南北均是红灯亮的状态,状态结束后系统重新设置,转换为东西红,南北绿的状态。

4.设计的原理图

5.VHDL硬件描述语言

5.VHDL硬件描述语言

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY traffic IS --定义实体

PORT( clk : IN STD_LOGIC; --CLK为时钟信号(1Hz)

urgency : IN STD_LOGIC; --紧急状态控制端

led : BUFFER STD_LOGIC_VECTOR(5 DOWNTO 0); --红黄绿绿黄红

East_West,South_North : BUFFER STD_LOGIC_VECTOR(7 DOWNTO 0));

END; --东西、南北倒计时数码管(高4位为十位,低4位为个位)

ARCHITECTURE rtl OF traffic IS --定义结构体

BEGIN

PROCESS(clk,urgency)

BEGIN

IF urgency = '1' THEN --出现紧急状态

led <= "100001"; --东西南北都亮红灯

East_West <= "00000000"; --设置重新计时的数据

South_North <= "00000000";

ELSIF (clk'EVENT AND clk = '1') THEN

IF (East_West > "00110000" or South_North > "00110000") THEN

East_West <= "00101001"; --计数错误时纠正到初始转态

South_North <= "00100100";

led <= "100100"; --东西红灯亮30秒,南北绿灯亮25秒

ELSIF (East_West = "00000101" AND South_North = "00000000") THEN

East_West <= "00000100"; --红、绿灯亮了25秒,绿灯将转变为黄灯

South_North <= "00000100";

led <= "100010"; --东西红灯亮剩余5秒,南北黄灯亮5秒

ELSIF (East_West = "00000000" AND South_North = "00000000" AND led = "100010") THEN --东西红灯30秒时间结束,南北黄灯5秒结束

East_West <= "00100100";

South_North <= "00101001";

led <= "001001"; --东西亮绿灯25秒,南北亮红灯30秒

ELSIF (East_West = "00000000" AND South_North = "00000101") THEN

East_West <= "00000100"; --东西红绿亮25秒结束,转为5秒黄灯

South_North <= "00000100";

led <= "010001"; --东西黄灯亮5秒,南北红灯亮剩余5秒

ELSIF (East_West = "00000000" AND South_North = "00000000" AND led = "010001") THEN --东西亮黄灯5秒结束,南北亮30秒红灯结束

East_West <= "00101001";

South_North <= "00100100";

led <= "100100"; --东西红灯30秒,南北绿灯25秒,循环

ELSIF (East_West(3 DOWNTO 0) = 0 AND South_North (3 DOWNTO 0) = 0) THEN

East_West <= East_West - 7; --BCD码减法转换

South_North <= South_North - 7;

ELSIF (East_West(3 DOWNTO 0) = 0 AND South_North (3 DOWNTO 0) = 0) THEN

East_West <= East_West - 7; --BCD码减法转换

South_North <= South_North - 1;

ELSIF (South_North (3 DOWNTO 0) = 0 AND East_West(3 DOWNTO 0) = 0) THEN

South_North <= South_North - 7; --BCD码减法转换

East_West <= East_West - 1;

ELSE East_West <= East_West - 1; --不满足上述特殊情况时减一

South_North <= South_North - 1;

END IF;

END IF;

END PROCESS;

END;

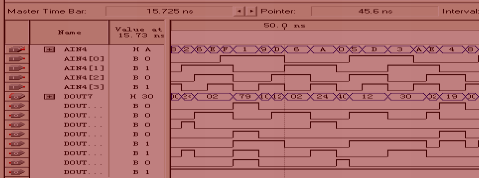

6.仿真截图

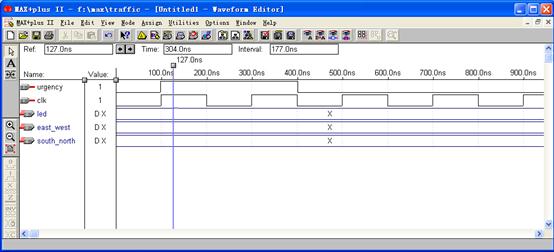

6.1VHDL源程序仿真

创建VHDL语言的编程窗口,并进行保存

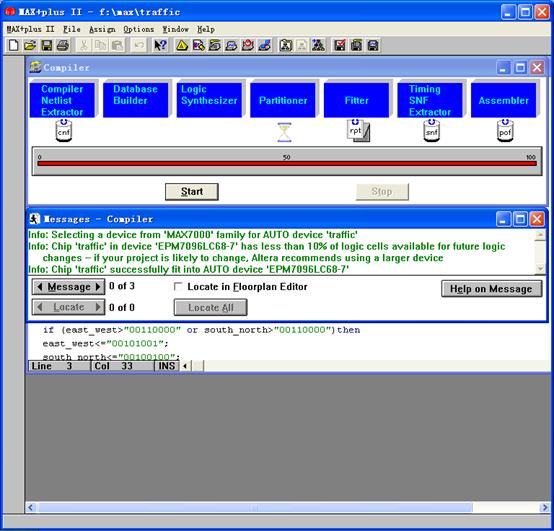

程序截图:

对源程序进行编译,为出现错误。

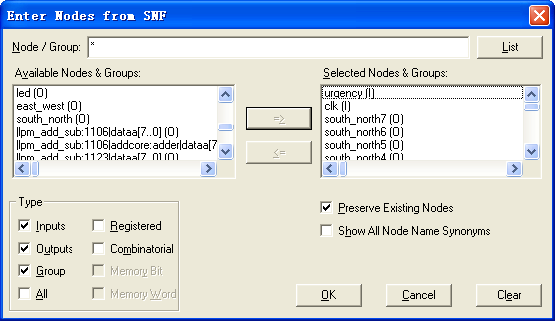

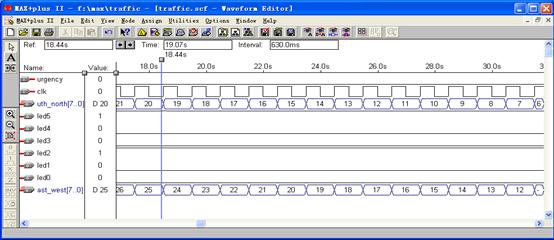

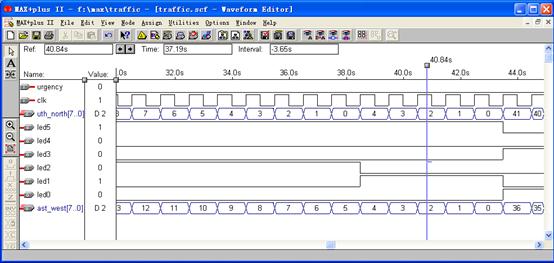

6.1.2创建波形文件并进行仿真

导入,

将仿真的结束时间定为65s,进行仿真;

(1)、东西红,南北绿:

(2)、东西红,南北黄

(3)东西绿,南北红

7.心得体会

通过这次的课程设计,加深了我对EDA技术这么课程的理解和认识,同时也让我对其有了更加熟练的运用。之前对VHDL的了解仅局限于课本上的些许知识,而没有深入体会,缺乏实践经验。这次的课程设计是很有意义的。

看到设计题目之后,我意识到自己对VHDL语言的掌握程度远远不够,开始查阅VHDL教程,寻找教程上的相似问题。最先做的是对设计进行模块的划分。在这个过程中,我也遇到了很多的问题,刚开始,没有找对方向,浪费了很多的时间。慢慢的,在查阅了相关的书籍之后,我找到了设计思路,确定了其由两个模块构成的思路。在对各个模块进行仿真的时候,遇到了不少困难,各个模块的连接以及信号的定义老是出现错误,经过反复修改才成功。

8.参考文献

[1] 潘松 黄继业?EDA技术实用教程——VHDL版(第4版)?科学出版社,2010

第二篇:EDA课程设计交通灯控制器

东 北 石 油 大 学

课 程 设 计

东北石油大学课程设计任务书

课程 EDA技术课程设计

题目 交通灯控制器

专业 姓名 学号 1

主要内容、基本要求、主要参考资料等

主要内容:

设计一个交通信号灯控制器,由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外。

基本要求:

1、红、绿、黄发光二极管作信号灯,用传感器或逻辑开关作检测车辆是否到来的信号,实验电路用逻辑开关代替。

2、主干道处于常允许通行的状态,支干道有车来时才允许通行。主干道亮绿灯时,支干道亮红灯;支干道亮绿灯时,主干道亮红灯。

3、主、支干道均有车时,两者交替允许通行,主干道每次放行45秒,支干道每次放行25秒,设立45秒、25秒计时、显示电路,选择1HZ时钟脉冲作为系统时钟。

4、在每次由绿灯亮到红灯亮的转换过程中,要亮5秒黄灯作为过渡,使行驶中的车辆有时间停到禁行线外,设立5秒计时、显示电路。

主要参考资料:

[1] 潘松著.EDA技术实用教程(第二版). 北京:科学出版社,2005.

[2] 康华光主编.电子技术基础 模拟部分. 北京:高教出版社,2006.

[3] 阎石主编.数字电子技术基础. 北京:高教出版社,2003.

完成期限

指导教师

专业负责人

20xx年 3月7日

1

一、总体设计思想

1.基本原理

设计一个交通信号灯控制器,由一条主干道(这里用南北道路为主干道)和一条支干道由东西道路为支干道)汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外。用实验平台上的LED发光二极管显示车辆通过的方向(东西和南北各一组),用数码管显示该方向的剩余时间。工作顺序为东西方向红灯亮45秒,前40秒南北方向绿灯亮,后5秒黄灯亮。然后南北方向红灯亮25秒,前20秒东西方向绿灯亮,后5秒黄灯亮。依次重复。设计一个交通信号灯控制器,由一条主干道和一条支干道汇合成十字路口,在每个入口处设置红、绿、黄三色信号灯,红灯亮禁止通行,绿灯亮允许通行,黄灯亮则给行驶中的车辆有时间停在禁行线外

2.设计框图

二、设计步骤和调试过程 2

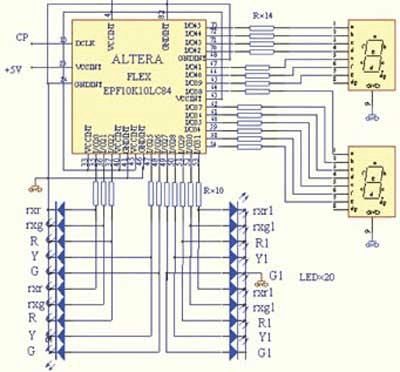

1、总体设计电路

2、模块设计和相应模块程序

(1)分频器

分频器实现的是将高频时钟信号转换成底频的时钟信号,用于触发控制器、计数器和扫描显示电路。该分频器实现的是一千分频,将一千赫兹的时钟信号分频成一赫兹的时钟信号。

LIBRARY IEEE;

USE IEEE.Std_Logic_1164.ALL;

ENTITY FreDevider IS

PORT

(Clkin:IN Std_Logic;

Clkout:OUT Std_Logic);

END;

ARCHITECTURE Devider OF FreDevider IS

CONSTANT N:Integer:=499;

signal counter:Integer range 0 to N;

signal Clk:Std_Logic;

3

BEGIN

PROCESS(Clkin)

begin

IF rising_edge(Clkin)THEN

IF Counter=N then

counter<=0;

Clk<=not clk;

else

counter<=counter+1;

end if;

end if;

end process;

clkout<=clk;

end;

(2)控制设计

控制器的作用是根据计数器的计数值控制发光二极管的亮、灭,以及输出倒计时数值给七段译管的分译码电路。此外,当检测到特殊情况(Hold=‘1’)发生时,无条件点亮红色的发光二极管。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY countroller IS

PORT (Clock:IN STD_LOGIC;

Hold:in std_logic;

CountNum:in INTEGER RANGE 0 TO 89;

NumA,NumB:out INTEGER RANGE 0 TO 45;

RedA,GreenA,YellowA:out std_logic;

RedB,GreenB,YellowB:out std_logic);

END;

ARCHITECTURE behavior OF Countroller IS

BEGIN

process(Clock)

BEGIN

IF falling_edge(Clock)THEN

IF Hold='1' THEN

RedA<='1';

RedB<='1';

GreenA<='0';

GreenB<='0';

YellowA<='0';

YellowB<='0';

4

ELSIF CountNum<=39 THEN

NumA<=40-CountNum;

RedA<='0';

GreenA<='1';

YellowA<='0';

ELSIF CountNum<=44 THEN

NumA<=45-CountNum;

RedA<='0';

GreenA<='0';

YellowA<='1';

ELSE

NumA<=90-CountNum;

RedA<='1';

GreenA<='0';

YellowA<='0';

END IF;

IF CountNum<=44 THEN

NumB<=45-CountNum;

RedB<='1';

GreenB<='0';

YellowB<='0';

ELSIF CountNum<=84 THEN

NumB<=85-CountNum;

RedB<='0';

GreenB<='1';

YellowB<='0';

ELSe

NumB<=90-CountNum;

RedB<='0';

GreenB<='0';

YellowB<='1';

END IF;

END IF;

END PROCESS;

END;

(3)计数器的设计

这里计数器的计数范围为0—45S 。计到45后,下一个时钟沿回复到0,开始下一轮计数.此外,当检测到特殊情况(Hold=‘1‘)发生时,计数器暂停计数,而系统复位号Reset则使计数器异步清0。

5

程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY counter IS

PORT (clock:IN STD_LOGIC;

reset:in std_logic;

Hold:in std_logic;

countNum:BuFFeR INTEGER RANGE 0 TO 90); END;

ARCHITECTURE behavior OF counter IS BEGIN

process(reset,Clock)

BEGIN

IF Reset='1' THEN

countNum<=0;

ELSIF rising_edge(Clock) THEN

IF Hold='1' then

countNum<=countNum;

ELSE

IF countNum=90 THEN

countNum<=0;

ELSE

countNum<=countNum+1;

END IF;

END IF;

END IF;

END PROCESS;

END;

(4)分位译码电路设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY Fenwei IS

PORT

(Numin:IN integer RANGE 0 TO 45; NumA,NumB:OUT Integer RANGE 0 to 9 );

END;

ARCHITECTURE behavior OF Fenwei IS BEGIN

6

process(Numin)

BEGIN

IF Numin>=40 THEN

NumA<=4;

NumB<=Numin-40;

ELSIF Numin>=30 THEN

NumA<=3;

NumB<=Numin-30;

ELSIF Numin>=20 THEN

NumA<=2;

NumB<=Numin-20;

ELSIF Numin>=10 THEN

NumA<=1;

NumB<=Numin-10;

ELSE

NumA<=0;

NumB<=Numin;

END IF;

END PROCESS;

END;

(5)分位译码电路设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL; ENTITY Fenwei2 IS

PORT

(Numin:IN integer RANGE 0 TO 45; NumC,NumD:OUT Integer RANGE 0 to 9 );

END;

ARCHITECTURE behavior OF Fenwei2 IS BEGIN

process(Numin)

BEGIN

IF Numin>=40 THEN

NumC<=4;

NumD<=Numin-40;

ELSIF Numin>=30 THEN

NumC<=3;

NumD<=Numin-30;

ELSIF Numin>=20 THEN

7

NumC<=2;

NumD<=Numin-20;

ELSIF Numin>=10 THEN

NumC<=1;

NumD<=Numin-10;

ELSE

NumC<=0;

NumD<=Numin;

END IF;

END PROCESS;

END;

(6)数码管驱动设计

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY bcd_data IS

PORT

(bcd_data:in STD_LOGIC_VECTOR(3 downto 0); segout: out STD_LOGIC_VECTOR(6 downto 0) );

END;

ARCHITECTURE behavior OF bcd_data IS BEGIN

process(bcd_data)

BEGIN

case bcd_data is

when "0000"=>segout<="1111110"; when "0001"=>segout<="0110000"; when "0010"=>segout<="1101101"; when "0011" =>segout<="1111001" ; when "0100" =>segout<="0110011" ; when "0101"=>segout<="1011011" ; when "0110"=>segout<="0011111" ; when "0111"=>segout<="1110000" ; when "1000" =>segout<="1111111" ; when "1001" =>segout<="1110011"; when others =>null;

END CASE;

END PROCESS;

END;

LIBRARY IEEE;

8

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_unsigned.ALL;

ENTITY dtsm IS

PORT(clk:in STD_LOGIC;

NumA,NumB,NumC,NumD: in STD_LOGIC_VECTOR(3 downto 0); segout1:out STD_LOGIC_VECTOR(6 downto 0);

led_sel: out STD_LOGIC_VECTOR(3 downto 0));

END dtsm;

architecture bhv of dtsm is

component bcd_data is

port (bcd_data:in STD_LOGIC_VECTOR(3 downto 0); segout:out STD_LOGIC_VECTOR(6 downto 0)); end component;

signal x:STD_LOGIC_VECTOR(3 downto 0);

signal q:STD_LOGIC_VECTOR(1 downto 0);

begin

p1:process(clk)

begin

if clk'event and clk ='1' then

Q<= Q + '1';

end if;

end process;

p2:process(Q)

begin

case Q is

when"00"=>led_sel<="1110";x<=NumD;

when"01"=>led_sel<="1101";x<=NumC;

when"10"=>led_sel<="1011";x<=NumB;

when"11"=>led_sel<="0111";x<=NumA;

when others=>null;

end case;

end process;

u1:bcd_data PORT map(bcd_data=>x,segout=>segout1); end ;

Clk: 输入,系统输入时钟;

reset:输入,是复位信号,高电平有效;

sensor:输入,为传感器信号,是高电平有效;

flash: 输出,转换期间的闪烁信号;

reda: 输出,主干道路口显示红灯信号,高电平有效; 9

greena: 输出,主干道路口显示绿灯信号,高电平有效; yellowa: 输出,主干道路口显示黄灯信号,高电平有效; redb: 输出,支干道路口显示红灯信号,高电平有效; greenb: 输出,支干道路口显示绿灯信号,高电平有效; yellowb: 输出,支干道路口显示黄灯信号,高电平有效; 实验总体程序:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity controller is

port

(clock:in std_logic;

reset:in std_logic;

sensor:in std_logic;

flashut std_logic;

numa,numbut integer range 0 to 90;

reda,greena,yellowaut std_logic;

redb,greenb,yellowbut std_logic

);

end;

architecture control of controller is

signal countnum:integer range 0 to 90;

begin

process(clock)

begin

if reset='1' then ---复位信号,将记数器清零 countnum<=0;

elsif rising_edge(clock) then

if sensor='1' then

flash<='1';

else

flash<='0';

if countnum=79 then ----记数到80秒时,记数器清零

countnum<=0;

else

countnum<=countnum+1; ---正常记数,计脉冲上升沿 end if;

end if;

end if;

10

end process;

process(clock)

begin

if rising_edge(clock) then

if sensor='1' then ---sensor信号有效期间,两组路灯都为红灯

reda<='1';

redb<='1';

greena<='0';

greenb<='0';

yellowa<='0';

yellowb<='0';

else ---sensor无效期间,系统行为:按照一个记数周期时间(80秒)描述动作

if countnum<=44 then ---前45秒,主干道的绿灯亮

numa<=50-countnum;

reda<='0';

greena<='1';

yellowa<='0';

elsif (countnum<=49) then --46-50秒,主干道的黄灯亮

numa<=55-countnum;

reda<='0';

greena<='0';

yellowa<='1';

else

numa<=80-countnum; ---51-80秒,主干道的红灯亮

reda<='1';

greena<='0';

yellowa<='0';

end if;

if countnum<=49 then ---0-50秒(主干道为绿,黄灯期间)支干道的红灯亮

numb<=55-countnum;

redb<='1';

greenb<='0';

yellowb<='0';

elsif countnum<=74 then ---56-75秒,支干道为绿灯

numb<=85-countnum;

redb<='0';

greenb<='1';

11

yellowb<='0';

else

numb<=80-countnum; ---76-80秒,支干道为黄灯 redb<='0';

greenb<='0';

yellowb<='1';

end if;

end if;

end if;

end process;

end ;

3、仿真及仿真结果分析

译码器模块由VHDL程序实现后,其功能仿真图如图所示:

仿真图

4、实验调试结果 打开

Quartus II

软件,新建一个工程,并新建一个

VHDL File

。把编写的

VHDL

程序出入进去,对自己编写的

VHDL

程序进行编译并仿真。仿真结果基本满足本实验的要求 三、结论及心得体会

12

通过这次试验,我能够熟练的掌握vhdl程序基本结构,学习编写简单的vhdl程序;可以熟练QuartusII设计流程,掌握QuartusII使用方法;并且能够在QuartusII的环境下,对其功能进行仿真,并在实验箱上验证设计的正确性。EDA设计我感觉程序调试最重要,试验软件、硬件熟悉其次。在编程没有错误之后可以进行波型仿真。若与理想的不同,再查看程序,有无原理上的编辑错误或没有查出的输入错误。都通过可以进行管脚配对,把程序烧入芯片,在实物机上看结果,从显示中得出还需改正的地方,再去改程序。必须注意没改一次都要编译,重新输入。

参考资料

[1] 李国丽等编著,EDA与数字系统设计,北京:机械工业出版社,2004

[2]彭介华.电子技术课程设计指导[M].高等教育出版社,1996..

[3] 谭会生.EDA技术综合应用实例与分析[M].西安:西安电子科技大学出版社,2004:99-110

[4] 辉.基于FPGA的嵌入式开发与应用[M].北京:电子工业出版社,2006:55-56

[5]李洋编著,EDA技术实用教程,北京:机械工业出版社,2004

13

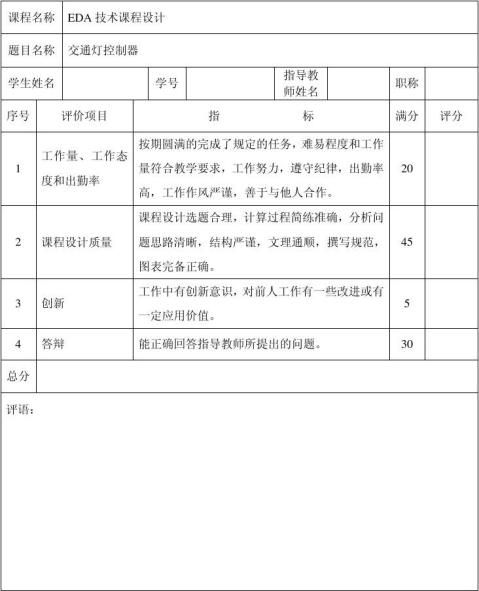

东北石油大学课程设计成绩评价表

指导教师: 20xx年 3 月 11 日