实验课题 函数波形发生器和频率计设计

一、 设计目的

1. 掌握低频数字频率计的设计原理与设计方法

2. 学会安装与调试数字电路的方法与步骤

3. 熟练掌握计数、锁存、译码、显示电路的应用

二、 设计任务与要求

1.测量信号范围:方波、正弦波;幅度0.5-5V;频率:1-9999Hz;

2.误差在1%;

3.应用最大读数;9999 Hz,用四个数码管显示,误差控制中、小规模集成电路设计数字频率计;

4. 拓展设计出能够产生连续可调的正弦波或三角波 或矩形波或锯齿波产生电路。

三、 实现方案和电路设计

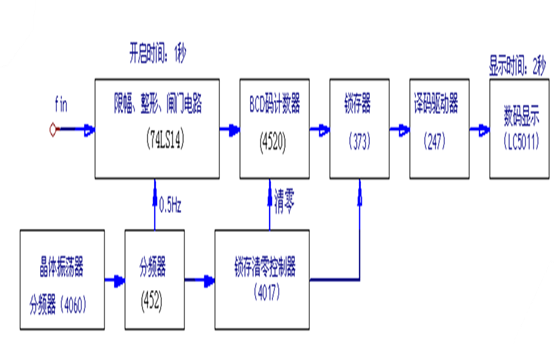

1. 工作原理:

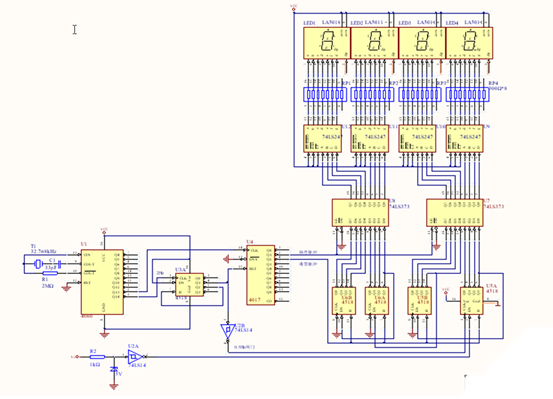

首先有准确的频率源,用它产生的频率信号经过分频电路后得到标准时间等于一秒的闸门信号,并在闸门信号的后沿由锁存清零控制器产生锁存信号使锁存器锁存数据、产生清零脉冲使计数器清零,以便下一次重新开始计数。

被测频率信号在闸门开启的一秒钟内可以通过闸门电路进入BCD码计数器进行计数,当闸门信号的后沿到来时计数器停止计数,同时在锁存信号的控制下将计数结果锁存在锁存器中,被锁存的数据经译码驱动电路译码后驱动数码显示电路。

2. 电路设计

① 时钟产生电路

晶体振荡器和分频器:

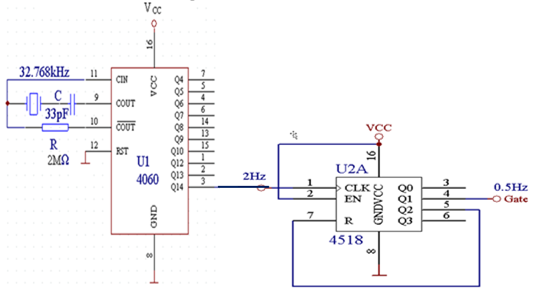

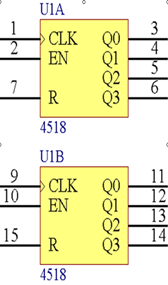

用内含非门电路的集成芯片4060外加石英晶体的方法构成晶体振荡器,4060是16脚双列直插式CMOS集成电路,内含6级反向器、一级施密特反向器和14级串行2分频电路,其中Q4~Q10和Q12~Q14共10个引脚有输出端。最大分频比是1/16384。11脚是时钟输入端(Clock-in),12脚是复位端(Reset)。

选用32.768MHz晶体,经4060芯片的14级二分频之后,在第三脚只能得到2Hz频率信号,要想得到宽度为1秒的闸门信号,还需要两极二分频器,所以在4060的Q14输出端(第三脚)又串入一只双4位二进制计数器4518。4518的R端为高电平时各个输出端均复位为0,R端为底电平时,有两种可以让计数器计数的方法:一是EN端保持高电平时CLK输入端每输入一个脉冲的上升沿,计数器均可加1。二是当CLK保持底电平时EN端每输入一个脉冲的下降沿,计数器可加1。所以从4518的Q1输出端的信号就是再经过四分频的正负半周均为1秒的方波信号。其中脉宽为1秒的正信号就是闸门信号(Gate)。

② 锁存清零控制器

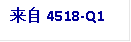

锁存信号是用来锁存1秒闸门时间内计数结果的,所以应在闸门脉冲结束后产生锁存信号。清零信号是用来对计数器清零的,必须在锁存信号之后到来。这一电路可用十进制循环计数器4017来完成。

4017是16脚双列直插式CMOS集成电路,有两个控制端,即复位端RST(15脚)和使能端(13脚);一个时钟输入端CLK(14脚);一个进位输出端CO(12脚)和十个循环输出端Q0~Q9。当RST为高时,除Q0输出“1”外,所有输出端均为“0”,当RST和均为低时,它对CLK端输入的时钟脉冲上升沿进行循环计数,Q0~Q9依次循环输出高电平。根据这一特点可以设计出锁存清零控制器电路。

来自4520的Q1端的闸门信号是正逻辑信号,闸门开启期间为高电平,这时4017的Q1端为“0”,计数器可以正常计数。闸门信号结束后计数停止,4017开始工作,来自4060的Q13端的脉冲重复频率比闸门信号低8倍,第二个脉冲上升沿使4017的Q1变高,将计数器中的数据锁存在锁存器中。第三个脉冲上升沿使4017的Q2变回低电平,Q1变成高电平,锁存器中的数据不变,但计数器被清零。第三个脉冲上升沿使Q0和Q1均变低,锁存器中的数据仍然不变,计数器保持“0”状态,但由于这时的闸门信号仍然是低电平,所以计数器并不计数。

到第八个脉冲结束时,4017只循环到Q7为高电平,还没有轮到Q0第二次变高,第二个闸门脉冲就开始了,计数器重新开始计数。

在计数器计数期间,由于锁存信号始终为低电平,锁存器中的数据仍然是前一次锁存的结果,一直保持到计数结束,锁存脉冲到来,锁存器中的数据才被更新。

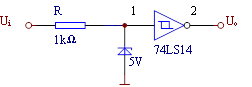

③ 限幅整形电路

频率计的输入信号是各种各样的,既可能有正弦波、矩形波和三角波,也可能有各种周期的、非周期的脉冲波和奇异波。无论什么波形,要计数准确,起码的条件是信号的信噪比必须足够大。输入级阻抗要足够高,而且当信号幅度很高时输入级电路不能被烧毁。因此在信号输入端应有一级高阻输入低噪声前置放大器和限幅器,并且应有一级整形电路,把各种输入信号变成比较规范的矩形波。

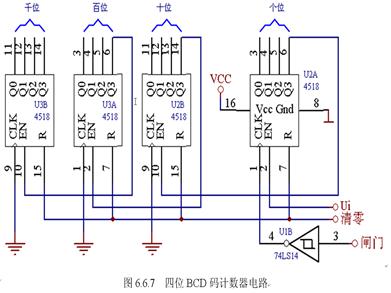

④ BCD码计数器

4518是BCD码十进制计数器,当BCD码“1001”向“0000”跳变, Q3由高变低的时候,故高位计数器要用低位计数器Q3的下降沿作为进位脉冲。为了满足这一要求,个位、十位和百位的进位信号都从本级的Q3接到高位的EN端,并将各计数器的CLK端接地,用清零脉冲控制复位端(R)。该电路个位计数器输入信号和控制信号的接法也应满足这样的逻辑,这是因为输入信号在整形电路中经过了反相,为保证计数的准确性,应该用输入信号的下降沿触发计数,故应从EN端接入输入信号,同时将闸门信号用74LS14反相后接入最低位十进制计数器的CLK端。

⑤ 锁存器、译码器和显示管

锁存器采用74LS373、译码器采用74LS247。

⑥ 元件清单

CD4060BD,CD4518BD,CD4017BT,74LS14D,74LS373,74LS47N,电阻2MΩ,石英晶振,电容0.1μF,七段显示管

⑦ 电路图

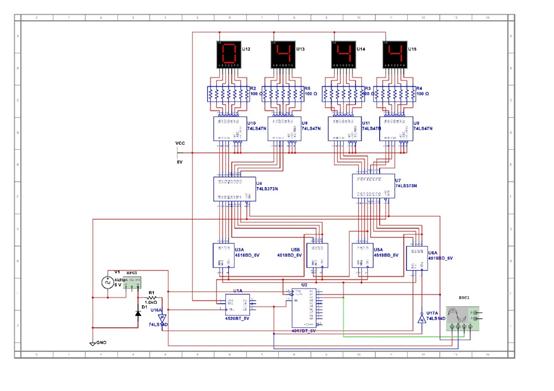

实体元件电路原理图:

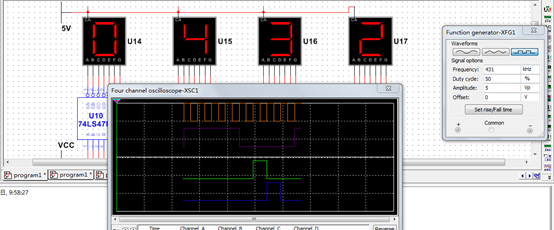

Multisim仿真电路图:

四、 仿真结果:

输入频率为443KHz,频率计显示444KHz,误差为1/443,小于1%,符合实验设计要求。

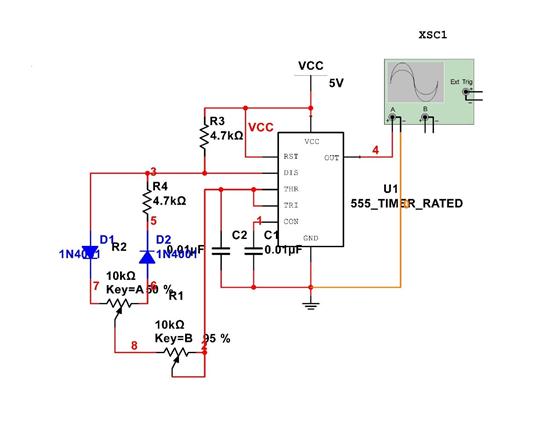

五、 制作波形发生器

外接元件R1,R2,R3,R4与C2构成多谐振荡器,引脚2与引脚6直接相连。电路没有稳态,仅存在两个暂稳态,利用电源通过电阻对电容C2充电,以及C2通过电阻放电,使电路产生震荡。通过改变R1和R2组合调节频率和占空比。

六、 课设体会

通过本次课程设计,我的数字电子技术基础的理论知识有了进一步巩固,对所学的各芯片的功能和使用方法有了更加清晰的认识。亲自动手实验也使我更加熟练地运用各种器材设备来解决一些实际问题。在此过程中,我也进一步熟悉了所用的Multisim仿真软件和实验箱的功能和使用方法。为以后进一步学习相关知识打下了很好的基础。

实验报告

实验项目 函数波形发生器和频率计设计

实验环境 PC机、Multisim、数字试验箱

学 院 信息与通信工程学院

班 级 通信1104

学号/姓名 2011010443 石福林

实验日期 2013/03/11—2013/03/20

指导教师 魏宁萍

第二篇:简易数字频率计实验报告

简易数字频率计设计报告

设计人员:王方伟,熊伟,田欣欣

目录

摘要

一.总体方案

二.电路分析与设计

1.可调频率波形发生器

2.整形电路

3.二分频电路

4.单片机计数部分

5.液晶显示部分

三.系统测试

1.调试仪器

2.测试结果分析

3.误差分析

四.总结

参考资料

附录

摘要

数字频率计用于测量正弦信号、矩形信号等波形的频率,其概念是单位时间里的脉冲个数。本设计采用89C52单片机为设计核心,将其分为波形产生部分,整形部分,单片机计数部分,显示部分。波形产生电路得到正弦波、三角波或矩形波;计数部分由89C52单片机实现;显示部分用液晶屏(LCD1602)。

关键词:AT89C52,分频计,频率计,LCD1602

Abstract

The digital frequency meter for measuring the frequency of the sinusoidal signal and rectangular signal waveform, the concept is the pulse number per unit time. This design uses a 89C52 microcontroller core for the design, waveform generator will be divided into the part, plastic part, the microcontroller to count part of the display section. Waveform generator circuit sine wave, triangle wave or square wave; count part of the 89C52 microcontroller; display part LCD screen

一.总体方案

1.总体设计思路:

波形发生电路采用ICL8038集成函数发生器,在经过74LS00整形电路整形,形成方波信号,再通过74LS74二分频电路,最后送到单片机T1计数并用LCD1602显示频率。

2. 总体原理框图:

可调频率波形产生电路 → 整形 → 计数 → 显示

二.电路分析与设计

1. 可调频率波形发生器

1、工作原理简介

ICL8038是单片集成函数发生器,其内部原理电路框图和外部引脚排列分别如图1和图2所示。在图1中, ICL8038由恒流源I1、I2,电压比较器C1、C2和触发器等组成。电压比较器C1、C2的门限电压分别为2VR/3和VR/(VR=VCC+VEE),电流源I1和I2的大小可通过外接电阻调节,且I2必须大于I1。当触发器的Q端输出为低电平时,它控制开关S使电流源I2断开。而电流源I1则向外接电容C充电,使电容两端电压VC随时间线性上升,当VC上升到VC=2VR/3时,比较器C1输出发生跳变,使触发器输出端Q由低电平变为高电平,控制开关S使电流源I2接通。由于I2>I1,因此电容C放电,vc随时间线性下降。当vc下降到vc≤VR/3时,比较器C2输出发生跳变,使触发器输出端Q又由高电平变为低电平,I2再次断开,I1再次向C充电,vc又随时间线性上升。如此周而复始,产生振荡,若I2=2I1,vc上升时间与下降时间相等,就产生三角波输出到脚3。而触发器输出的方波经缓冲器输出到脚9。三角波经正弦波变换器变成正弦波后由脚2输出。当I1<I2<2I1时,vc的上升时间与下降时间不相等,管脚3输出锯齿波。因此,8038能输出方波、三角波、正弦波和锯齿波等四种不同的波形。

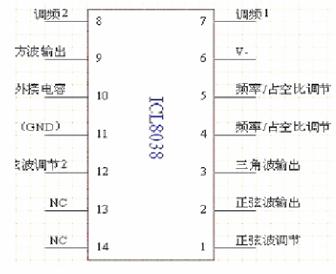

图1 ICL8038内部原理电路框图

图2 ICL8038管脚图

2、ICL8038的典型应用

由图2可见,管脚8为调频电压控制输入端,管脚7输出调频偏置电压,其值(指管脚6与7之间的电压)是(VCC+VEE)/5,它可作为管脚8的输入电压。此外,该器件的方波输出端为集电极开路形式,一般需在正电源与9脚之间外接一电阻,其值常选用10kΩ左右,如图3所示。当电位器RV1动端在中间位置,并且图中管脚7接+4V时,管脚9、3和2的输出分别为方波。三角波和正弦波。电路的振荡频率?约为0.3/[(R1+0.5RV1)C]。调节RV2﹑RV3可使正弦波的失真达到较理想的程度。RV1为调频电位器。RV4调节方波占空比及正弦波失真度。

图3 函数发生器电路图

可通过改变10号管脚的电容值来改变频率,C2从50uf--250pf每降低10倍频率增加10倍,再通过RV1来实现对频率的微调。

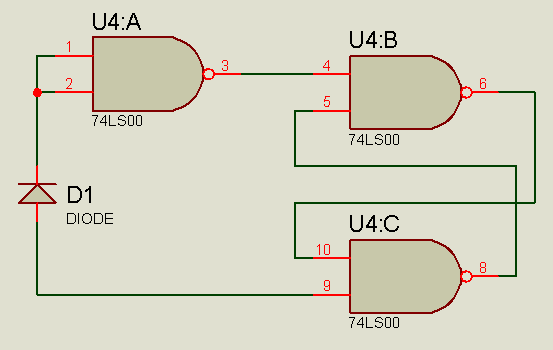

2. 整形电路

整形电路部分通过74LS00中的与非门按照图4连接,管脚1为输入信号,管脚6为输出信号。

图4 整形电路

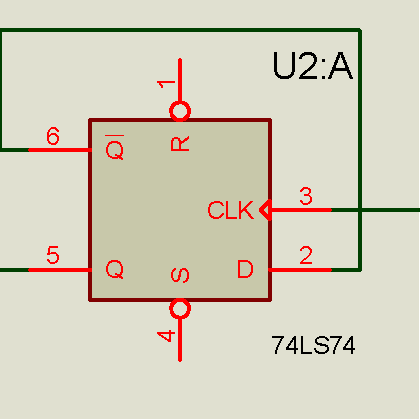

3. 二分频电路

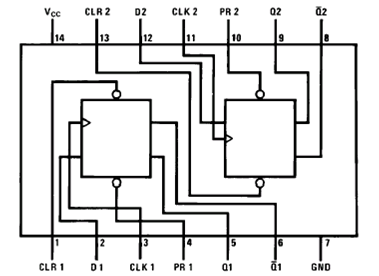

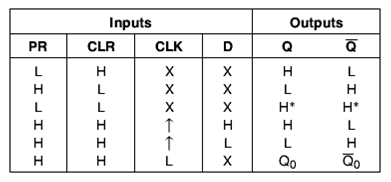

74LS74为带预置和清除端的两组D 型触发器,

图5 74LS74管脚图

图6 功能表

图7 二分频计

4. 单片机计数部分

1.AT89C52芯片介绍:

AT89C52是美国ATMEL 公司生产的低电压,高性能CMOS 8 位单片机,片内含4 kB 的可反复擦写的只读程序存储器(EPROM) 和128 B 的随机数据存储器(RAM) ,器件采用ATMEL 公司的高密度、非易失性存储技术生产,兼容标准MCS-51 指令系统,内置通用8 位中央处理器(CPU)和FLASH 存储单元

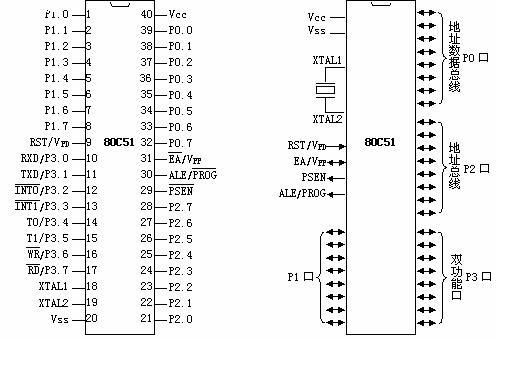

单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。

电源: VCC - 芯片电源,接+5V;

VSS - 接地端;

时钟: XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。

控制线: 控制线共有4根,

⑴ ALE/PROG:地址锁存允许/片内EPROM编程脉冲

① ALE功能:用来锁存P0口送出的低8位地址

② PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入 编程脉冲。

⑵ PSEN:外ROM读选通信号。

⑶ RST/VPD:复位/备用电源。

① RST(Reset)功能:复位信号输入端。

② VPD功能:在Vcc掉电情况下,接备用电源。

⑷ EA/Vpp:内外ROM选择/片内EPROM编程电源。

① EA功能:内外ROM选择端。

② Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。

I/O线: 80C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。

RST/VPD: 复位/备用电源。

① RST(Reset)功能:复位信号输入端。

② VPD功能:在Vcc掉电情况下,接备用电源。

EA/Vpp: 内外ROM选择/片内EPROM编程电源。

① EA功能:内外ROM选择端。

② Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。

图8 单片机管脚图

2. 单片机应用管脚应用:

p0口作为lcd1602的数据口

lcd的rs由单片机的p2.0控制

lcd的rw由单片机的p2.1控制

lcd的en由单片机的p2.2控制

利用单片机的T0口定时模式

利用单片机的T1口为计数模式

由外部电路与单片组成的复位电路

利用外部晶振12MHZ为单片机提供时钟频率

3. 软件设计:

程序流程图:(程序见附录)

5.液晶显示部分

1. LCD1602液晶屏介绍:工业字符型液晶,能够同时显示16x02即32个字符。(16列2行)

注:为了表示的方便 ,后文皆以1表示高电平,0表示低电平。

1602液晶也叫1602字符型液晶它是一种专门用来显示字母、数字、符号等的点阵型液晶模块它有若干个5X7或者5X11等点阵字符位组成,每个点阵字符位都可以显示一个字符。每位之间有一个点距的间隔每行之间也有间隔起到了字符间距和行间距的作用,正因为如此所以他不能显示图形

1602LCD是指显示的内容为16X2,即可以显示两行,每行16个字符液晶模块(显示字符和数字)。

2. 管脚功能:

1602采用标准的16脚接口,其中:

第1脚:VSS为电源地

第2脚:VDD接5V电源正极

第3脚:V0为液晶显示器对比度调整端,接正电源时对比度最弱,接地电源时对比度最高(对比度过高时会 产生“鬼影”,使用时可以通过一个10K的电位器调整对比度)。

第4脚:RS为寄存器选择,高电平1时选择数据寄存器、低电平0时选择指令寄存器。

第5脚篟W为读写信号线,高电平(1)时进行读操作,低电平(0)时进行写操作。

第6脚:E(或EN)端为使能(enable)端。

第7~14脚:D0~D7为8位双向数据端。

第15~16脚:空脚或背灯电源。15脚背光正极,16脚背光负极。

图9 单片机部分电路

三.系统测试

1.调试仪器

示波器,电源,函数信号发生器

2.测试结果分析

3.误差分析

当频率越高时,误差越大。可能是由于51单片机本身计数的限制和其他噪声信号对高频信号的干扰引起的。

而对于低频信号,误差相对很小。误差主要来源于元器件本身的误差。

四.总结

该数字频率计经过实际检验说明:具有精度高、使用方便、显示直观、硬件电路简单等特点。在本次设计中遇到了许多的困难——仿真与实物无法有机的结合,程序显示无法达到要求……这些困难都基本克服,但波形产生电路中还有缺陷——高频信号会有失真,但对设计总体影响不大。经过这次设计有效地提高了我们实践动手能力,对我们今后的学习和生活有很大的积极影响。

参考资料

1. 康华光 电子技术基础(模拟部分)第五版 高等教育出版社

2. 康华光 电子技术基础(数字部分)第五版 高等教育出版社

3. 汪文 陈林 单片机原理及应用 华中科技大学出版社

4. 李强 51系列单片机编程技术 北京航空航天大学出版社

附录

LCD_RS EQU P2.0

LCD_RW EQU P2.1

LCD_EN EQU P2.2

ORG 0000H

JMP MAIN

ORG 000BH

JMP T0_INT

ORG 0030H

MAIN:

LCALL PRO_SET

CALL SET_LCD

LOOP5:

CALL INIT_TI

CALL ZHUANGHUA

CALL FUZHI

CALL LCE_FRE

SJMP LOOP5

;初始化程序

;-----------------------------------------------------------

PRO_SET:

MOV P0,#0FFH

MOV P1,#0FFH

MOV P2,#0FFH

SETB P3.5 ;P3.5 端口置输入状态

RET ;T1(TIMER1 的外部输入脚)

;----------------------------------------------------

;LCD 初始化设置

;----------------------------------------------------

SET_LCD:

CLR LCD_EN

CALL INIT_LCD

CALL DELAY1

MOV DPTR,#INFO1

MOV A,#1

CALL LCD_SHOW

MOV DPTR,#INFO2

MOV A,#2

CALL LCD_SHOW

RET

;----------------------------------------------------

INFO1: DB " GROUP OF 3B",0 ;LCD 第一行显示信息

INFO2: DB "FRE:",0 ;LCD 第二行显示信息

;----------------------------------------------------

;LCD 接口初始化

;8 位 I/O 控制

;----------------------------------------------------

INIT_LCD:

MOV A,#38H ;双列显示,字形 5*7 点阵

CALL WCOM

CALL DELAY1

MOV A,#0EH ;开显示,关光标,

CALL WCOM

CALL DELAY1

MOV A,#01H ;清除 LCD 显示屏

CALL WCOM

CALL DELAY1

MOV A,#06H

CALL WCOM

CALL DELAY1

RET

;---------------------------------------------------

LCD_SHOW: ;在 LCD 的第一行或第二行显示信息字符

CJNE A,#1,LINE2 ;判断是否为第一行

LINE1:

MOV A,#01H

CALL WCOM

MOV A,#80H

CALL WCOM

JMP FILL

LINE2:

MOV A,#0C0H

CALL WCOM

FILL:

CLR A

MOVC A,@A+DPTR

CJNE A,#0,LC1

RET

LC1:

CALL WDATA

INC DPTR

JMP FILL

RET

;---------------------------------------------------

;写入命令子程序

;---------------------------------------------------

WCOM:

MOV P0,A

CLR LCD_RS

CLR LCD_RW

SETB LCD_EN

CALL DELAY0

CLR LCD_EN

RET

;---------------------------------------------------

;写入数据子程序

;---------------------------------------------------

WDATA:

MOV P0,A

SETB LCD_RS

CLR LCD_RW

SETB LCD_EN

CALL DELAY0

CLR LCD_EN

RET

INIT_TI:

MOV TMOD,#51H ;/*01010001 T1计数,T0定时*/

MOV TH0, #HIGH(65536 - 49988) ;50ms@12MHz

MOV TL0, #LOW (65536 - 49988)

MOV TH1, #00H

MOV TL1, #00H

MOV R6,#0

SETB ET0

SETB EA

MOV R7, #20

SETB TR0

SETB TR1

COUNT1:

JBC TF1,LOOP0

MOV A,R7

JZ TEND

SJMP COUNT1

LOOP0:

INC R6

MOV A,R7

JZ TEND

SJMP COUNT1 ; MOV R0,#01; MOV R1,#00H R1为高8位,r0为低8位

TEND: RET

T0_INT: ;中断

DJNZ R7,T0_END

CLR TR1

CLR TR0

JMP TIAO

T0_END: ;50ms执行一次

MOV TH0, #HIGH(65536 - 49988) ;50ms@12MHz

MOV TL0, #LOW (65536 - 49988)

TIAO:

RETI

ZHUANGHUA:

CLR A

MOV R0,TL1

MOV A,R0

MOV R1,#00H

SUBB A,R1

MOV R0,A

CLR A

MOV R1,TH1

MOV A,R0

ADD A,R0

MOV R0,A

MOV A,R1

ADDC A,R1

MOV R1,A

MOV A,R6

ADDC A,R6

MOV R6,A

MOV R4,#0FFH

MOV R5,#0FFH

LCALL QMUL

MOV R0, 3AH

MOV R1, 39H

MOV R2, 38H

lCALL HEX2BCD ;调用子程序把R0 R1 R2中的数字,转换成BCD码,送到R4 R5 R6 R7

RET

QMUL:

MOV A,R4

MOV B,R6

MUL AB

MOV R3,A ;(R3)=(R4*R6)L

MOV R4,B ;(R3)=(R4*R6)B

MOV A,R5

MOV B,R6

MUL AB

ADD A,R4

MOV R4,A

CLR A

ADDC A,B

MOV R5,A

CLR A

MOV A,R3

ADD A,R0

MOV 38H,A

CLR A

MOV A,R1

ADDC A,R4

MOV 39H,A

CLR A

ADDC A,R5

MOV 3AH,A

RET

HEX2BCD:

CLR A

MOV R4, A ;先清零

MOV R5, A

MOV R6, A

MOV R7, A

MOV R3, #24 ;共转换24位数

LOOP3:

CLR C

MOV A, R2

RLC A

MOV R2, A

MOV A, R1

RLC A

MOV R1, A

MOV A, R0

RLC A

MOV R0, A

MOV A, R7 ;送到BCD码的低端

ADDC A, R7 ;带进位加。自身相加,相当于左移一位

DA A ;十进制调整,变成BCD码

MOV R7, A

MOV A, R6

ADDC A, R6

DA A

MOV R6, A

MOV A, R5

ADDC A, R5

DA A

MOV R5, A

MOV A, R4

ADDC A, R4

MOV R4, A

DJNZ R3, LOOP3 ;共转换24位数

RET

FUZHI:MOV A, R7

MOV B, #16

DIV AB ;除以16,目的是分离出高、低四位

MOV 31H, A ;存放十位

MOV 30H, B ;存放个位

MOV A, R6

MOV B, #16

DIV AB

MOV 33H, A

MOV 32H, B

MOV A, R4

MOV 36H, A ;存放百万位

MOV A, R5

MOV B, #16

DIV AB

MOV 35H, A

MOV 34H, B

RET

PRO_SETS:

MOV 30H,#00H

MOV 31H,#00H

MOV 32H,#00H

MOV 33H,#00H

MOV 34H,#00H

MOV 35H,#00H

MOV 36H,#00H

RET

;显示各位数字

;-----------------------------------

LCE_FRE:

MOV A,#0C5H

CALL WCOM

MOV R1,#36H

LOOP1:

MOV A,@R1

ADD A,#30H

CALL WDATA;

DEC R1;

CJNE R1,#2FH,LOOP1

RET

DELAY0: ;

MOV R7,#250

DJNZ R7,$

RET

DELAY1: ;延时3ms

MOV R6,#15

D2:

MOV R7,#100

DJNZ R7,$

DJNZ R6,D2

RET

END