实验四数字频率计设计(1)

【实验目的】

1. 掌握数字频率计的Verilog描述方法;

2. 学习设计仿真工具的使用方法;

3. 学习层次化设计方法;

【实验内容】

1. 用4位十进制计数器对用户输入时钟进行计数,计数间隔为1秒,计数满1秒后将计数值(即频率值)锁存到4位寄存器中显示,并将计数器清0,再进行下一次计数。

2. 为上述设计建立元件符号

【实验原理】

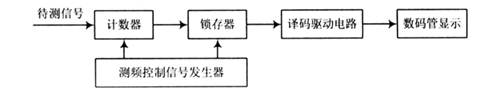

根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1S的输入信号脉冲计数允许的信号;一秒计数结束后,计数值被锁入锁存器,计数器清零,为下一测频技术周期做好准备。

【程序源代码】(加注释)

【一】

module CNTL(CLK,CNL_EN,RST_CNL,LOAD); //控制器模块

input CLK; //输入控制模块的计数器时钟

output CNL_EN,RST_CNL,LOAD; //输出使能、复位、装载信号

reg CLK2DIV,CNL_EN,LOAD,RST_CNL; //寄存器类型

always @(posedge CLK)

begin

CLK2DIV=~CLK2DIV; //分频器取反

end

always @(posedge CLK) //产生使能信号和装载信号

begin

CNL_EN=CLK2DIV; //使能信号赋值

LOAD=~CLK2DIV; //装载信号赋值

end

always @(CLK) //产生复位信号

begin

if(CLK==1'b0&&CNL_EN==1'b0)

RST_CNL=1; //复位信号置一

else

RST_CNL=0; //复位信号清零

end

endmodule

【二】

module CNT10(CLK,RST,EN,COUT,DOUT); //计数器模块

input CLK,RST,EN;

output COUT; //输出进位信号

output[3:0] DOUT;

reg[3:0] Q; //中间变量

reg COUT;

assign DOUT=Q;

always @(posedge CLK or posedge RST) //中间变量Q的产生

begin

if(RST)

Q=0; //Q被置为零

else if(EN)

if(Q<9)

Q=Q+1; //循环计数

else Q=0;

end

always @(Q) //Q为时钟控制信号,电平触发,产生进位信号

begin

if(Q==4'b1001)

COUT=1; //计数器已计满一周期

else

COUT=0; //计数器没计满

end

endmodule

【三】

module RGB4(DIN,LOAD,DOUT); //锁存器模块

input LOAD;

input[3:0] DIN;

output[3:0] DOUT;

reg[3:0] DOUT;

always @(posedge LOAD) //LOAD为时钟控制信号,产生输出信号

DOUT=DIN; //输出赋值

endmodule

【四】

module freg(CLK1HZ,UCLK,led0,led1,led2,led3,rst,en,load); //主模块

input CLK1HZ,UCLK; //输入信号

output[3:0] led0,led1,led2,led3;

output rst,en,load;

wire in_load,in_rst,in_en; //定义为网线性

wire[3:0] dout0,dout1,dout2,dout3; //定义为网线性

wire c0,c1,c2;

assign rst=in_rst,load=in_load,en=in_en; //给信号赋值

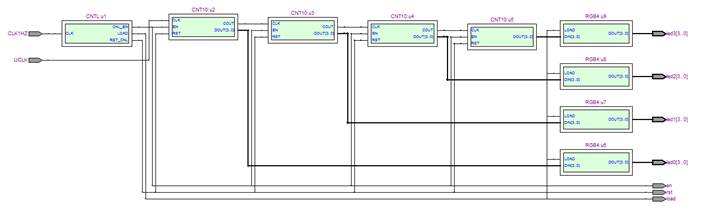

CNTL u1(.CLK(CLK1HZ),.CNL_EN(in_en),.RST_CNL(in_rst),.LOAD(in_load)); //元件例化(控制模块)

CNT10 u2(.CLK(UCLK),.EN(in_en),.RST(in_rst),.COUT(c0),.DOUT(dout0)); //元件例化(计数模块)

CNT10 u3(.CLK(c0),.EN(in_en),.RST(in_rst),.COUT(c1),.DOUT(dout1)); //元件例化(计数模块)

CNT10 u4(.CLK(c1),.EN(in_en),.RST(in_rst),.COUT(c2),.DOUT(dout2)); //元件例化(计数模块)

CNT10 u5(.CLK(c2),.EN(in_en),.RST(in_rst),.DOUT(dout3)); //元件例化(计数模块)

RGB4 u6(.DIN(dout0),.LOAD(in_load),.DOUT(led0)); //元件例化(锁存器模块)

RGB4 u7(.DIN(dout1),.LOAD(in_load),.DOUT(led1)); //元件例化(锁存器模块)

RGB4 u8(.DIN(dout2),.LOAD(in_load),.DOUT(led2)); //元件例化(锁存器模块)

RGB4 u9(.DIN(dout3),.LOAD(in_load),.DOUT(led3)); //元件例化(锁存器模块)

endmodule

【元件符号与总框图】

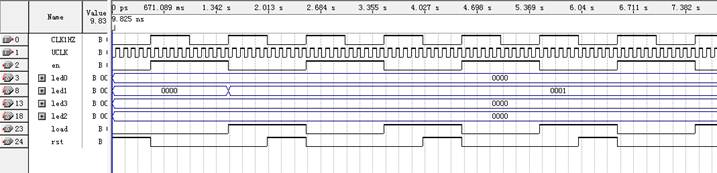

仿真结果:

由此图可以看出,CLK1HZ是周期为1S的时钟脉冲,为上升沿,是频率的时钟信号;UCLK是周期为100ms的时钟脉冲,它是输入变量,此模块的功能就是对UCLK进行频率测量;EN为使能信号,RST为复位信号,LOAD为装载信号,此模块通过CLK2DIV信号产生这些信号,其中当CLK有效时,把CLK2DIV赋值给EN ,把CLK2DIV取反以后赋值给LOAD信号,当CLK为低电平而且EN为低电平时,对RST赋值。led0,led1,led2,led3为频率计量的结果,是输出变量,因为UCLK为10ms,相当于为100hz,因此输出为0100。

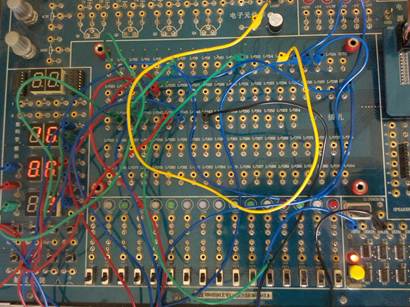

硬件仿真结果:

【实验心得和体会】

通过对频率计的设计,让我更深入地了解了QUARTUS软件的应用,进一步熟悉其操作系统,也更深入地了解了频率计的原理与应用。和同学一块做实验,中间遇到很多问题,磕磕绊绊,但彼此间的协作,加快了我们的进程。

第二篇:数字频率计实验报告

大连理工大学城市学院

数字电路与系统课程设计

设计题目:数字频率计

学 院:电子与自动化学院

专 业: 自动化

学 生: 揣智涵

同 组 人: 王晓宁 周英茹

指导教师: 于海霞

完成日期: 20##年3月26日

目 录

第一章 设计任务

1.1项目名称

1.2项目设计说明

1.2.1设计任务和要求

1.2.2进度安排

1.3项目总体功能模块图

第二章 需求分析

2.1问题基本描述

(要求分析得出整个系统流程图)

2.2系统模块分解及各模块功能的基本要求

第三章 设计原理

3.1 设计原理

3.2 MAXPLUSII介绍

第四章 系统功能模块设计

4.1 FEN模块

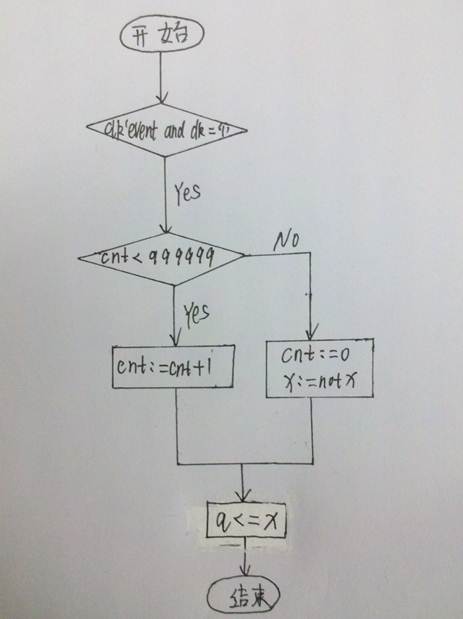

4.1.1 FEN模块流程图

4.1.2 输入输出引脚及其功能说明

4.1.3 程序代码实现

4.2 SEL模块

4.2.1 SEL模块流程图

4.2.2输入输出引脚及其功能说明

4.2.3程序代码实现

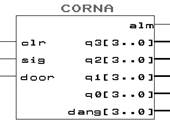

4.3 CORNA模块

4.3.1 CORNA模块流程图

4.3.2 输入输出引脚及其功能说明

4.3.3 程序代码实现

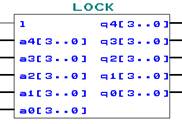

4.4 LOCK模块

4.4.1 LOCK模块流程图

4.4.2 输入输出引脚及其功能说明

4.4.3 程序代码实现

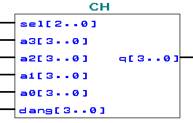

4.5 CH模块

4.5.1 输入输出引脚及其功能说明

4.5.2 程序代码实现

4.6 DISP模块

4.6.1 输入输出引脚及其功能说明

4.6.2 程序代码实现

第五章调试并分析结果

5.1输入说明

5.2预计输出

5.3测试结果记录

5.4测试结果分析

第六章 结论

心得体会

参考文献

第一章 设计任务

1.1 项目名称:数字频率计

1.2 项目设计说明

1.2.1 设计任务和要求

此频率计共分4档:

一档:0~9999Hz;

二档:10~99.99kHZ;

三档:100.0~999.9kHz;,

四档:1.000~999MHz;

在换挡的设计方面,此程序突破了以往改变闸门时间的方法,使自动换挡的实现更加简单可靠。

1.2.2 进度安排

第一节课:画出模块及程序流程图

第二节课:调试各模块程序使其无误

第三节课:连接整个程序并下载到试验箱是数字频率计的功能实现

第四节课:改进程序设计实现创新,然后完成课程设计报告

第五节课:完成答辩

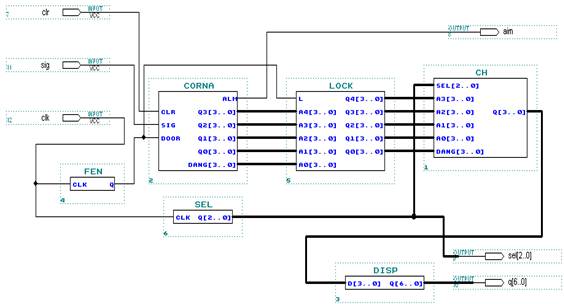

1.3 项目总体功能模块图如下

图1-1

第二章 需求分析

2.1 问题基本描述

所谓频率,就是周期信号在单位时间(1秒)内变化的次数。频率计的测量范围为1MHZ,为了测量精确量程分别为10KHZ,100KHZ,1000KHZ和1MHZ四个档。即最大读数分别为9.999KHZ,99.99KHZ,999.9KHZ,999MHZ。要求两成自动换挡。其具体功能如下:

(1) 当量程超过999时,自动增大一档,下一次测量时量程大一档;

(2) 当超过测量范围时,显示溢出,报警器报警。

(3) 小数点位置随量程变化自动移位。

(4) 采用记忆显示方法,在测量过程中不显示数据,在测量完成以后显示测频结果,并将此结果 保存到下次测量结束,显示时间不少于1秒。

(5) 根据频率计的测频原理,可以选择合适的时基信号即阀门时间,对输入信号脉冲进行计数,实现测频的目的。

(6) 根据数字频率计的设计原理,可以将数字频率计设计分为五个模块来实现其功能。即分频模块,控制模块,计数模块,锁存模块和显示模块。用CLDH语言进行编程。

(7) 弄清什么情况下是测频率,就是选择合适的时基信号的问题。测频率时以输入信号作为时钟信号,因为输入信号的频率大于频率计的基准频率。

:

数字频率计的系统流程图如下

图2-1

2.2 系统模块分解及各模块功能的基本要求

计数器在各个档是被反复应用的,如果在各个档分别设计计数器就造成资源的浪费,而且在测周期和频率的时候,计数器的时基信号和输入信号要进行调换,但计数功能是一样的,所以将计数器设为单独的模块。七段译码器也是被重复使用的,也设成单独的模块,这样的话就不用在重复使用的时候重复书写译码电路了。总体来说数字频率计分为五个模块来设计,即分频模块计数

模块,锁存模块,预测控制信号发生器,显示模块。

分频模块为计数模块提供1秒的阀门时间。计数模块是整个程序的核心,它完成在1秒的时间里对被测信号计数的功能,并通过选择输出数据实现自动换挡的功能。锁存模块在信号L的下降沿到来时将信号A4,A3,A2,A1锁存。显示模块对应于数码管片选信号,将相应的数据送出,其中档位也通过数码管显示。

第三章 设计原理

3.1 设计原理

众所周知,频率信号易于传输,抗干扰性强,可以获得较好的测量精度。因此,频率检测是电子测量领域最基本的测量之一。频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1 s。闸门时间可以根据需要取值,大于或小于1 s都可以。闸门时间越长,得到的频率值就越准确,但闸门时间越长,则每测一次频率的间隔就越长。闸门时间越短,测得的频率值刷新就越快,但测得的频率精度就受影响。一般取1 s作为闸门时间。

数字频率计的关键组成部分包括测频控制信号发生器、计数器、锁存器、译码驱动电路和显示电路,其原理框图如图3-1所示。

图3-1数字频率计原理图

3.2 MAXPLUSII介绍

MAX+PLUSⅡ(Multiple Array and Programming Logic User System)开发工具是Altera公司推出的一种EDA工具,具有灵活高效、使用便捷和易学易用等特点。Altera公司在推出各种CPLD的同时,也在不断地升级相应的开发工具软件,已从早起的第一代A+PLUS、第二代MAX+PLUS发展到第三代MAX+PLUSⅡ和第四代Quartus。使用MAX+PLUSⅡ软件,设计者无需精通器件内部的复杂结构,只需用业已熟悉的设计输入工具,如硬件描述语言、原理图等进行输入即可,MAX+PLUSⅡ就会自动将设计转换成目标文件下载到器件中去。MAX+PLUSⅡ开发系统具有以下特点。

(1) 多平台。MAX+PLUSⅡ软件可以在基于PC机的操作系统如Windows95、Windows98、Windows20##、Windows NT下运行,也可以在Sun SPAC station等工作站上运行。

(2) 开放的界面。MAX+PLUSⅡ提供了与其他设计输入、综合和校验工具的接口,借口符合EDIF 200/300、LPM、VHDL、Verilog-HDL等标准。目前MAX+PLUSⅡ所支持的主流第三方EDA工具主要有Synopsys、Viewlogic、Mentor、Graphics、Cadence、OrCAD、Xilinx等公司提供的工具。

(3) 模块组合式工具软件。MAX+PLUSⅡ具有一个完整的可编程逻辑设计环境,包括设计输入、设计处理、设计校验和下载编程4个模块,设计者可以按设计流程选择工作模块。

(4) 与结构无关。MAX+PLUSⅡ开发系统的核心——Compiler(编译器)能够自动完成逻辑综合和优化,它支持Altera的Classic、MAX7000、FLEX8000和FLEX10K等可编程器件系列,提供一个与结构无关的PLD开发环境。

(5) 支持硬件描述语言。MAX+PLUSⅡ支持各种HDL设计输入语言,包括VHDL、Verilog-HDL和Altera的硬件描述语言AHDL。

(6) 丰富的设计库。MAX+PLUSⅡ提供丰富的库单元供设计者调用,其中包括一些基本的逻辑单元,74系列的器件和多种特定功能的宏功能模块以及参数化的兆功能模块。调用库单元进行设计,可以大大减轻设计人员的工作量,缩短设计周期

。

第四章 系统功能模块

4.1 FEN 模块

4.1.1 FEN 模块流程图

图4-1

4.1.2输入输出引脚及其功能说明

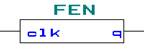

模块FEN如图9-87所示。通过对4MHz时钟的分频得到0.5Hz时钟,为模块CORNA提供1s的闸门时间。CLK:输入时钟信号;Q:输出分频后的基准信号。

程序代码的实现如下

library ieee;

library ieee;

use ieee.std_logic_1164.all;

entity fen is

port (clk:in std_logic;

q: out std_logic); 图4-2

end fen;

architecture fen_arc of fen is

begin

process(clk)

variable cnt: integer range 0 to 999999;

variable x: std_logic;

begin

if clk'event and clk = '1' then

if cnt<999999 then

cnt:=cnt+1;

else

cnt:=0;

x:= not x;

end if;

end if;

q<=x;

end process;

end fen_arc;

4.2 SEL模块

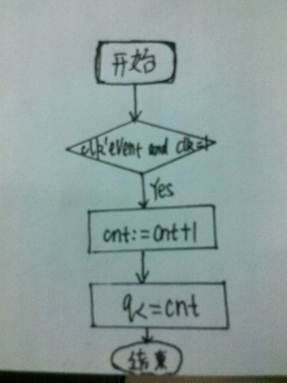

4.2.1 SEL 模块流程图

图4-3

4.2.2 SEL模块输入输出引脚及其功能说明

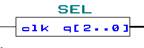

CLK:基准时钟信号; Q[2..0]:产生数码管的片选信号。

4.2.3 程序代码实现

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity sel is

port (clk: in std_logic; 图4-4

q:out std_logic_vector(2 downto 0));

end sel;

architecture sel_arc of sel is

begin

process(clk)

variable cnt:std_logic_vector(2 downto 0);

begin

if clk'event and clk='1' then

cnt:=cnt+1;

end if;

q<=cnt;

end process;

end sel_arc;

4.3 模块CORNA

4.3.1 CORNA 模块流程图

图4-5

4.3.2 输入输出引脚及其功能说明

该模块是整个程序的核心,它完成在1s的时间里对被测信号计数的功能,并通过选择输出数据实现自动换挡的功能输入输出引脚及其功能说明CLR:复位按钮;SIG:待测频率信号;DOOR:基准时钟频率;ALM:蜂鸣器;DANG[3..0]:档位值;Q0~4[3..0]:计算后的频率值。

4.3.3程序代码实现

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity corna is

port (clr,sig,door : in std_logic;

alm : out std_logic;

q3,q2,q1,q0,dang : out std_logic_vector(3 downto 0));

end corna;

architecture corn_arc of corna is

begin

process (door,sig)

variable c0,c1,c2,c3,c4,c5,c6: std_logic_vector (3 downto 0);

variable x:std_logic;

begin

if sig'event and sig='1' then

if door='1' then

if door='1' then

if c0<"1001"then

c0:=c0+1;

else

c0:="0000";

if c1<"1001" then

c1:=c1+1;

else

c1:="0000"; 图4-6

if c2<"1001" then

c2:=c2+1;

else

c2:="0000";

if c3<"1001" then

c3:=c3+1;

else

c3:="0000";

if c4<"1001" then

c4:=c4+1;

else

c4:="0000";

if c5<"1001" then

c5:=c5+1;

else

c5:="0000";

if c6<"1001" then

c6:=c6+1;

else

c6:="0000";

alm<='1';

end if;

end if;

end if;

end if;

end if;

end if;

end if;

else

if clr = '0' then

alm <= '0';

end if;

c6:="0000";

c5:="0000";

c4:="0000";

c3:="0000";

c2:="0000";

c1:="0000";

c0:="0000";

end if;

if c6/="0000" then

q3<=c6;

q2<=c5;

q1<=c4;

q0<=c3;

dang<="0100";

elsif c5/="0000" then

q3<=c5;

q2<=c4;

q1<=c3;

q0<=c2;

dang<="0011";

elsif c4/="0000" then

q3<=c4;

q2<=c3;

q1<=c2;

q0<=c1;

dang<="0010";

else

q3<=c3;

q2<=c2;

q1<=c1;

q0<=c0;

dang<="0001";

end if;

end if;

end process;

end corn_arc;

4.4 模块LOCK

4.4.1 LOCK 模块流程图

图4-7

4.4.2 输入输出引脚及其功能说明

该模块实现锁存器的功能,在信号L的下降沿到来时信号A4、A3、A2、A1锁存。输入输出引脚及其功能说明L:基准时钟信号;A0~4[3..0]:接受计数器CORNA传过来的值并锁存;Q0~4[3..0]:向数据选择器传值。

4.4.3 程序代码实现

library ieee;

use ieee.std_logic_1164.all;

entity lock is

port (l: in std_logic;

a4,a3,a2,a1,a0:in std_logic_vector(3 downto 0);

q4,q3,q2,q1,q0:out std_logic_vector(3 downto 0));

end lock;

architecture lock_arc of lock is

begin

process(l)

variable t4,t3,t2,t1,t0:std_logic_vector(3 downto 0);

begin

if l'event and l='0' then

t4:=a4;

t3:=a3;

t3:=a3;

t2:=a2;

t1:=a1;

t0:=a0;

end if;

q4<=t4;

q3<=t3;

q2<=t2;

q1<=t1;

q0<=t0;

end process; 图4-8

end lock_arc;4.5 模块CH

4.5.1 输入输出引脚及其功能说明

该模块对应于数码管片选信号,将相应的数据送出,其中档位也通过数码管显示。输入输出引脚及其功能说明SEL[2..0]:接受SEL模块传来的数码管片选信号;A[3..0]:接受锁存器传来的数码管片选信号;DANG[3..0]:接受锁存器传来的档位信号;Q[3..0]:传出数码管位选信号。

4.5.2 程序代码实现

library ieee;

use ieee.std_logic_1164.all;

entity ch is

port(sel:in std_logic_vector(2 downto 0);

a3,a2,a1,a0,dang:in std_logic_vector(3 downto 0);

q:out std_logic_vector(3 downto 0));

q:out std_logic_vector(3 downto 0));

end ch;

architecture ch_arc of ch is

begin

process(sel)

begin

case sel is

when "110" =>q<=a0;

when "010" =>q<=a1;

when "100" =>q<=a2; 图4-9

when "000" =>q<=a3;

when "101" =>q<=dang;

when others =>q<= "1111";

end case;

end process;

end ch_arc;

4.6 DISP模块

4.6.1输入输出引脚及其功能说明

D[3..0]:接受CH传出的数码管位选信号;Q[6..0]:译码出数码管位选信号;

4.6.2程序代码实现

use ieee.std_logic_1164.all;

entity disp is

port (d:in std_logic_vector(3 downto 0);

port (d:in std_logic_vector(3 downto 0);

q:out std_logic_vector(6 downto 0)); 图4-10

end disp;

architecture disp_arc of disp is

begin

process(d)

begin

case d is

when "0000" =>q<="0111111";

when "0001" =>q<="0000110";

when "0010" =>q<="1011011";

when "0011" =>q<="1001111";

when "0100" =>q<="1100110";

when "0101" =>q<="1101101";

when "0110" =>q<="1111101";

when "0111" =>q<="0100111";

when "1000" =>q<="1111111";

when "1001" =>q<="1101111";

when others =>q<="0000000";

end case;

end process;

end disp_arc;

第五章 调试并分析结果

5.1输入说明

SIG:接1KHz频率;CLR:接开关;CLK:接4MHz频率。

5.2预计输出

低两位数码管显示‘1’;高四位数码管显示‘1000’。

5.3 测试结果记录

低两位数码管显示‘1’;高四位数码管显示‘1000’。

5.4 测试结果分析

本频率计满足试验要求,使用周期和直接测量法进行测量,这样会减小误差。实验中也遇到了很多问题,在器件在线编程过程中,program各项操作无法进行,如果是首次编程,则需要设置下载端口,如果还比能进行操作,可能是芯片或者试验箱出现问题,所以应该换芯片或试验箱。在连接引脚是要特别注意 ,否则显示管无法显示。此外此试验还有需要改进的地方,比如测量频率的精度和灵敏度。

待测信号给的是1KHz,数码管档位显示为一档(0~9999Hz);频率显示为‘1000’;与预计输出完全一样。因为基准信号和待测信号是同一个信号源,故如此准确。也论证了上述设计的正确性。

图5-1

如上图,待测信号sig 10KHz,clk接1MHz显示如图,第一行和第二行为脉冲频率,第三行为档位,10KHz的待测信号档位为二档。

第六章 结论

心得体会

经过这次的实验课程设计,我学到了如何将多个程序绑在一起使用并构成一个完整的系统。在老师的指导下、在我们实验设计小组的共同努力下、在其他同学的热情帮助下,我们完整滴完成了《数字频率计》的设计、组装,并做了些创新。

虽然实验成功,我们同样在实验过程中遇到了一些问题:

1. 刚开始时候的设计是每组组员做一部分, 但是问题就是有些系数不能同一。因此造成了一开始实验进展缓慢。

2. 在实验过程中,器材的问题也被我们遇到了。因此也得到了些经验:要对自己的实验成果由信心,不要一出问题就从程序中找问题。可能对你最大的阻碍就是你没有考虑到的器材问题。

3. 在最后仿真时候,导线的顺序也是常出问题的地方。由于没有及时发现问题的所在,我们小组花费了整整一节课的时间在改程序,浪费了许多宝贵时间。

参考文献

【1】VHDL数字电路设计与应用与实践教程

【2】第2版王振红 主编机械工业出版社