CPLD/FPGA设计实验报告

实验名称: 时序电路设计基础

实验目的: 掌握Quartus II 软件的基本使用方法,完成基本时序电路设计

实验内容:

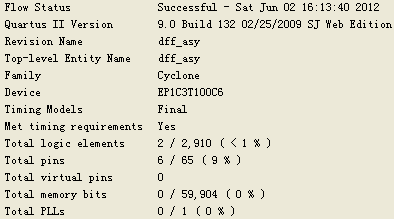

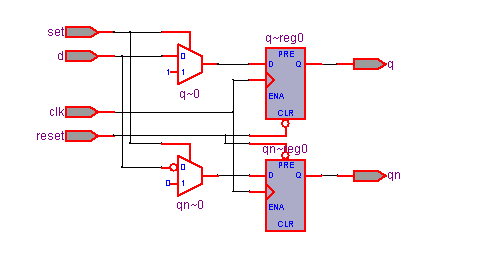

实验一 D触发器

一、 创建工程

工程名称:dff_asyn 顶层实体文件名:dff_asyn

器件: EP1C3T100C6 (要求:Cyclone系列任意器件)

二、 创建文件

创建Verilog HDL文件,实现同步置数异步清零带Q_n输出的D触发器。

module dff_asyn(q,qn,d,clk,set,reset);

input d,clk,set,reset;

output reg q,qn;

always @ (posedge clk or negedge reset)

begin

if (~reset)

begin

q<=1'b0;

qn<=1'b1;

end

else if (set)

begin

q<=1'b1;

qn<=1'b0;

end

else

begin

q<=d;

qn<=~d;

end

end

endmodule

三、 编译工程

报告中下列数据是多少

四、 仿真电路

1、创建VWF文件

2、设定“End Time”为20us

3、在VWF文件中添加Node OR Bus

4、编辑波形

5、仿真

6、画出仿真结果

实验二 数据选择器

一、 创建工程

工程名称: mux6_1 顶层实体文件名: mux6_1

器件: EP1C3T100C6 (要求:Cyclone系列任意器件)

二、 创建文件

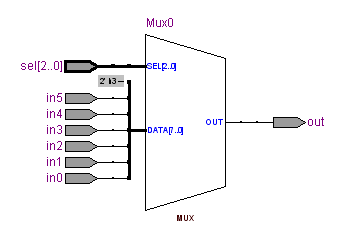

创建Verilog HDL文件,实现6选1数据选择器。

module mux6_1(out,in0,in1,in2,in3,in4,in5,sel);

input in0,in1,in2,in3,in4,in5;

input [2:0] sel;

output reg out;

always @ (in0,in1,in2,in3,in4,in5,sel)

case (sel)

3'b000: out=in0;

3'b001: out=in1;

3'b010: out=in2;

3'b011: out=in3;

3'b100: out=in4;

3'b101: out=in5;

default: out=3'b111;

endcase

endmodule

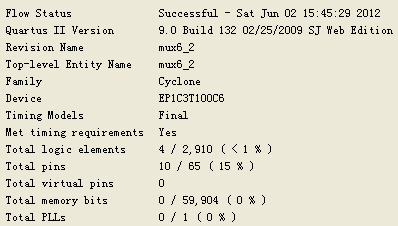

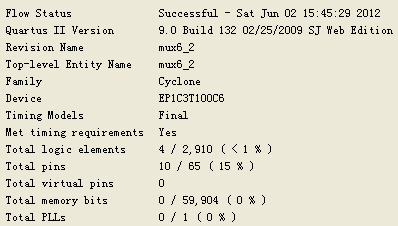

三、编译工程

报告中下列数据是多少

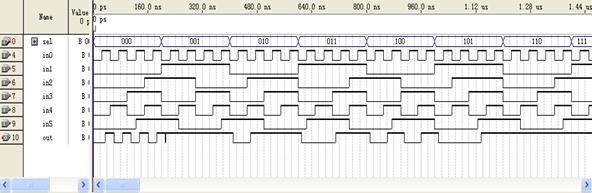

四、 仿真电路

1、创建VWF文件

2、设定“End Time”为20us

3、在VWF文件中添加Node OR Bus

4、编辑波形

5、仿真

6、画出仿真结果

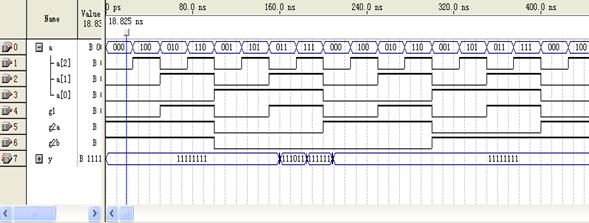

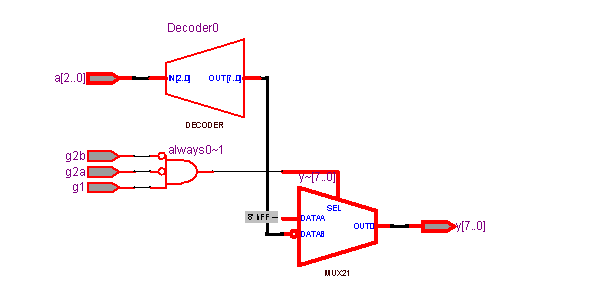

实验三 3-8译码器(使用Always语句实现)

一、创建工程

工程名称: tt74138 顶层实体文件名: tt74138

器件: EP1C3T100C6 (要求:Cyclone系列任意器件)

二、 创建文件

创建Verilog HDL文件,实现3-8译码器(使用Always语句实现)。

module tt74138(a,y,g1,g2a,g2b);

input [2:0] a;

input g1,g2a,g2b;

output reg [7:0] y;

always@ (a,y,g1,g2a,g2b)

begin

if (g1&~g2a & ~g2b)

begin case(a)

3'b000:y=8'b1111_1110;

3'b001:y=8'b1111_1101;

3'b010:y=8'b1111_1011;

3'b011:y=8'b1111_0111;

3'b100:y=8'b1110_1111;

3'b101:y=8'b1101_1111;

3'b110:y=8'b1011_1111;

3'b111:y=8'b0111_1111;

endcase

end

else y=8'b1111_1111;

end

endmodule

三、编译工程

报告中下列数据是多少

四、 仿真电路

1. 创建VWF文件

2. 设定“End Time”为20us

3. 在VWF文件中添加Node OR Bus

4. 编辑波形

5. 仿真

6. 画出仿真结果