上海电力学院

实验报告

实验课程名称: FPGA应用开发试验

实验项目名称:简单的组合逻辑电路设计

班 级:

姓名: 学号: 成绩:________ 实验时间:

一、实验目的

1、 掌握组合逻辑的设计方法。

2、 掌握组合逻辑电路的静态测试方法。

3、 加深PLD设计的过程,并比较原理图输入和文本输入的优劣。

二、实验原理

根据第三章学习的VHDL硬件描述语言来设计一定功能的电路。

三、实验步骤

1、 四舍五入判别电路

设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1,反之为0。

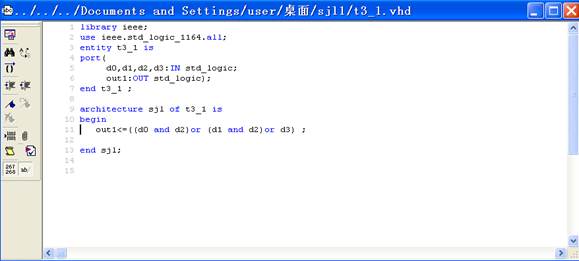

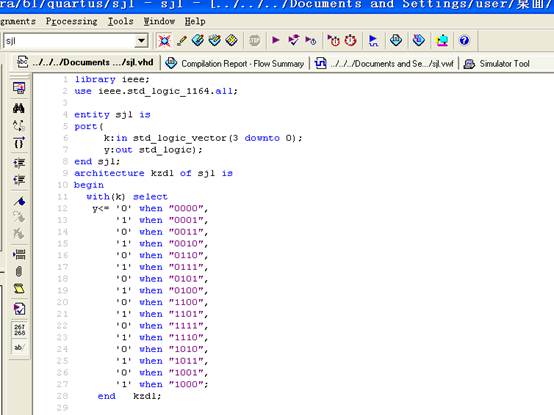

其VHDL描述语言为:

时序仿真波形为:

2、 控灯电路

设计四个开关控制一盏灯的逻辑电路,要求合任一开关,灯亮;断任一开关,灯灭。

其VHDL描述语言为:

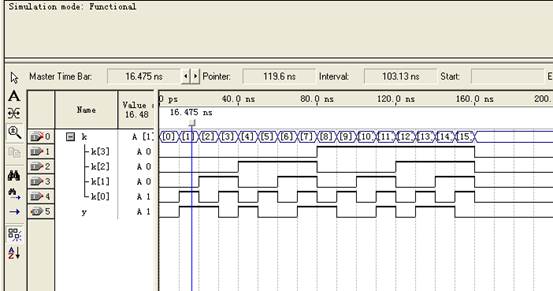

功能仿真波形为:

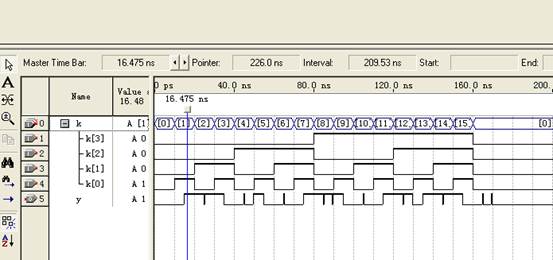

时序仿真波形:

引脚分配:

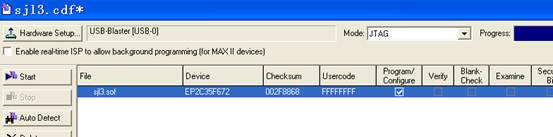

程序下载:

之后在DE2上验证,实验结果与设计要求一致。

3、 优先排队电路

设计一个优先排队电路,排队优先顺序依次为A,B,C要求输出端最高只能有一端为“1”,即只能为优先级较高的输入端对应的输出端为“1”。

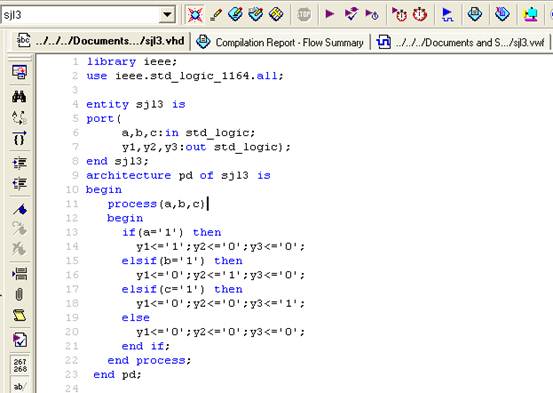

其VHDL描述语言为:

功能仿真波形为:

时序仿真波形:

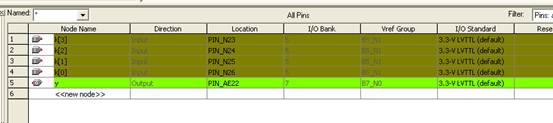

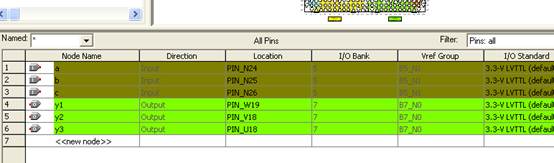

引脚分配:

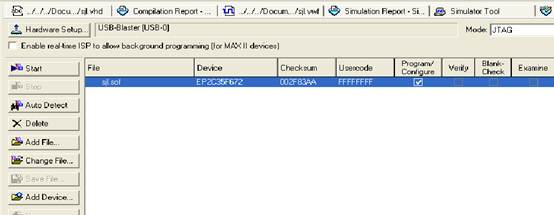

程序下载:

在DE2上验证,实验结果与设计要求一致。

实验连线:

1、四位拨码开关连d0,d1,d2,d3信号对应的管脚。

Out1输出信号管脚接LED灯。

2、四位按键开关分别连k0,k1,k2,k3信号对应的管脚。

y输出信号管脚接LED灯。

3、a ,b , c信号对应管脚分别连三个按键开关。

输出y1,y2,y3信号对应的管脚分别连三个LED灯。

五、实验小结

通过本次试验,我掌握了组合逻辑的基本设计方法。能够按照电路功能要求编写出基本的VHDL硬件描述语言,能合理的分配输入输出引脚,并能够在DE2上验证编写程序是否符合电路设计要求。当然,一开始又有对软件使用不熟练,也出现了一些问题,如引脚分配时未让输出对应LED灯,但是在自己的努力和多次实验的后,终于熟练起来。

第二篇:东南大学门电路和组合逻辑电路实验报告模板

东南大学电工电子实验中心

东南大学电工电子实验中心

实验报告

课程名称:

第 次实验

实验名称:

院 (系): 专 业:

姓 名: 学 号:

实 验 室: 实验组别:

同组人员: 实验时间: 年 月 日

评定成绩: 审阅教师:

一、实验目的

二、实验原理

三、预习思考题

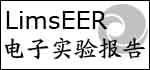

1、下图中的两个电路在实际工程中经常用到,其中反相器为74LS04,电路中的电阻起到了保证输出电平的作用。分析电路原理,并根据器件的直流特性计算电阻值的取值范围。

答:①电路(a)使用条件是驱动门电路固定输出为低电平

②电路(b)使用条件是驱动门电路固定输出为高电平

2、下图中的电阻起到了限制前一级输出电流的作用,根据器件的直流特性计算电阻值的取值范围。

答:

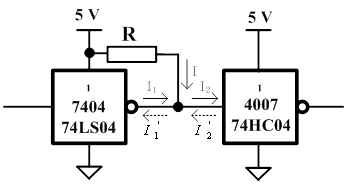

3、图2.4.1 用上拉电阻抬高输出电平中,R的取值必须根据器件的静态直流特性来计算,试计算R的取值范围。

图2.4.1 用上拉电阻抬高输出电平

答:

4、图2.4.3(a)中OC外接上拉电阻的值必须取的合适,试计算在这个电路中R的取值范围。

(a) OC门做驱动

答:

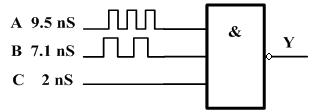

5、下图中A、B、C三个信号经过不同的传输路径传送到与门的输入端,其中计数器为顺序循环计数,即从000顺序计到111,C为高位,A为低位。A、B、C的传输延分别为9.5nS、7.1nS和2nS。试分析这个电路在哪些情况下会出现竞争-冒险,产生的毛刺宽度分别是多少。

答:

四、实验内容

必做实验:

A)2.5节 实验:门电路静态特性的测试

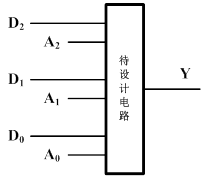

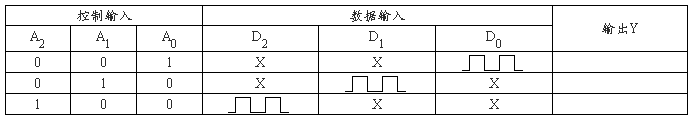

内容7.用OC门实现三路信号分时传送的总线结构框图如图2.5.4所示,功能如表2.5.2所示。(注意OC门必须外接负载电阻和电源,EC取5V)

图2.5.4 三路分时总线原理框图

① 查询相关器件的数据手册,计算OC门外接负载电阻的取值范围,选择适中的电阻值,连接电路。

答:详细计算步骤:

电路图:

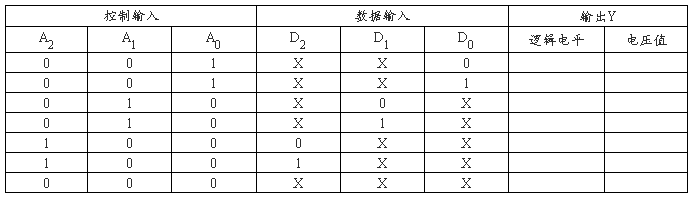

② 静态验证:控制输入和数据输入端加高低电平,用电压表测量输出高低电平的电压值,注意测量A2A1A0=000时的输出值。

答:

数据分析:

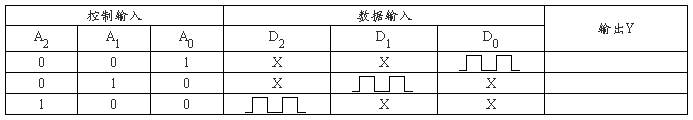

③ 动态验证:控制输入加高低电平,数据输入端加连续脉冲信号,用示波器双踪显示输入和输出波形,测量波形的峰峰值、高电平电压和低电平电压,对结果进行分析并解释为什么要选择“DC”。

答:

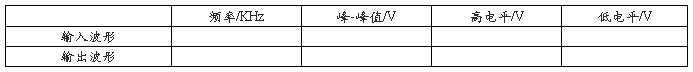

波形参数如下:

波形显示如下:

数据分析:

④ 器件电源电压VCC仍为5V,将EC改为10V,重复①和②,分析两者的差别。注意,不要直接将VCC改为10V,避免烧毁器件。

答:(同学们自己设计表格,进行数据分析比较,得出结论)

内容8.用三态门实现实验内容7三路信号分时传输

① 重复实验内容7中的②和③,注意不要同时将两个或两个以上的三态门的控制端处于使能状态。

答: 电路图:

静态验证:

数据分析:

动态验证:

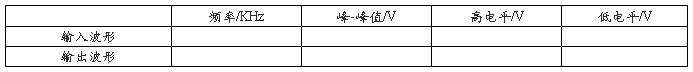

波形参数如下:

波形显示如下:

数据分析:

② 将A2A1A0设为“000”, D2D1D0设为“111”,此时输出端为高阻状态,测量输出端电压值,总结如何用万用表判断高阻态。

答:

③ 将A2A1A0设为“011”, D2D1D0设为“010”,此时破坏了三态门的使用规则,测量输出端电压值,总结如何用万用表判断两个或两个以上普通门输出端短接。(在测量的时候应该尽量缩短两个控制端属于使能状态的时间)。

答:

B)2.7节 实验:门电路动态特性测试

内容1.用环形振荡器测量74LS04、74HC04的传输延时时间

答:

内容2.在74LS04传输延时测量电路中加入长导线,观察延时造成的振荡周期变化

答:

C)2.10节 实验:SSI组合逻辑设计及竞争-冒险现象

内容5.竞争-冒险现象的观察和消除(具体内容有所修改,请参看教学网站相关内容)

答:

选做实验:

① 2.5节 实验:门电路静态特性的测试

内容2.分别测量74LS04和74HC04的静态参数极限值,并计算噪声容限和扇出数

内容4.用74LS04和74HC04门电路驱动发光二极管

内容5.观察叠加交流噪声信号的影响(74LS04)

内容6.TTL门驱动CMOS门实验

② 2.7节 实验:门电路动态特性测试

内容3.测量增加RC负载后的环形振荡器,RC负载对传输延时的影响

③ 2.10节 实验:SSI组合逻辑设计及竞争-冒险现象

内容1.数值判别电路

内容4.停车场交通控制系统