广西大学实验报告纸

_______________________________________________________________________________

实验内容___________________________________________指导老师

【实验名称】

组合逻辑电路的设计

【实验目的】

学习组合逻辑电路的设计与测试方法。

【设计任务】

用四-二输入与非门设计一个4人无弃权表决电路(多数赞成则提案通过)。

要求:采用四-二输入与非门74LS00实现;使用的集成电路芯片种类尽可能的少。

【实验用仪器、仪表】

数字电路实验箱、万用表、74LS00。

【设计过程】

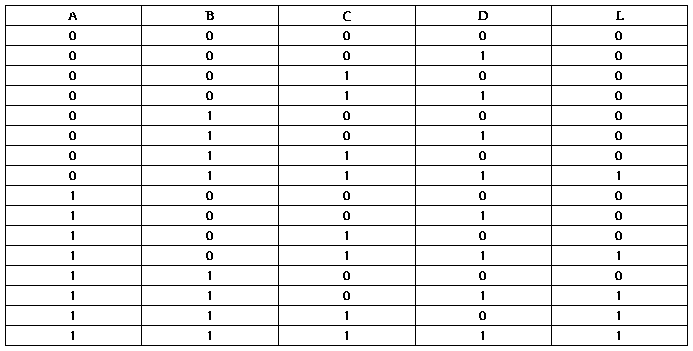

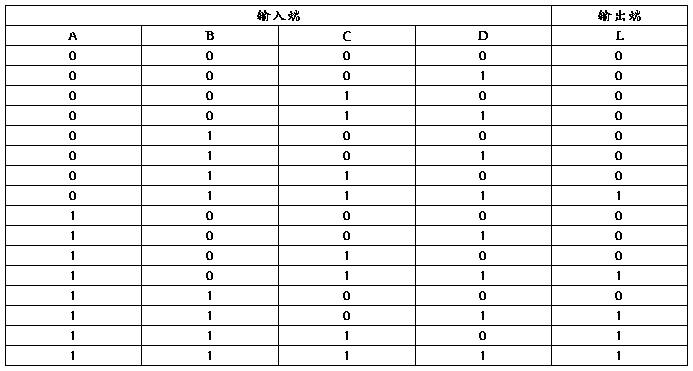

设输入为A、B、C、D,输出为L,根据要求列出真值表如下

真值表

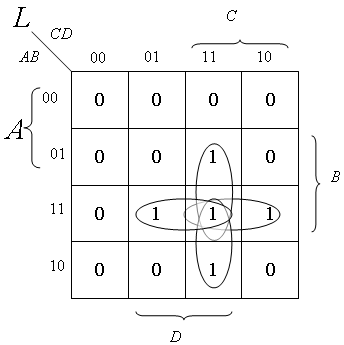

根据真值表画卡若图如下

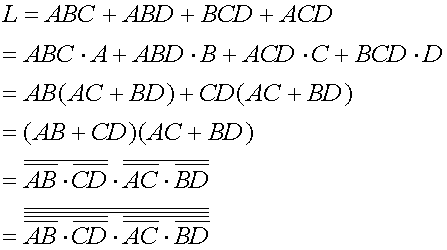

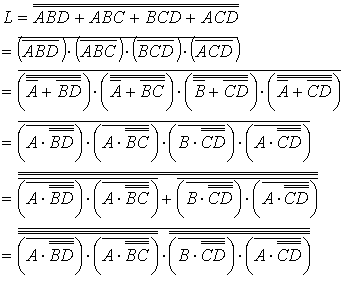

由卡若图得逻辑表达式

用四二输入与非门实现

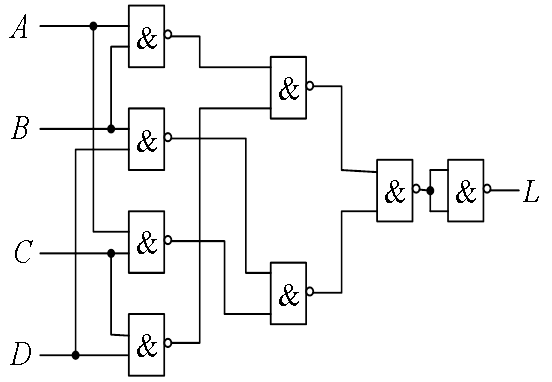

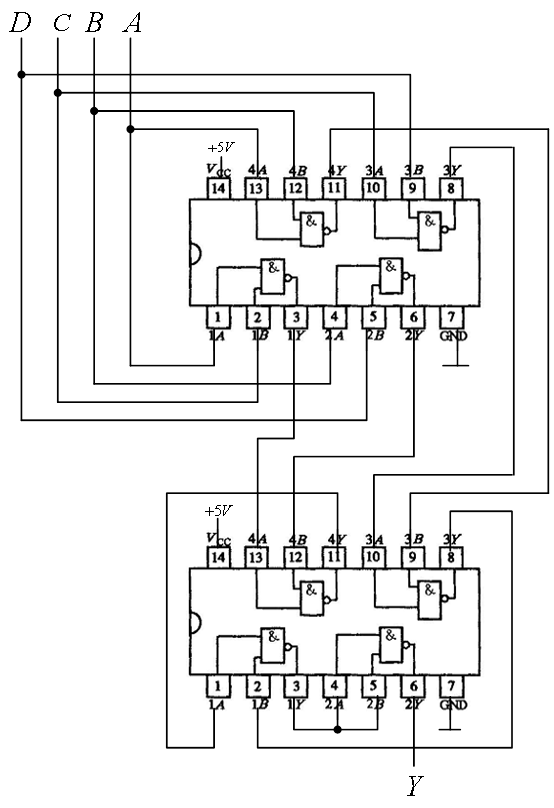

实验逻辑电路图

实验线路图

实验线路图

【实验步骤】

1. 打开数字电路实验箱,按下总电源开关按钮。

2. 观察实验箱,看本实验所用的芯片、电压接口、接地接口的位置。

3. 检查芯片是否正常。芯片内的每个与非门都必须一个个地测试,以保证芯片能正常工作。

4. 检查所需导线是否正常。将单根导线一端接发光二极管,另一端接高电平。若发光二极管亮,说明导线是正常的;若发光二极管不亮时,说明导线不导通。不导通的导线不应用于实验。

5. 按实验线路图所示线路接线。

6. 接好线后,按真值表的输入依次输入A、B、C、D四个信号,“1”代表输入高电平,“0”代表输入低电平。输出端接发光二极管,若输出端发光二极管亮则说明输出高电平,对应记录输出结果为“1” ;发光二极管不亮则说明输出低电平,对应记录输出结果为“0” 。本实验有四个输入端则对应的组合情况有16种,将每种情况测得的实验结果记录在实验数据表格中。

测量结果见下表:

实验数据表格

【分析实验结果】

1. 实验记录的数据表格得出的真值表与设计过程中的真值表完全一致,实验结果与理论设计及其要求一致。说明实验成功的用74LS00设计出了一个4人无弃权表决电路并实现其功能:多数赞成则提案通过。

2. 由实验结果可知:只有A、B、C、D中三个或三个以上输入高电平“1”时,发光二极管才发光,即输出“1” 。说明本设计符合理论设计要求。

【实验总结】

1. 做实验设计时,应该按步骤设计:列真值表→根据真值画卡若图列出逻辑函数表达式并化简→根据化简了的逻辑表达式画出逻辑电路图→选择适当的电路芯片合理布线设计实验线路。

2. 实验设计选择电路芯片时,应该先了解芯片的构造,原理,主要用途。熟悉芯片各引脚对应的输入或输出内容。本实验要求使用用74LS00芯片,74LS00芯片是由4个二输入与非门构成的。

3. 通过设计了解到74LS00芯片是4个二输入的与非门的集成,以后的实验若要用到与非门即可利用74LS00芯片实现。

4. 做实验时需要用到很多的连接导线,在连接导线时一定要小心、耐心,根据逻辑表达式可以直接接线,但是容易接错。最快捷的接法是将芯片引脚对应逻辑电路图的输入输出端分别编号,接线时就可以直接按编号接。

5. 我在设计实验时的实现方案中没有将逻辑表达式化到最简,形式非常复杂,最后导致实验逻辑图也是非常复杂。化简过程如下:

最后需要用到15个与非门,要4个74LS00芯片来实现。本实验室的数字电路实验箱只提供2块74LS00芯片,做实验时上述方案根本无法实现。后来在实验指导老师的耐心指导下,我改进了设计方案,即本实验报告的设计方案,改进后的方案只用8个与非门,2块74LS00芯片即可实现。 所以逻辑表达式的化简对于逻辑电路的设计非常重要。设计逻辑表达式尽量化简到最简,使实验设计方案尽量最简。若设计的电子产品用于现实生产则最简的设计方案使用的材料最少,生产成本也就最低,设计才有现实意义。

6. 通过本次实验可知,一个问题可以有很多种解决方案。寻找问题的解决方法时需要我们不断思考,找到最佳的解决方案。

第二篇:数电实验报告 实验二 组合逻辑电路的设计

实验二 组合逻辑电路的设计

一、实验目的

1.掌握组合逻辑电路的设计方法及功能测试方法。

2.熟悉组合电路的特点。

二、实验仪器及材料

a) TDS-4数电实验箱、双踪示波器、数字万用表。

b) 参考元件:74LS86、74LS00。

三、预习要求及思考题

1.预习要求:

1)所用中规模集成组件的功能、外部引线排列及使用方法。

2) 组合逻辑电路的功能特点和结构特点.

3) 中规模集成组件一般分析及设计方法.

4)用multisim软件对实验进行仿真并分析实验是否成功。

2.思考题

在进行组合逻辑电路设计时,什么是最佳设计方案?

四、实验原理

1.本实验所用到的集成电路的引脚功能图见附录

2.用集成电路进行组合逻辑电路设计的一般步骤是:

1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表;

2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式;

3)画出逻辑图;

4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。

五、实验内容

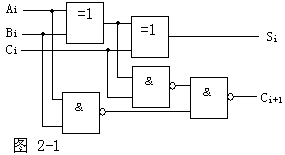

1.用四2输入异或门(74LS86)和四2输入与非门(74LS00)设计一个一位全加器。

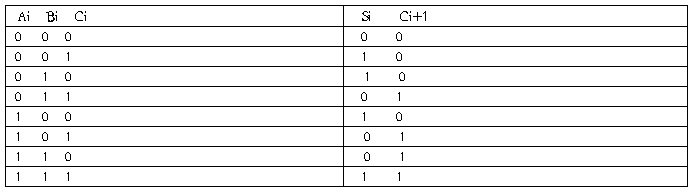

1)列出真值表,如下表2-1。其中Ai、Bi、Ci分别为一个加数、另一个加数、低位向本位的进位;Si、Ci+1分别为本位和、本位向高位的进位。

表 2-1 全加器真值表

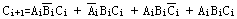

2)由表2-1全加器真值表写出函数表达式。

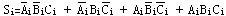

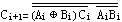

3)将上面两逻辑表达式转换为能用四2输入异或门(74LS86)和四2输入与非门(74LS00)实现的表达式。

4)画出逻辑电路图如图2-1,并在图中标明芯片引脚号。按图选择需要的集成块及门电路连线,将Ai、Bi、Ci接逻辑开关,输出Si、Ci+1接发光二极管。改变输入信号的状态验证真值表。

2.在一个射击游戏中,每人可打三枪,一枪打鸟(A),一枪打鸡(B),一枪打兔子(C)。规则是:打中两枪并且其中有一枪必须是打中鸟者得奖(Z)。试用与非门设计判断得奖的电路。(请按照设计步骤独立完成之)

五、实验报告要求:

1.画出实验电路连线示意图,整理实验数据,分析实验结果与理论值是否相等。

2.设计判断得奖电路时需写出真值表及得到相应输出表达式以及逻辑电路图。

3.总结中规模集成电路的使用方法及功能。