电子信息工程学系实验报告

课程名称:EDA技术与实验

课程名称:EDA技术与实验

实验项目名称:实验二 三八译码器设计 实验时间:2011.9.5

实验项目名称:实验二 三八译码器设计 实验时间:2011.9.5

班级: 姓名: 学号:

实验目的:

1.熟悉ALTERA公司EDA设计工具软件max+plusⅡ。

2.掌握max+plusⅡ文本设计及其仿真。

实验环境:

max+plusⅡ

实验内容及过程:

1.三八译码器的工作原理

由三个输入端A,B,C和八个输出端Y0,Y1,Y2,Y3,Y4,Y5 ,Y6,Y7组成,输入输出用二进制表示。

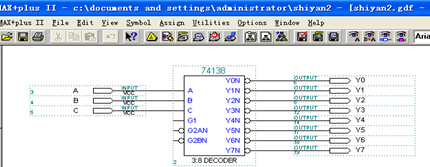

2.原理图设计

2.文本设计

打开File点击New选择文本文件,点击OK.进行编程,再保存

3.建立工程。运行File,Project,Set Project to Current File,讲工程设置到当前文件。

4.编译工程。在 MAX+PLUS II 菜单内选择Compiler 项,选择 Start即可开始编译。

5.选择菜单“File”→“New”,在出现的“New”对话框中选择“Waveform Editor File”,按“OK”后将出现波形编辑器子窗口。选择菜单“Node ” →“Enter Nodes from SNF”,出现选择信号结点对话框。按右上侧的“List”按钮,左边的列表框将立即列出所有可以选择的信号结点,然后按中间的“=>”按钮,将左边列表框的结点全部选中到右边的列表框。按“OK”按钮,选中的信号将出现在波形编辑器中

7将波形图保存为.scf

8.选择主菜单“MAX+plus II”→“Simulator”,按下“Simulator”,出现仿真参数设置与仿真启动窗,这时按下该窗口中的“Start”按钮,即刻进行仿真运算。再点击右边的OPEN SCF,就会出现仿真结果。

实验结果及分析:

实验心得:

通过实验学会了三八译码器的程序设计和原理图设计,对三八译码器有了更深的了解。

第二篇:eda第二次实验 38译码器

实验二 组合逻辑电路的VHDL模型实验

一、实验目的

1、 掌握组合逻辑和时序逻辑电路的设计方法。

2、 掌握组合逻辑电路的静态测试方法。加深FPGA设计的过程,并比较原理图输入和文本输入的优劣。

3、 了解通用同步计数器,异步计数器的使用方法。

4、 理解积分分频器的原理。

二、硬件要求

拨位开关、FPGA主芯片EP1K30QC208、LED显示模块

三、实验原理

译码器是输入数码和输出数码之间的对应关系,也就是说,“输入码和输出码之间的对应表”这应该算是设计译码器的必须条件。

译码器常用来做码和码之间的转换器,也常被用于地址总线或用作电路的控制线。

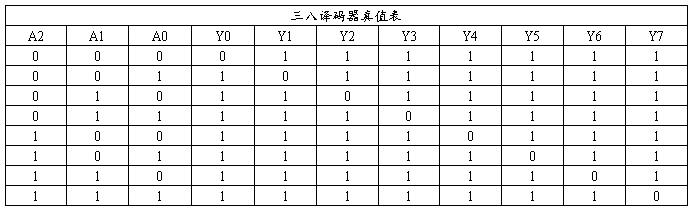

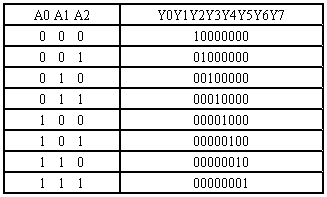

例如下面为常见的3×8译码器的真值表:

实验中可根据需要,为3×8译码器加入使能控制脚。

一般的分频器可获得的分频频率种类分布不均匀,积分分频,能比较好的解决这个问题。

1、分频结果=来源频率×N/(2?-1);

2、频率波形不均匀。

四、实验内容及步骤

本实验内容是完成38译码器和5/8分频器的设计,然后将3×8译码器的结果在实验箱上实现,5/8分频器则能正确仿真、显示,实验步骤如下:

1、编写3×8译码器的VHDL代码。

2、用MaxPlusII对其进行编译仿真。

3、在仿真确定无误后,选择芯片ACEX1K EP1K30QC208。

4、给芯片进行管脚绑定,在此进行编译。

5、根据自己绑定的管脚,在实验箱上对键盘接口、显示接口和FPGA之间进行正确连线。

6、给目标板下载代码,在开关输入键值,观看实验结果。

7、编写5/8分频器的VHDL代码。

8、用MaxPlusII对其进行编译仿真。

9、使用WaveForm进行波形仿真。

五、程序代码

1. 38译码器

library ieee;

use ieee.std_logic_1164.all;

entity a3toy8 is

port (en:in std_logic;

a:in std_logic_vector(2 downto 0);

b:in std_logic_vector(2 downto 0);

y:out std_logic_vector(7 downto 0);

YM: out std_logic_vector(7 downto 0));

end entity a3toy8;

architecture a3y8 of a3toy8 is

signal t:std_logic_vector(3 downto 0);

signal v:std_logic_vector(3 downto 0);

begin

t <= en & a(2 downto 0);

process(t(3 downto 0))

begin

case t(3 downto 0) is

when "1000" => Y(7 downto 0) <= "00000001";

when "1001" => Y(7 downto 0) <= "00000010";

when "1010" => Y(7 downto 0) <= "00000100";

when "1011" => Y(7 downto 0) <= "00001000";

when "1100" => Y(7 downto 0) <= "00010000";

when "1101" => Y(7 downto 0) <= "00100000";

when "1110" => Y(7 downto 0) <= "01000000";

when "1111" => Y(7 downto 0) <= "10000000";

when others => Y(7 downto 0) <= "00000000";

end case;

end process;

v <= t;

process(v(3 downto 0))

begin

case v(3 downto 0) is

WHEN "1000" => YM(7 downto 0) <= "01100000";

WHEN "1001" => YM(7 downto 0) <= "11011010";

WHEN "1010" => YM(7 downto 0) <= "11110010";

WHEN "1011" => YM(7 downto 0) <= "01100110";

WHEN "1100" => YM(7 downto 0) <= "10110110";

WHEN "1101" => YM(7 downto 0) <= "10111110";

WHEN "1110" => YM(7 downto 0) <= "11100000";

WHEN "1111" => YM(7 downto 0) <= "11111110";

when others => YM(7 downto 0) <= "00000000";

end case;

end process;

end architecture a3y8;

本代码是通过控制拨动开关来控制led灯,并且在数码管上显示发亮的是第几盏led。

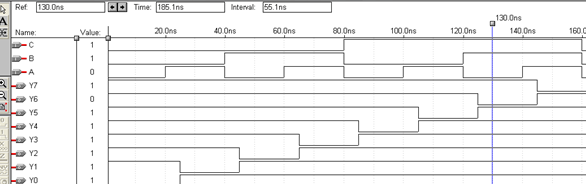

时序图仿真:

2.5/8分频器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ch5_8 is

port (clk:in std_logic;

c_out:out std_logic);

end entity ch5_8;

architecture one of ch5_8 is

signal dly:std_logic;

signal qn:std_logic_vector(3 downto 0);

begin

process(clk)

begin

if clk'event and clk='1' then

dly <= qn(3);

qn<= qn + 5;

end if;

end process;

c_out<= (qn(3) xor dly) and (not clk);

end architecture one;

时序图:

六、思考:如果要设计7/8分频器,需要如果进行改动?总结设计方法。

实现7/8分频只需把语句“qn<=qn+5”改成“qn<=qn+7”即可