目录

1. 前言... 3

2. 设计要求... 4

3.整体设计... 4

4. 设计原理... 4

5. 设计程序... 4

5.1顶层文件... 4

5.2 8位是进制计数器... 5

5.3 10进制计数器... 6

5.4 测频控制电路... 7

5.5 32位锁存器及其控制器... 8

6. 引脚锁定... 9

7. 综合结果... 9

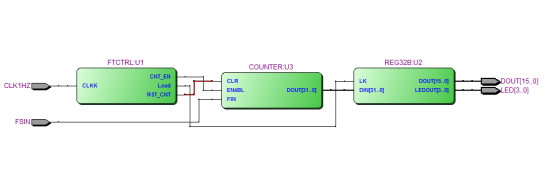

7.1 RTL电路... 9

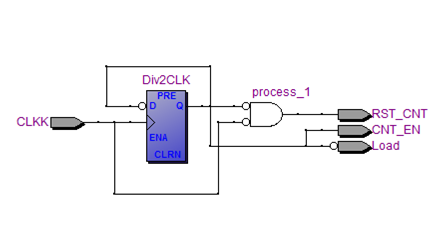

7.2 测频控制电路... 10

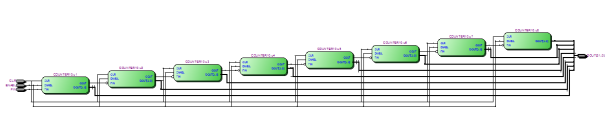

7.3 8位十进制计数器... 10

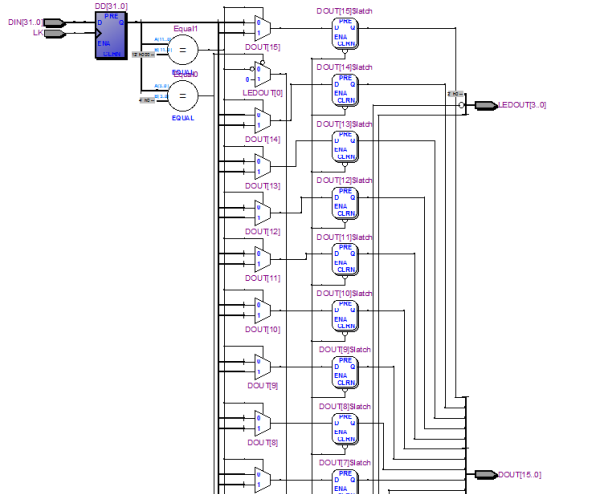

7.3 32位锁存器... 10

8. 实验结果... 11

7.实验总结... 11

参考文献... 13

自适应数字频率计数器设计

1. 前言

传统的数字频率计一般是由分离元件搭接而成,用到的器件较多,连线比较复杂,而且会产生比较大的延时,造成测量误差大、可靠性差。后来随着单片机的大规模的应用, 出现了不少用单片机控制的频率测量系统。相对于以前用分离元件搭接起来的频率测量系统, 单片机控制的频率测量系统在频率测量范围、频率测量精度和频率测量速度上都有了很大的提高。但由于单片机工作频率的限制、单片机内部计数器位数的限制等因素, 由单片机控制的频率测量系统无法在频率测量范围、频率测量精度和频率测量速度上取得重大突破。若再增加别的器件, 以弥补单片机的不足, 不仅会大大增加系统的复杂性, 而且不利于系统的集成化。以E D A 工具作为开发平台,运用V H D L 语言,将使整个系统大大简化,从而提高整体的性能和可靠性。 本课题采用的是等精度数字频率计,在一片FPGA开发板里实现了数字频率计的绝大部分功能, 它的集成度远远超过了以往的数字频率计。又由于数字频率计最初的实现形式是用硬件描述语言写成的程序, 具有通用性和可重用性。 所以在外在的条件(如基准频率的提高, 基准频率精度的提高)的允许下,只需对源程序作很小的改动, 就可以使数字频率计的精度提高几个数量级。同时对于频率精度要求不高的场合, 可以修改源程序, 使之可以用较小的器件实现, 从而降低系统的整体造价。

2. 设计要求

设计一个频率计,频率测量范围为1-9999KHZ,量程分别为10 、100、 1M三档,要求如下:

a. 当读数大于999时,频率计处于超量程状态,下一次测量时,量程自动增大1档

b. 当读数小于099时,频率计处于欠量程状态,下一次测量时,量程自动减小1档

c. 当超过频率范围时,显示器自动溢出

3.整体设计

当被测频率进入时候,档位1、2能自动换挡实现功能,在档位1中,有一个LED灯亮(表示Hz);档位2中有2个LED灯亮(表示kHz);当计数频率超出9999kHz的时候,显示“E”而且LED灯全部熄灭,表示溢出功能。在程序代码中,必须要清晰表示出计数的运行状况。

档位1:当被测频率为0—9999Hz时候,直接显示f x的值(单位为Hz);

档位2:当被测频率为10k—9999kHz时候,显示10-9999(单位kHz);

4. 设计原理

根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1 秒的输入信号脉冲计数允许的信号;1 秒计数结束后,计数值被锁入锁存器,计数器清0,为下一测频计数周期作好准备。测频控制信号可以由一个独立的发生器来产生。

5. 设计程序

5.1顶层文件

LIBRARY IEEE; --频率计顶层文件

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY FREQTEST IS

PORT ( CLK1HZ : IN STD_LOGIC;

FSIN : IN STD_LOGIC;

DOUT : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

LED : OUT STD_LOGIC_VECTOR(1 DOWNTO 0) );

END FREQTEST;

ARCHITECTURE struc OF FREQTEST IS

COMPONENT FTCTRL

PORT (CLKK : IN STD_LOGIC; -- 1Hz

CNT_EN : OUT STD_LOGIC; -- 计数器时钟使能

RST_CNT : OUT STD_LOGIC; -- 计数器清零

Load : OUT STD_LOGIC ); -- 输出锁存信号

END COMPONENT;

COMPONENT COUNTER

PORT (FIN : IN STD_LOGIC; -- 时钟信号

CLR : IN STD_LOGIC; -- 清零信号

ENABL : IN STD_LOGIC; -- 计数使能信号

DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); -- 计数结果

END COMPONENT;

COMPONENT REG32B

PORT ( LK : IN STD_LOGIC;

DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

LEDOUT : OUT STD_LOGIC_VECTOR(1 DOWNTO 0));

END COMPONENT;

SIGNAL TSTEN1 : STD_LOGIC;

SIGNAL CLR_CNT1 : STD_LOGIC;

SIGNAL Load1 : STD_LOGIC;

SIGNAL DTO1 : STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL CARRY_OUT1 : STD_LOGIC_VECTOR(6 DOWNTO 0);

BEGIN

U1 : FTCTRL PORT MAP(CLKK =>CLK1HZ,CNT_EN=>TSTEN1,

RST_CNT =>CLR_CNT1,Load =>Load1);

U2 : REG32B PORT MAP( LK => Load1, DIN=>DTO1, DOUT => DOUT,LEDOUT=>LED);

U3 : COUNTER PORT MAP( FIN => FSIN, CLR => CLR_CNT1,

ENABL => TSTEN1, DOUT=>DTO1 );

END struc;

5.2 8位是进制计数器

LIBRARY IEEE;-- 8位十进制计数器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTER IS

PORT (FIN : IN STD_LOGIC; -- 时钟信号

CLR : IN STD_LOGIC; -- 清零信号

ENABL : IN STD_LOGIC; -- 计数使能信号

DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0)); -- 计数结果

END COUNTER;

ARCHITECTURE behav OF COUNTER IS

COMPONENT COUNTER10 IS

PORT (FIN : IN STD_LOGIC; -- 时钟信号

CLR : IN STD_LOGIC; -- 清零信号

ENABL : IN STD_LOGIC; -- 计数使能信号

DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); -- 计数结果

COUT : OUT STD_LOGIC);

END COMPONENT ;

SIGNAL CLK1,CLK2,CLK3,CLK4,CLK5,CLK6,CLK7: STD_LOGIC;

BEGIN

u1 : COUNTER10 PORT MAP(FIN=>FIN,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(3 DOWNTO 0),COUT=>CLK1);

u2 : COUNTER10 PORT MAP(FIN=>CLK1,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(7 DOWNTO 4),COUT=>CLK2);

u3 : COUNTER10 PORT MAP(FIN=>CLK2,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(11 DOWNTO 8),COUT=>CLK3);

u4 : COUNTER10 PORT MAP(FIN=>CLK3,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(15 DOWNTO 12),COUT=>CLK4);

u5 : COUNTER10 PORT MAP(FIN=>CLK4,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(19 DOWNTO 16),COUT=>CLK5);

u6 : COUNTER10 PORT MAP(FIN=>CLK5,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(23 DOWNTO 20),COUT=>CLK6);

u7 : COUNTER10 PORT MAP(FIN=>CLK6,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(27 DOWNTO 24),COUT=>CLK7);

u8 : COUNTER10 PORT MAP(FIN=>CLK7,CLR=>CLR,ENABL=>ENABL,DOUT=>DOUT(31 DOWNTO 28));

END ARCHITECTURE behav;

5.3 10进制计数器

LIBRARY IEEE; --10位计数器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY COUNTER10 IS

PORT (FIN : IN STD_LOGIC; -- 时钟信号

CLR : IN STD_LOGIC; -- 清零信号

ENABL : IN STD_LOGIC; -- 计数使能信号

DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); -- 计数结果

COUT : OUT STD_LOGIC);

END COUNTER10;

ARCHITECTURE behav OF COUNTER10 IS

SIGNAL CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(FIN, CLR, ENABL)

BEGIN

IF CLR = '1' THEN CQI <= (OTHERS=>'0'); -- 清零

ELSIF FIN'EVENT AND FIN = '1' THEN

IF ENABL = '1' THEN

IF CQI<9 THEN CQI <= CQI + 1;

ELSE CQI <= (OTHERS=>'0');

END IF;

END IF;

END IF;

IF CQI="1001" THEN COUT<='1';

ELSE COUT<='0'; END IF;

END PROCESS;

DOUT <= CQI;

END behav;

5.4 测频控制电路

LIBRARY IEEE; --测频控制电路

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY FTCTRL IS

PORT (CLKK : IN STD_LOGIC; -- 1Hz

CNT_EN : OUT STD_LOGIC; -- 计数器时钟使能

RST_CNT : OUT STD_LOGIC; -- 计数器清零

Load : OUT STD_LOGIC ); -- 输出锁存信号

END FTCTRL;

ARCHITECTURE behav OF FTCTRL IS

SIGNAL Div2CLK : STD_LOGIC;

BEGIN

PROCESS( CLKK )

BEGIN

IF CLKK'EVENT AND CLKK = '1' THEN -- 1Hz时钟2分频

Div2CLK <= NOT Div2CLK;

END IF;

END PROCESS;

PROCESS (CLKK, Div2CLK)

BEGIN

IF CLKK='0' AND Div2CLK='0' THEN RST_CNT<='1';-- 产生计数器清零信号

ELSE RST_CNT <= '0'; END IF;

END PROCESS;

Load <= NOT Div2CLK; CNT_EN <= Div2CLK;

END behav;

5.5 32位锁存器及其控制器

LIBRARY IEEE; --32位锁存器及控制器

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY REG32B IS

PORT ( LK : IN STD_LOGIC;

DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

LEDOUT : OUT STD_LOGIC_VECTOR(1 DOWNTO 0));

END REG32B;

ARCHITECTURE behav OF REG32B IS

SIGNAL DD : STD_LOGIC_VECTOR(31 DOWNTO 0);

BEGIN

PROCESS(LK, DIN)

BEGIN

IF LK'EVENT AND LK = '1' THEN DD<=DIN; END IF;

if DD(31 DOWNTO 28)="0000" then

IF DD(27 DOWNTO 16)="000000000000" THEN DOUT<=DD(15 DOWNTO 0);LEDOUT<="01";

ELSIF DD (27 DOWNTO 16)/="000000000000" THEN DOUT<=DD(27 DOWNTO 12);LEDOUT<="11";

end if;

else DOUT(15 DOWNTO 0)<="0000000000001110";LEDOUT<="00";

END IF;

END PROCESS;

END behav;

6. 引脚锁定

![7DXCC29F8@_W]G4O3{X%$$A](https://upload2.fanwen118.com/wk001/4035020/4035020_img_001.jpg)

7. 综合结果

7.1 RTL电路

7.2 测频控制电路

7.3 8位十进制计数器

7.3 32位锁存器

8. 实验结果

当计数频率为4Hz(范围在0-9999Hz)的时候,此时LED灯有一个亮,计数为:0004;当计数频率为500KHz(范围在10K-9999KHz)的时候,此时设定两个LED灯都亮,计数为0500;当计数频率大于9999KHz的时候,设定此时两个LED灯都处于熄灭状态,而计数则输出一个‘E’值,表示范围超出计数范围。

7.实验总结

经系统测试表明,本图频率计的各项功能正常,能实现对频率的0~9999kHz频率范围的测量,并通过LED指示和数码管显示,操作简单,是理想频率计解决方案。

经过一个多星期的努力,本设计系统终于完成了。通过该课程设计,掌握了编译程序工作的基本过程及其各阶段的基本任务,熟悉了VHDL程序开发的总流程框图,了解了编译程序的生成过程及其相关的技术,对课本上的知识也有了更深的理解。老师常说,课本上的知识是机械的,要学会去运用,要举一反三。现在终于深刻的了解了这句话。经过这次的课程设计,发现书本上很深奥的知识变的更为简单,同样,对实验原理也了有更深的理解。知道和理解了该理论在计算机中是怎样执行的, 对该理论在实践中的应用有深刻的理解 。通过该课程设计,把死板的课本知识变得生动有趣,激发了学习的积极性。能够把课堂上学的知识通过自己设计的程序表示出来,加深了对理论知识的理解。

课程设计中的电路和程序比较复杂,因此调试的过程更是考验我们耐性和细心。除了课堂外,课程设计是最能学到东西的,最考验人的。在做课程设计的这段时间,时刻都感到自己学的知识有多么的贫瘠。经过这次课程设计,让我对VHDL语言和FPGA有了更深的认识,操作能力有了一定的提高。明白了,要想是写出的代码能运行,需要耐心细心,毅力以及充沛的体力。只有经过多次编辑,多次编译,再多次运行,才能编写出更好的程序,有时候需要多次的更正才能达到所要的运行结果。

参考文献

[1] 潘松、黄继业, EDA技术应用教程 VHDL篇[J] . 北京:高等教育出版社.2010

[2] 徐成刘彦李仁发,一种全同步数字频率测量方法的研究[J] . 北京:高等教育出版社.2004

[3] 李云鹏王思明,基于FPGA 的等精度频率计设计[J] . 北京:高等教育出版社.2007