--VF课程设计报告

--VF课程设计报告

设计内容 : 计算器程序设计

学院信息 : 管 理 学 院

班 级 : 会计1204班

制作人员 : 史 凡 史 明 坤

学 号 :1220034149

指导教师: 周作涛

目录

一、 程序功能设计界面................................ 2

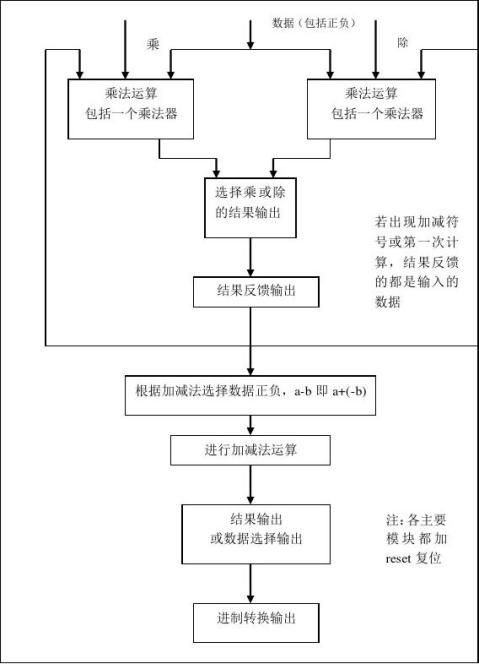

二、程序流程图及其说明............................... 3

1 程序流程图....................................... 3

2 流程图说明....................................... 4

三、程序调试......................................... 4

1.初始界面......................................... 4

2.加法运算实现界面................................. 4

3.除法运算实现..................................... 5

4.减法运算......................................... 5

5. 乘法运算实现.................................... 6

6.清屏后的界面..................................... 6

四、心得体会......................................... 7

五、参考文献......................................... 7

六、附录(代码)....................................... 8

一、程序基本概况

1 程序界面

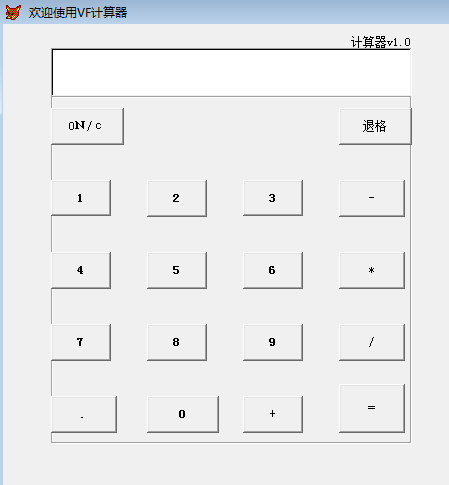

该课程设计的任务是做一个简易计算器,可以实现加减乘除四则运算。我们要解决的问题有:以什么方式输入数字、判断是进行什么运算、运算过程中的进位和借位问题以及如何实现清屏等问题。

首先我们要解决的是输入问题,这里我们用vf的自定义的按钮来进行个人输入;然后我们要进行的是判断是进行何种运算,到底是“+、-、*、/”中的哪一种。当点击ON/c时,则清屏。点击退格时则消减一位数字。

具体界面如下图:

2程序功能介绍

本次设计的为简易计算器程序,可以进行简单的四则运算,并对计算的结果及过程能及时并准确的显示。

二、初步设计构想

本次课程设计以设计简易计算器为主,功能较为简单,内容相对较少,但其界面必须清晰明了,不能过于繁琐,应由一个text文本框以及相关按钮组成,按钮方面应人性化对按钮进行全面分析设计,使使用者能更好更简洁的使用相关操作。

三、程序设计步骤

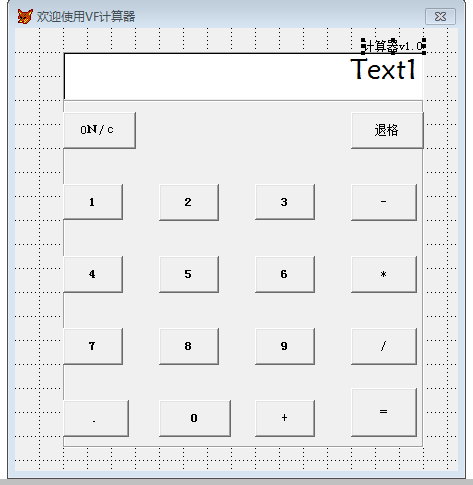

1.初始界面

首先打开Microsoft Visual Foxpro 程序,在程序中新建一个表单,完成后在表单上添加一个text文本框一个标签框以及一个命令按钮组和两个按钮并将命令按钮组的Button Count 属性值改为16,text1的Alignment属性改为1-右,command1~16的FontBlod改为真并修改它们各自的Caption数值,将command1~10 Caption分别改为1,2,3,4,5,6,7,8,9,0;command11~16则改为“.”,“=”,“+”,“-”,“*”,“/”(其中“=”为全拼时输入),按钮一及按钮二Caption改为“ON/c”和“退格”

完成后,进入程序运行初始界面,如图:

2数字输入的实现

通过上一步骤的操作,我们基本完成了对计算器界面的相关制作,但在运行时我们不难发现这些按钮并未有实质性作用,很显然我们没有对其写入代码,所以此步骤我们先来进行对数字按键代码的编写,首先我们需要明白数字是在text1中显示出来的,虽然我们知道了text1可以显示相关数字但在vf中其数据的类型比较多样,而text1的数据类型也必须为字符型数据类型,如果我们按键输入的字符为数值型就很难被显示出来,但如果不能输入数值型我们又该怎么去输入数字的更高位数呢,其实很简单我们只需要将0~9按钮输入的字符相互连接就可以了。

即对其相应代码的编写如下:

按键0:thisform.text1.value = thisform.text1.value + ”0”

按键1:thisform.text1.value = thisform.text1.value + ”1”

按键2:thisform.text1.value = thisform.text1.value + ”2”

按键3:thisform.text1.value = thisform.text1.value + ”3”

按键4:thisform.text1.value = thisform.text1.value + ”4”

按键5:thisform.text1.value = thisform.text1.value + ”5”

按键6:thisform.text1.value = thisform.text1.value + ”6”

按键7:thisform.text1.value = thisform.text1.value + ”7”

按键8:thisform.text1.value = thisform.text1.value + ”8”

按键9:thisform.text1.value = thisform.text1.value + ”9”

到此,我们再次运行程序就可以自由的输入我们想输入的数字了。

3相关运算的编写

上一步我们进行了对数字输入的相关编写,但数字的输入并不是我们设计的最终目的,我们还需要对数字进行更深一步的计算,这样才能到达我们设计的目的。

首先我们要明确我们只有加减乘除四则运算,我们需要对这四则运算进行更深一步的分析及阐述。

其次我们要明白我们这里的四则运算是针对数值来说的,而我们通过按钮输入的数字却是字符型的,字符型的加减只是字符之间的串联我们需要对字符进行深一步的转换才可以得出我们想要的结果。

在

三、心得体会

经调试,基本上任务要求设计的所有功能都实现,调试出的计算结果均正确。一周的课程设计结束了,给我的总体感觉就是忙碌但充实,而且真正学到了东西。

以前做课程课计的时候总是前几天时间玩,后面几天才开始做,不过这次却是一直都在做这个课程设计,因为在网上我根本搜不到别人写的简易计算机的资料,所以从构思到设计流程图到编写源程序都是我一个人独立完成的,虽然这个过程比较痛苦,但是我真正的去体验了,当我编写的程序一遍一遍地报错,出的结果一次次和正确结果有出入的时候我真的好想放弃,但是我选择了坚持,通过调试程序,一步步地看寄存器和数据区的变化,最终发现了错误并改正了错误,当运行的结果全都正确的时候我真的好激动,好有成就感,因为这是我第一次自己独立地编写的长达两百多条的程序,虽然结构看上去有点乱,语句不够精练,但是不管怎样,我终于能够实现要求的功能了。

另外,这次无论是设计个这程序还是写课程设计报告都让我学到了好多东西,有对课本知识更加深入的了解和掌握,也有对于流程图的设计以及绘制还有word的一些用法和排版等,都让我受益匪浅,

总之,非常感谢学校和老师给我们安排了这次课程设计,不仅让我掌握了更多的知识,还让我领会到要把一件事情做好并真正有所收获还得靠自己独立地去完成并坚持不懈!希望在以后的学习中还能多搞几次这种课程设计。

五、参考文献

[1] 周佩玲、彭虎、傅忠谦.微机原理与接口技术(基于16位机). 北京:电子工业出版社.,2005

[2] 马春燕.微机原理与接口技术(基于32位机)实验与学习辅导. 北京:电子工业出版社.,2007

[3] 何小海、严华. 微机原理与接口技术.北京:科学出版社,2006

[4] 钱晓捷. 新版汇编语言程序设计. 北京:电子工业出版社,2007

第二篇:简易计算器报告

数字系统设计实践 实验报告(四)

实验名称 班 级: 通信113

学生姓名: 胡挺

学 号: 116040222

完成日期: 2013-06-17

1

目 录

绪论

0.1 引言摘要3 0.2 关键词3

一、实验任务及要求 3

1.1 设计任务及要求3

1.2 计算器的系统组成框图4

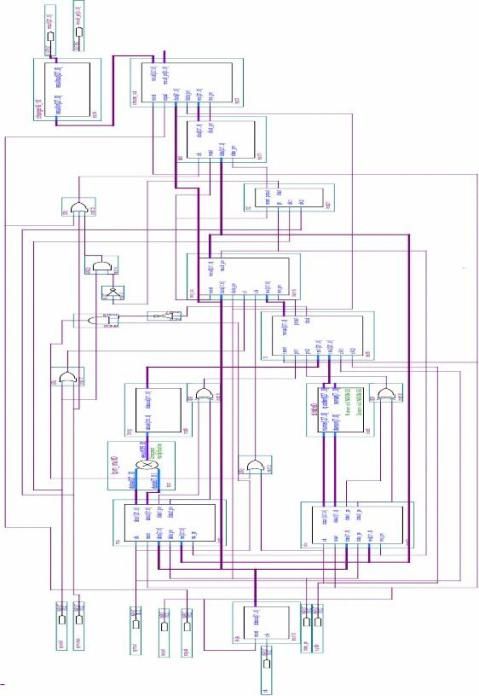

二、 系统设计2.1 原理图输入顶层设计4

2.2 系统总框架5

2.3 系统各模块6

2.4 系统各模块VHDL语言设计三、 系统测试 15

3.1 部分数据及操作结果15

2

绪论

0.1 引言摘要

摘要:本文介绍了一个简单计算器的设计,该设计采用了现场可编程逻辑器件FPGA设计,并基于硬件描述语言VHDL在Altera公司的Quartus Ⅱ软件上实现仿真。系统由计算部分、存储部分、显示部分和输入部分四个部分组成,计算部分为加法器、减法器、乘法器和除法器,存储部分需要3个存储器来实现:内部累加器(acc)、输入寄存器(reg)以及结果暂存器(ans)。显示部分由七段译码管组成,显示输入数字,加减乘除四个运算符按键,一个符号按键,一个等号按键和一个清零按键,一个计数按键组成的。通过按键可以完成四位数之内的加、减、乘、除四种功能运算,其结构简单,易于实现。

引言:计算器已经成为人们日常生活中不可缺少的一种计算工具,为我们的生活提供了很大的方便。而随着计算机的普及,越来越多人在使用计算机,越来越多的工作离不开计算机,可以说计算机已经成为现代社会中不可或缺的工具,而电子计算器功能也以软件的形式进入计算机的软件世界,这不仅给人们带来了更大的便利,更为人们引入了更快的计算速度和更强大的运算功能。

0.2关键词

FPGA,VHDL,计算器

一、实验任务及要求

1.1 设计任务及要求

1.基本内容:设计一个简易计算器

2.基本要求:

①实现最大输入两位十进制数字的四则运算(加减乘除)

②能够实现多次连算(无优先级,从左到右计算结果)

如 12+34×56-78÷90+9=36.75

③最大长度以数码管最大个数为限,溢出报警

④有正负数区分;

3

⑤除法不能除尽时小数保留2位有效数字

3.扩展要求:

能够区分运算优先级(先乘除,后加减) 如12+34×56-78÷90+9=1924.13

1.2 计算器的系统组成框图

二、系统设计

2.1 原理图输入顶层设计

4

5

2.2系统总体框架

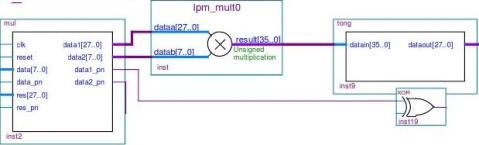

2.3 系统各模块 1.乘法模块

6

模块说明:

当乘法符号的上升沿的时候读入反馈的结果(包括数据及正负号)并输出到data1、data1_pn;

当乘法符号的下降沿的时候读入数据(包括数据及正负号)并输出到data2、data2_pn。并进行计算,结果的数据由乘法器计算得到;结果的正负号即为两个相乘数据的正负号取异或。

数据为保留两位小数,输出的当成被乘数的数乘上100。

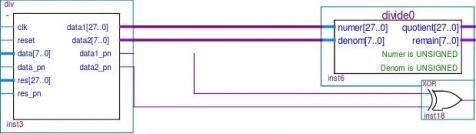

2.除法模块:

模块说明:

当除法符号的上升沿的时候读入反馈的结果(包括数据及正负号)并输出到data1、data1_pn;

当除法符号的下降沿的时候读入数据(包括数据及正负号)并输出到data2、data2_pn。并进行计算,结果的数据由除法器计算得到;结果的正负号即为两个相除数据的正负号取异或。

数据为保留两位小数,输出的当成被除数的数乘上100。

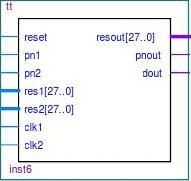

3.乘或除数据选择输出模块:

7

模块说明:

乘或除的数据及正负在各自符号的下降沿时输出,在输出时确定输出的是乘的结果还是除的结果。即预期在乘符号的下降沿时输出乘的结果;在除符号的下降沿时输出除的结果。

又由于两个时钟信号不能控制同一个变量,所以把clk1当成是清零信号,clk2当成时钟信号,当clk2的下降沿的时候输出数据2(即除的结果),clk2为1时,输出数据1(即除的结果)。又为了防止clk2为1与其后面要用到的上升沿冲突,故添加dout。

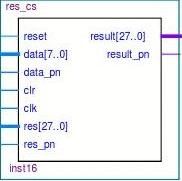

4.结果反馈及输出模块:

模块说明:

当第一次进行运算或出现过加减再进行乘除的第一次运算时读取输入的数据值,否则读取前一级的结果值。

其中clr为恢复信号(加or 减),当其为1时,恢复到第一次运算的模式。clk本为乘或除,又为了避开与上一级的清零错位,故其变为(乘or(除and not dout))

5.加减选择模块:

模块说明:

减法是加法的逆运算,A-B等同于A+(-B),即减法运算只需在进行加法运算前把数据的正负取反,所以当减法的下降沿时输出的正负为输入的取反,加法的下降沿时输出的正负为输入的,实现方法与乘除选择模块一致。

8

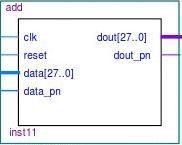

6.加减运算模块:

模块说明:

由于上一级已考虑加减情况,此模块只需实现加法运算。A+B有四种情况:

1、A>0,B>0 输出数据A+B,正负号为正

2、A>0,B<0 |A|>|B| 输出数据|A|-|B| 正负号为正

|A|<|B| 输出数据|B|-|A| 正负号为负

3、A<0,B>0 |A|>|B| 输出数据|A|-|B| 正负号为负

|A|<|B| 输出数据|B|-|A| 正负号为正

4、A<0,B<0 输出数据A+B,正负号为负

其中clk为加or减,上升沿时读新数据并计算。

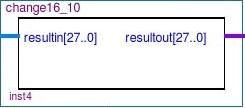

7.进制转换模块:

模块说明:

28位二进制数(根据7个数码管为限,最大输出为十进制的9999999,后两位为小数位)以十进制的方式显示到数码管上,采用各位求余分别显示的方法。

其中除数分别为十进制的1000000、100000、10000、1000、100、10,需要输出的是每次相除后的商及最后一个余数。

9

2.4 系统各模块VHDL语言设计

乘法模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity mul is

port( clk : in std_logic;

reset: in std_logic;

data : in std_logic_vector(7 downto 0);

data_pn : in std_logic;

res : in std_logic_vector(27 downto 0);

res_pn: in std_logic;

data1: out std_logic_vector(27 downto 0);

data2: out std_logic_vector(7 downto 0);

data1_pn:out std_logic;

data2_pn:out std_logic

);

end entity mul;

architecture behave of mul is

signal temp1:std_logic;

signal temp2:std_logic;

begin

process(reset,clk)

begin

if(reset='0')then

if(clk'event and clk='1')then

data1<=res; data1_pn<=res_pn;

end if;

if(clk'event and clk='0')then

data2<=data; data2_pn<=data_pn;

end if;

else data1<="0000000000000000000000000000";data2<="00000000"; end if;

end process;

end behave;

除法模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity div is

10

port( clk : in std_logic;

reset: in std_logic;

data : in std_logic_vector(7 downto 0);

data_pn : in std_logic;

res : in std_logic_vector(27 downto 0);

res_pn: in std_logic;

data1: out std_logic_vector(27 downto 0);

data2: out std_logic_vector(7 downto 0);

data1_pn:out std_logic;

data2_pn:out std_logic

);

end entity div;

architecture behave of div is

signal temp1:std_logic;

signal temp2:std_logic;

begin

process(reset,clk)

begin

if(reset='0')then

if(clk'event and clk='1')then

data1<=res; data1_pn<=res_pn;

end if;

if(clk'event and clk='0')then

data2<=data; data2_pn<=data_pn;

end if;

else data1<="0000000000000000000000000000";data2<="00000000"; end if;

end process;

end behave;

乘或除数据选择输出模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity tt is

port(

reset:in std_logic;

pn1:in std_logic;

pn2:in std_logic;

res1:in std_logic_vector(27 downto 0 );

res2:in std_logic_vector(27 downto 0 );

clk1: in std_logic;

clk2: in std_logic;

11

resout: out std_logic_vector(27 downto 0 ); pnout:out std_logic;

dout:out std_logic

);

end entity tt;

architecture behave of tt is

signal temp:std_logic;

begin

dout<=temp;

process(clk1,clk2)

begin

if(reset='0')then

if(clk1='1')then temp<='0';

elsif(clk2'event and clk2='0')then

temp<='1';

end if;

if(temp='1')then

resout<=res2;pnout<=pn2; else resout<=res1;pnout<=pn1; end if;

else temp<='0';

end if;

end process;

end behave;

结果反馈及输出模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity res_cs is

port( reset:in std_logic;

data: in std_logic_vector(7 downto 0); data_pn: in std_logic;

clr: in std_logic;

clk: in std_logic;

res: in std_logic_vector(27 downto 0); res_pn:in std_logic;

result: out std_logic_vector(27 downto 0); result_pn:out std_logic

);

end entity res_cs;

architecture behave of res_cs is

12

signal cn:std_logic_vector(3 downto 0);

begin

process(clk,clr)

begin

if(reset='0')then

if(clr='0')then

if(cn="0000")then

result<="0000000000000"&(data*"1100100");result_pn<=data_pn; else result<=res;result_pn<=res_pn;

end if;

if(clk'event and clk='1')then

cn<=cn+1;

end if;

else cn<="0000";

end if;

else cn<="0000";

end if;

end process;

end behave;

加减选择模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity tt2 is

port( reset:in std_logic;

pn:in std_logic;

clk1: in std_logic;

clk2: in std_logic;

pnout:out std_logic;

dout:out std_logic

);

end entity tt2;

architecture behave of tt2 is

signal temp:std_logic;

begin

dout<=temp;

process(clk1,clk2)

begin

if(reset='0')then

if(clk1='1')then temp<='0';

elsif(clk2'event and clk2='0')then

temp<='1';

13

end if;

if(temp='1')then

pnout<=not(pn);

else pnout<=pn;

end if;

else temp<='0';

end if;

end process;

end behave;

加减运算模块

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity add is

port(clk :in std_logic;

reset:in std_logic;

data:in std_logic_vector(27 downto 0);

data_pn:in std_logic;

dout :out std_logic_vector(27 downto 0);

dout_pn:out std_logic

);

end entity add;

architecture behave of add is

signal temp: std_logic_vector(27 downto 0):="0000000000000000000000000000"; signal temp_pn:std_logic:='0';

begin

dout<=temp;

dout_pn<=temp_pn;

process(clk,reset)

begin

if(reset='1')then temp<="0000000000000000000000000000";temp_pn<='0'; elsif( clk' event and clk='1')then

if(temp _pn='0')then

if(data _pn='0')then temp<=temp +data ; temp _pn<='0'; else

if(temp>data or temp=data)then

temp<=temp – data ; temp _ pn<='0';

else temp<=data – temp ; temp _pn<='1';

end if;

end if;

else

if(data _pn='1')then temp<=temp + data ; temp _pn<='1'; 14

else

if(temp<data or temp=data)then

temp<=data – temp ; temp _pn<='0';

else temp<=temp-data; temp _pn<='1'; end if;

end if;

end if;

end if;

end process;

end behave;

三、系统测试

3.1实验数据及操作结果

数据及验证:1、按正确方式按入式子3+2×3-5÷6×9+20 输出结果E 0 0 0 2 1 5 0 代表正21.50 和理论值21.5一致。

2、按正确方式按入式子12+50÷15×(-40) -51 输出结果F 0 0 1 7 2 3 3 代表正-172.33 和理论值-172.33一致。

3、按正确方式按入式子10×10×10×10×10 输出结果C 0 0 0 0 0 0 0 代表溢出 理论值为100000,溢出,符合要求。

15