淮海工学院

课程设计报告书

课程名称: 电子技术课程设计A

题 目: 数字钟的设计

系 (院): 电子工程学院

学 期: 20##-20##-2

专业班级: 电科121

姓 名: 刘园

学 号: 2012120929

电子技术课程设计报告

1 绪论

基于数字电子技术基础、模拟电子技术基础和电路原理有关知识,对多功能数字钟电路进行设计和制作。该数字钟可以实现准确显示24小时制时间,手动调节时间,随时启动、清零、置时间等功能,使用方便,制作简单。

本文针对多功能数字钟的各功能进行初步框架设计,并对多种方案进行了认真比较和验证,在此基础上,又进一步详细介绍了时间脉冲发生器、秒分计数器、时计数器、译码及驱动显示电路、校时电路的设计方法和要求。在总体电路图组装完成以后,针对设计好的电路,用Multisim软件进行了仿真与调试,逐步解决设计过程中出现的一系列问题。

在电路设计过程中,特意将选做部分即校时电路部分作为电路设计的主要内容。最后对应的数字钟设计方案对制作好的数字钟功能进行总体验证。

2 设计目的

2.1设计目的一

进一步熟悉对数字电子技术基础知识的理解,加深对数电知识应用重要性地认识,掌握数字钟的设计、组装和调试方法。

2.2设计目的二

掌握集成电路的使用方法,增强自己动手设计和动手操作的基本能力

2.3设计目的三

加强对作图软件,仿真软件的应用,熟悉操作,掌握好电气工程及其自动化专业学生应该掌握的基本技能。

3 设计思路

3.1总体设计思路

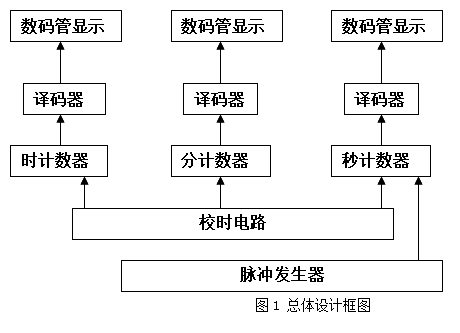

设计脉冲发生器电路产生脉冲;设计时、分、秒逻辑电路实现时间的正确显示功能;设计时、分、秒校时电路对数字钟显示时间进行基本校正。

3.2具体设计思路

根据已学知识,我们可以用由集成电路定时器555与RC组成的多谐振荡器作为时间标准信号源构成我们需要的脉冲发生器;以时基电路555定时器为核心,可以直接作为计数器输入脉冲信号使其进行计数 ,配合译码显示电路构成多功能数字钟的主要部分,控制部分则可以通过直接用开关与74LS160等一系列芯片的清零端相连接,直接控制清零,使系统具有随时启动、停止、清零、 计时;校时电路可以通过开关通断控制各芯片脉冲信号的通断,加以手动脉冲,实现准确校时。

4 设计过程

4.1 设计用到的电路

脉冲发生器:脉冲发生器是通过应用集成电路定时器555与RC组成的多谐振荡器,产生1Hz的方波脉冲信号。

时间计数器电路:时间计数电路由秒个位和秒十位计数器、分个位和分十位计数器及时个位和时十位计数器电路构成,其中秒计数器和分计数器为60进制计数器,根据设计要求,时计数器为24进制计数器。

译码驱动电路:译码驱动电路将计数器输出的8421BCD码转换为数码管需要的逻辑状态,并且为保证数码管正常工作提供足够的工作电流。

校时电路:用接有电源的线路开关对芯片直接进行脉冲控制,可实现单独调节时、分、秒各部分。总体设计框图如图1所示:

4.2方案设计与说明

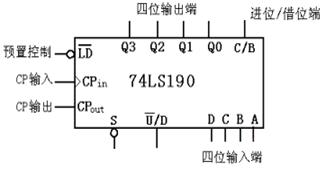

74LS160 为可预置的十进制同步计数器, RCO 进位输出端

ENP 计数控制端 QA-QD 输出端

ENT 计数控制端 CLK 时钟输入端

CLR 异步清零端(低电平有效)LOAD 同步并行置入端(低电平有效)74ls160管脚图如图2所示,功能表如图3所示:

图2 74LS160管脚图

图3 74LS160功能表

校时电路:首先截断正常的计数通路,然后再进行人工出触发计数或将频率较高的方波信号加到需要校正的计数单元的输入端,校正好后,再转入正常计时状态即可。根据要求,数字钟应具有分校正和时校正功能,因此,应截断分个位和时个位的直接计数通路,并采用正常计时信号与校正信号可以随时切换的电路接入其中。校时电路仿真如图4所示:

图4 校时电路

脉冲发生器:用555组成的脉冲产生电路,改变RC的配比,使得脉冲发生器产生的脉冲频率更接近设计要求水平R1=5kΩ,R2=5kΩ,C1=0.01μF ,C2=2μF则555所产生的脉冲的为:f=1.43/[(R1+2*R2)*10e3*2*10e6=0.963Hz,而设计要求为1Hz,因此其误差为1.7%。脉冲发生电路如图5所示:

![说明: C:\Users\张平\AppData\Roaming\Tencent\Users\1833865351\QQ\WinTemp\RichOle\%HNX]Y7G0E_[FMI}B`$XVIJ.jpg](https://upload2.fanwen118.com/wk001/3995519/3995519_img_005.jpg)

图5 脉冲发生电路

4.3分解电路的设计与说明

4.3.1脉冲发生器的设计

由集成电路定时器555与RC组成的多谐振荡器作为时间标准信号源。从输出端可以得到可以忽略误差接近1Hz的方波信号。

4.3.2秒、分计数器的设计

“秒”计数器电路与“分”计数器电路都是60进制,它由一级10进制计数器和一级6进制计数器连接构成。如图9所示由74ls160构成的60进制计数器。

74ls160是10进制计数,个位直接LOAD CLR ENP ENT 接高电平,CLK接时钟脉冲就可以实现十进制,

当十位“Q3Q2Q1Q0”由0000变为0101时,Q2Q0通过一与非门输出由0变为1,接LOAD,由于是同步置数,到个位产生脉冲上升沿,就会重置,所以不会输出0110,即实现6进制,Q2Q0通过一与门输出由0变为1,产生一上升沿,实现进位。

4.3.3 时计数器的设计

时计数器电路是24进制,十位的Q1与个位Q0Q1通过一个与非门可以实现时计数器重置;

4.3.4 译码及驱动显示电路的设计

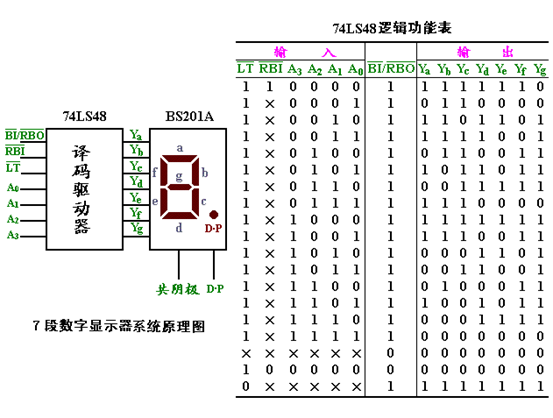

译码电路的功能是将“秒”、“分”、“时”计数器的输出代码进行翻译,变成相应的数字。本次使用74LS48,译码电路仿真如图6所示,功能表如图7所示:

图6 译码电路仿真

图7 74LS74电路图及功能表

4.3.5 校时电路的设计

数字种启动后,每当数字钟显示与实际时间不符进,需要根据标准时间进行校时。校“秒”时,采用等待校时。校“分”、“时”采用加速校时。

对校时电路的要求:

在小时校正时不影响分和秒的正常计数 。

在分校正时不影响秒和小时的正常计数 。

4.3.6 总体电路设计

图8 总体电路图

5 仿真、调试及结果分析

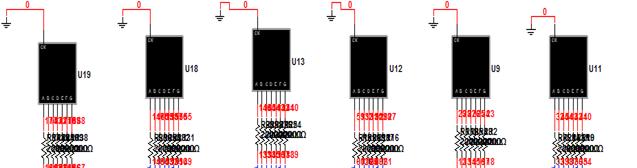

数码管显示如9所示:

![说明: C:\Users\张平\AppData\Roaming\Tencent\Users\1833865351\QQ\WinTemp\RichOle\~N74A]$G3U[$H5T3N`YY_}N.jpg](https://upload2.fanwen118.com/wk001/3995519/3995519_img_009.jpg)

图9 数码管

数码显示电路统一采用共阴的数码管及其配套的74LS48,U14、U20可以准确显示六十进制的秒;U16、U15可以准确显示六十进制的分;U18、U17可以准确显示十二进制的时。

脉冲发生器产生波形如图10所示:

![说明: C:\Users\张平\AppData\Roaming\Tencent\Users\1833865351\QQ\WinTemp\RichOle\HAPHR(WP5]MHPMB(K8Y21NQ.jpg](https://upload2.fanwen118.com/wk001/3995519/3995519_img_010.jpg)

图10脉冲发生器波形图

由集成电路定时器555与RC组成的多谐振荡器作为时间标准信号源。从输出端可以得到可以忽略误差接近1Hz的方波信号。从波形可以看出,脉冲发生器产生的方波信号占空比十分接近50%,频率为1Hz,符合实验要求。

6 主要仪器与设备

集成芯片 74LS160—6片,74LS48—6片,555定时器一片,七段显-6片

滑动变电阻器 200Ω—42只,1kΩ-2只,5kΩ—2只

电 容 0.001uF—1只,2uF—1只。

TTL与非门 5只

TTL非门 2只

共阴极LED显示 6只。

按键 3只。

7 小结、体会

小结、体会:在这次课程设计中,自己亲自动手查阅资料、设计方案、软件仿真和与组员一起完成多功能数字钟的制作,最后看到老师的好评时心里感到由衷地欣慰。

课程设计进一步加深了对数字电子技术的认识,熟悉了对Multisim软件的学习和使用,在仿真过程中出现较多的问题,通过自己的努力和同学的帮助都一一解决了。首先在仿真时发现数码管不能正常显示,经过查验发现,555与RC构成的脉冲发生器的封装存在问题。其次,因电子电路中用网络编号表示线路连接不如手绘电路直观,检查起来不是很方便,最后在组员的指导下,看熟了之后很容易的就能看出线路分布,从而进行进一步调试改善电路功能。

调试时有的器件在理论上可行,但在实际运行中就无法看到效果,所以得换不少器件,有时无法找出错误便更换器件重新接线以使电路正常运行。在整个设计中,74LS160的接线比较困难,反复修改了多次,在认真学习其用法后采用归零法和置数法设计出60进制和24进制的计数器。

通过这次对数字时钟的设计与仿真及制作,为以后的电路设计打下良好的基础,得到了一些宝贵经验和教训,加强了自己的动手能力和协同合作能力,为以后的学习和工作提供了良好的范例,我会把这种认真和实在带到以后的生活当中。

8.参考文献

1.数字电子技术基础(第五版),阎石主编 ,高等教育出版

2.电路设计与仿真,杨欣 王玉凤 刘湘黔编著,清华大学出版社

3数字电路与逻辑设计,刘培植主编,北京邮电大学出版社

4电子设计,蔡明生主编,高等教育出版社

第二篇:VHDL数字钟设计报告

VHDL数字钟设计报告

一. 数字钟总体设计方案:

1.1设计目的

①正确显示时、分、秒;

②可手动校时,能分别进行时、分的校正;

③整点报时功能;

1.2设计思路

数字钟的设计模块包括:分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路、整点报时和译码显示电路。

每一个功能模块作为一个实体单独进行设计,最后再用VHDL的例化语句将各个模块进行整合,生成顶层实体top。

该数字钟可以实现3个功能:计时功能、设置时间功能和报时功能。

二.数字钟模块细节

2.1 分频器(fenpin)

本系统共需3种频率时钟信号(1024Hz、512Hz、1Hz)。为减少输入引脚,本系统采用分频模块,只需由外部提供1024Hz基准时钟信号,其余三种频率时钟信号由分频模块得到。

分频原理:为以1024Hz基准时钟经1024分频得到512Hz,1Hz频率时钟信号。

分频器管脚

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity fenpin is

port(clk1024:in std_logic;

clk1,clk512:out std_logic

);

end fenpin ;

architecture cml of fenpin is

begin

process (clk1024)

variable count1: integer range 0 to 512;

variable q1: std_logic;

begin

if clk1024' event and clk1024='1' then

if count1=512 then

q1:=not q1;

count1:=0;

else

count1:=count1+1;

end if;

end if;

clk1<=q1;

end process;

process(clk1024)

variable count512: integer range 0 to 1;

variable q512: std_logic;

begin

if clk1024' event and clk1024='1' then

if count512=1 then

q512:=not q512;

count512:=0;

else

count512:=count512+1;

end if;

end if;

clk512<=q512;

end process;

end cml;

2.2 校时电路(jiaoshi)

本模块要实现的功能是:正常计时、校时、校分在每个状态下都会产生不同控制信号实现相应的功能。

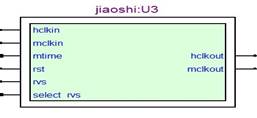

校时管脚图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jiaoshi is

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:in std_logic;

hclkout,mclkout:out std_logic

);

end jiaoshi;

architecture cml of jiaoshi is

signal h_m:std_logic;

begin

p1:process(rst,rvs,hclkin,mclkin,h_m,mtime)

begin

if rst='0' then

null;

elsif rvs='1' then

hclkout<=hclkin;

mclkout<=mCLKin;

elsif h_m='0' then

hclkout<=hclkin;

mclkout<=mtime;

else

hclkout<=mtime;mclkout<=mclkin;

end if;

end process;

p2:process(select_rvs)

begin

if select_rvs'event and select_rvs='1' then

h_m<=not h_m;

end if;

end process ;

end cml;

管脚图

仿真图

2.3 时计数器(hour)分计数器(mine)秒计数器(second)

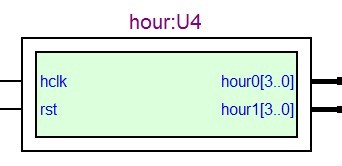

时计数器管脚图

时代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity hour is

port(rst,hclk:in std_logic;

hour0,hour1:buffer std_logic_vector(3 downto 0 )

);

end hour;

architecture cml of hour is

begin

process(rst,hclk,hour0,hour1)

begin

if rst='0' then

hour0<="0000";

hour1<="0000";

elsif hclk'event and hclk='1' then

if hour0="0011" and hour1="0010" then

hour0<="0000";

hour1<="0000";

elsif hour0="1001" then

hour0<="0000";

hour1<=hour1+1;

else

hour0<=hour0+1;

end if;

end if;

end process ;

end cml;

分计数器管脚图

分代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mine is

port(rst,mclk:in std_logic;

mco:out std_logic;

min0,min1:buffer std_logic_vector(3 downto 0 )

);

end mine;

architecture cml of mine is

signal min0_t,min1_t:std_logic_vector(3 downto 0 );

begin

process(rst,mclk,min0,min1)

begin

if rst='0' then

min0<="0000";

min1<="0000";

elsif mclk'event and mclk='1' then

if min0="0101" and min1="1001" then

min0<="0000";

min1<="0000";

mco<='1';

elsif min0="0010" and min0="1001" then

min1<="0011";

min0<="0000";

mco<='0';

elsif min0="1001" then

min1<=min1+1;

min0<="0000";

else

min0<=min0+1;

end if;

end if;

end process ;

end cml;

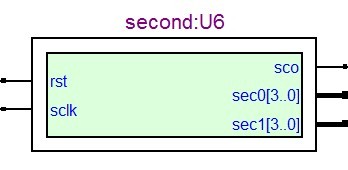

秒计数器管脚图

秒代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity second is

port(rst,sclk:in std_logic;

sco:out std_logic;

sec0,sec1:buffer std_logic_vector(3 downto 0 )

);

end second;

architecture cml of second is

signal sec0_t,sec1_t:std_logic_vector(3 downto 0 );

begin

process(rst,sclk,sec0,sec1)

begin

if rst='0' then

sec0<="0000";

sec1<="0000";

elsif sclk'event and sclk='1' then

if sec0="0101" and sec1="1001" then

sec0<="0000";

sec1<="0000";

sco<='1';

elsif sec0="0010" and sec0="1001" then

sec1<="0011";

sec0<="0000";

sco<='0';

elsif sec0="1001" then

sec1<=sec1+1;

sec0<="0000";

else

sec0<=sec0+1;

end if;

end if;

end process ;

end cml;

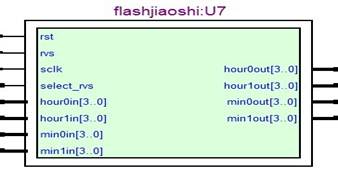

2.4 校时闪烁电路(flashnjiaoshi)

如果正在进行校时,flashjiaoshi将实现使当前正在校时项(小时或分钟)以1Hz的频率闪烁,以便于操知道正在被校正。

校时闪烁电路管脚图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity flashjiaoshi is

port(rst,sclk,rvs,select_rvs:in std_logic;

hour0in,hour1in,min0in,min1in:in std_logic_vector(3 downto 0 );

hour0out,hour1out,min0out,min1out :out std_logic_vector(3 downto 0 )

);

end flashjiaoshi;

architecture cml of flashjiaoshi is

signal h_m:std_logic;

begin

p1:process(rst,sclk,rvs,hour0in,hour1in,min0in,min1in,h_m)

begin

if rst='0' then

null;

elsif rvs='1' then

hour0out<=hour0in;

hour1out<=hour1in;

min0out<=min0in;

min1out<=min1in;

elsif h_m='0' then

hour0out<=hour0in;

hour1out<=hour1in;

if sclk='1' then

min0out<=min0in;

min1out<=min1in;

else

min0out<="1111";

min1out<="1111";

end if;

else

min0out<=min0in;

min1out<=min1in;

IF sCLK='1' then

hour0out<=hour0in;

hour1out<=hour1in;

else

hour0out<="1111";

hour1out<="1111";

end if;

end if;

end process p1;

p2:process(select_rvs)

begin

if select_rvs'event and select_rvs='1' then

h_m<=not h_m;

end if;

end process p2;

end cml;

2.5 整点报时电路

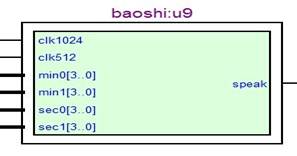

整点报时管脚图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity baoshi is

port( clk1024,clk512 : in std_logic;

min0,min1 , sec0,sec1 : in std_logic_vector (3 downto 0);

speak : out std_logic);

end baoshi;

architecture cml of baoshi is

begin

speak<=clk512

when (min1="0101" and min0="1001" and sec1="0101") and (sec0="0011" or sec0="0101" or sec0="0111") else

clk1024

when( min1="0101" and min0="1001" and sec1="0101" and sec0="1001") else

'0';

end cml;

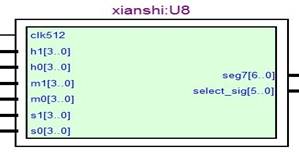

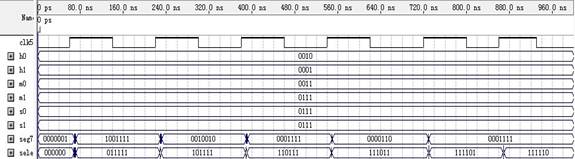

2.6 译码显示电路

该显示用的是动态扫描电路

译码显示管脚图

波形图

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity xianshi is

port(clk512:in std_logic;

h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0 );

seg7:out std_logic_vector(6 downto 0 );

select_sig:out std_logic_vector(5 downto 0 )

);

end xianshi;

architecture cml of xianshi is

signal data:std_logic_vector(3 downto 0 );

signal order:std_logic_vector(2 downto 0 );

begin

process(clk512)

begin

if clk512' event and clk512='1' then

case order is

when "000"=>data<=h1;select_sig<="011111";

when "001"=>data<=h0;select_sig<="101111";

when "010"=>data<=m1;select_sig<="110111";

when "011"=>data<=m0;select_sig<="111011";

when "100"=>data<=s1;select_sig<="111101";

when "101"=>data<=s0;select_sig<="111110";

when others=>data<="1000";select_sig<="111111";

end case;

if order="101" then order<="000";

else order<=order+1;

end if;

end if;

end process ;

process(data)

begin

case data is

when "0000" =>seg7 <= "0000001";

when "0001" =>seg7 <= "1001111";

when "0010" =>seg7 <= "0010010";

when "0011" =>seg7 <= "0000110";

when "0100" =>seg7 <= "1001100";

when "0101" =>seg7 <= "0100100";

when "0110" =>seg7 <= "0100000";

when "0111" =>seg7 <= "0001111";

when "1000" =>seg7 <= "0000000";

when "1001" =>seg7 <= "0000100";

when others =>seg7 <= "1111111";

end case;

end process ;

end cml ;

2.7 数字钟整体设计 (top)

本数字钟的设计包括分频器、去抖动电路、校时电路、“时、分、秒”计数器、校时闪烁电路和译码显示电路。以上已经有了各个功能模块的实现方法,现在将各个模块综合在一起,构成一个完整的数字钟。

代码:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity top is

port(clk1024,key,reset:in std_logic;

keyin:in std_logic_vector(1 downto 0 );

select_sigout:out std_logic_vector(5 downto 0 );

seg7out:out std_logic_vector(6 downto 0 );

speak:out std_logic

);

end top;

architecture cml of top is

component fenpin is

port(clk1024:in std_logic;

clk1,clk512:out std_logic

);

end component fenpin ;

component jiaoshi is

port(rst,rvs,select_rvs,mtime,mclkin,hclkin:in std_logic;

hclkout,mclkout:out std_logic

);

end component jiaoshi;

component hour is

port(rst,hclk:in std_logic;

hour0,hour1:buffer std_logic_vector(3 downto 0 )

);

end component hour;

component minute is

port(rst,mclk:in std_logic;

mco:out std_logic;

min0,min1:buffer std_logic_vector(3 downto 0 )

);

end component minute;

component second is

port(rst,sclk:in std_logic;

sco:out std_logic;

sec0,sec1:buffer std_logic_vector(3 downto 0 )

);

end component second;

component flashjiaoshi is

port(rst,sclk,rvs,select_rvs:in std_logic;

hour0in,hour1in,min0in,min1in:in std_logic_vector(3 downto 0 );

hour0out,hour1out,min0out,min1out :out std_logic_vector(3 downto 0 )

);

end component flashjiaoshi;

component xianshi is

port(clk512:in std_logic;

h1,h0,m1,m0,s1,s0:in std_logic_vector(3 downto 0 );

seg7:out std_logic_vector(6 downto 0 );

select_sig:out std_logic_vector(5 downto 0 )

);

end component xianshi;

component baoshi is

port( clk1024,clk512 : in std_logic;

min0,min1 , sec0,sec1 : in std_logic_vector (3 downto 0);

speak : out std_logic);

end component baoshi;

signal scanCLKSig : std_logic;

signal secCLKSig : std_logic;

signal hCLKSig0,hCLKSig1 : std_logic;

signal mCLKSig0,mCLKSig1 : std_logic;

signal sec1Sig,sec0Sig : std_logic_vector(3 downto 0);

signal min1Sig0,min0Sig0 : std_logic_vector(3 downto 0);

signal min1Sig1,min0Sig1 : std_logic_vector(3 downto 0);

signal hour1Sig0,hour0Sig0 : std_logic_vector(3 downto 0);

signal hour1Sig1,hour0Sig1 : std_logic_vector(3 downto 0);

begin

U1: fenpin PORT MAP(clk1024=>clk1024,clk512=>scanCLKSig,clk1=>secCLKSig);

U2: jiaoshi PORT MAP(rst=>reset, rvs=>key, select_rvs=>keyin(0),

mtime=>keyin(1),

hclkin=>hCLKSig0,mclkin=>mCLKSig0,hclkout=>hCLKSig1,mclkout=>mCLKSig1);

U3:hour PORT MAP(rst=>reset, hCLK=>hCLKSig1, hour1=>hour1Sig0,

hour0=>hour0Sig0);

U4: minute PORT MAP(rst=>reset, mclk=>mCLKSig1, mco=>hCLKSig0,

min1=>min1Sig0, min0=>min0Sig0);

U5: second PORT MAP(rst=>reset, sCLK=>secCLKSig, sco=>mCLKSig0, sec1=>sec1Sig,

sec0=>sec0Sig);

U6: flashjiaoshi PORT MAP(rst=>reset, sclk=>secCLKSig, rvs=>key,

select_rvs=>keyin(0), hour1in=>hour1Sig0, hour0in=>hour0Sig0, min1in=>min1Sig0,

min0in=>min0Sig0, hour1out=>hour1Sig1, hour0out=>hour0Sig1, min1out=>min1Sig1,

min0out=>min0Sig1);

U7: xianshi PORT MAP(clk512=>scanCLKSig, h1=>hour1Sig1, h0=>hour0Sig1, m1=>min1Sig1,

m0=>min0Sig1, s1=>sec1Sig, s0=>sec0Sig, seg7=>seg7out, select_sig=>select_sigout);

u8:baoshi PORT MAP(clk1024=>clk1024,clk512=>scanCLKSig,sec1=>sec1Sig,sec0=>sec0Sig,

min1=>min1Sig0,min0=>min0Sig0,speak=>speak);

END cml;