课程设计(综合实验)报告

( 2011 -- 2012 年度第 1 学期)

名 称:VHDL语言与系统设计

题 目:电子秒表

院 系:电气与电子工程学院

班 级: 信息1001、1002班

学 号:1101200112

1101200225

1101200228

学生姓名:刘东俊、周晨轶、赵照迪

指导教师: 陈晓梅

设计周数: 2周

成 绩:

日期: 20##年 1月 11日

《VHDL语言与数字系统设计》课程设计

任 务 书

一、目的与要求

本课程设计是学生在完成数字电子技术基础课程的学习后,使用VHDL硬件描述语言和可编程逻辑器件进行电路设计的实践课程。主要内容包括:

二、主要内容

1. VHDL的基本知识:实体,结构体,数据类型,对象.

2. VHDL的描述方法:行为描述,数据流描述,结构描述.

3. 组合逻辑电路和时序逻辑电路的VHDL模型

4. 数字系统设计实例

三、进度计划

四、设计(实验)成果要求

1. 对于基础实验部分,完成程序的校对和修改,理解各种典型单元电路的设计思路。展示仿真波形和RTL综合电路图。

2. 对于电子综合题目设计部分,独立完成具有特定功能的综合电子系统的VHDL描述,并展示仿真波形和RTL综合电路图,验证设计功能。并分析和说明设计思路。

五、考核方式

平时出勤10分

基础实验调试 30 分

综合设计题目展示和答辩 50分

实验报告 10分

注:根据课程设计、综合实验的内容将标题任选其一。

学生姓名:刘东俊、周晨轶、赵照迪

指导教师: 陈晓梅

20##年 1月 11 日

一、 课程设计(综合实验)的目的与要求

1.1设计实验目的与要求

设计一个电子秒表,具有以下要求:

1. 利用计数器接受分频电路输出的计数脉冲,并通过数码显示器显示出来,完成0.1—99.9s的秒表计时。

2. 使用基本RS触发器及其他外围电路制作电子秒表的控制开关,实现“开始计数”,“停止并保持计数”和“清零并准备开始重新开始计数”的功能。在秒表计数期间应使“开始计数”

和“清零并准备重新开始计数”无效。

3.培养我们运用有关课程的基础理论和技能解决实际问题,并进一步提高专业基本技能、创新能力。通过课程设计,学习到设计写作方法,能用文字、图形和现代设计写作方法系统地、正确地表达课程设计和研究成果。

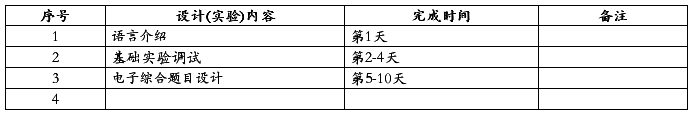

1.2 系统设计

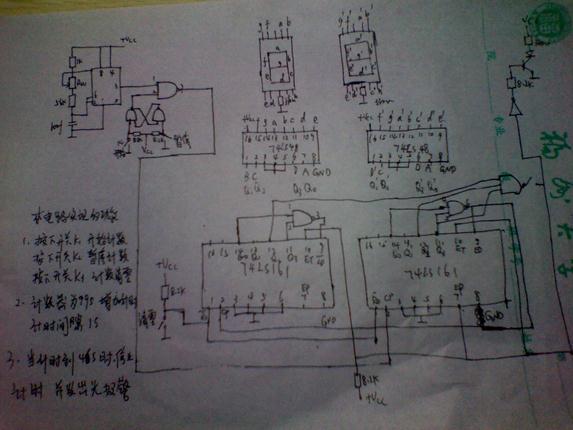

根据数字秒表的功能,可以将系统电路划分为4部分:R,S锁存器、计数器、十分频和与门。其中含3个十进制计数器 实验中总共包括3要点:计数、保持原态和清零,通过以上部分可以实现上述要求。

:

(1)RS触发器

设计思路:要实现计数、暂停和清零等功能,需先设计出一个RS触发器、 RS触发器:

--RS

Library IEEE ;

use IEEE.std_logic_1164.all ;

ENTITY latchinf IS

PORT

(R, S : IN std_logic;

q : OUT std_logic);

END latchinf;

ARCHITECTURE maxpld OF latchinf IS

BEGIN

latch : PROCESS (R, S)

BEGIN

IF R = '0' AND S='1' THEN

q <= '0';

elsIf S='0'AND R='1' THEN

q<='1';

END IF;

END PROCESS latch;

END maxpld;

当R=1、S=0时,Q=1;

当R=0、S=1时,Q=0;

当R=1、S=1时,Q保持不变。

(2)计数器:用来实现从0.1~99.9的计数功能,由3个十进制计数器构成

library ieee;

use ieee.std_logic_1164.all;

entity counters4 is port

( clk:in std_logic;

clear:in std_logic;

x1:out std_logic_vector(3 downto 0);

x2:out std_logic_vector(3 downto 0);

x3:out std_logic_vector(3 downto 0));

end counters4;

architecture A of counters4 is

component counters3

port (clk:in std_logic;

clear:in std_logic;

qg3:out std_logic_vector(3 downto 0));

end component;

signal s1,s2:std_logic_vector(3 downto 0);

begin

A: counters3 port map(clk ,clear,s1);

A1:x1<=s1;

B: counters3 port map(s1(3),clear,s2);

B1:x2<=s2;

C: counters3 port map(s2(3),clear,x3);

end A;

当时钟来下降沿时计数,分别在3个输出端输出3个四位二进制数;

当清零端来高电频时实现异步清零。

(3)十分频:将输入的0.01S转化为0.1S的时钟

Library IEEE ;

use IEEE.std_logic_1164.all ;

use IEEE.std_logic_unsigned.all ;

ENTITY counters3 IS

PORT (clk : IN std_logic;

clear : in std_logic;

qg3 : OUT std_logic_vector(3 downto 0) );

END counters3;

-- A synchronous clear enable counter

architecture A of counters3 is

begin

counter_process:

PROCESS (clk)

VARIABLE cnt : std_logic_vector(3 downto 0);

BEGIN

if clear='1' then cnt :="0000";

elsiF clk'EVENT AND clk ='0' THEN

if cnt ="1001" THEN

cnt := "0000";

else cnt := cnt+1;

END IF;

END IF;

qg3 <= cnt;

END PROCESS;

end a;

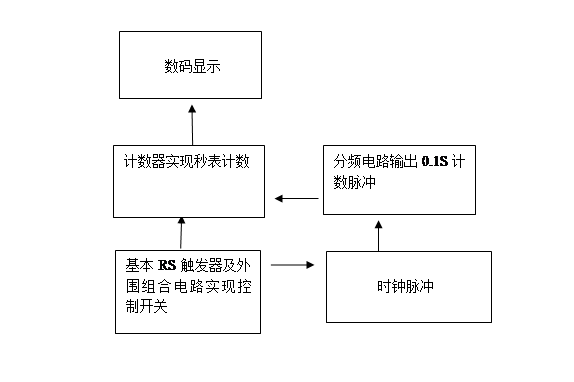

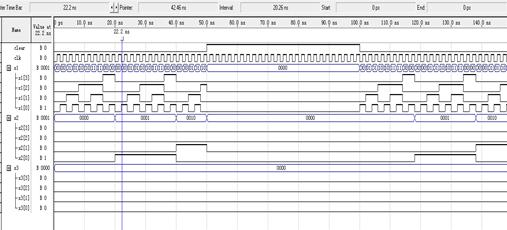

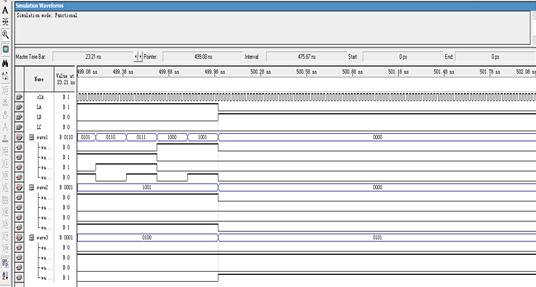

运行波形如下

图为十进制计数器实现异步清零,取最高位实现十分频功能。

(4)与门:基本元件

Library IEEE ;

use IEEE.std_logic_1164.all ;

entity and1 is port

(m:in std_logic;

n:in std_logic;

mn:out std_logic);

end entity;

architecture and11 of and1 is

begin mn<=m and n;

end and11;

只要m或n中有一个为0,输出就为0。

1.3总的程序设计

将以上几个模块利用port map语句连接起来,注意添加局部信号变量,运行即可。

Library IEEE ;

use IEEE.std_logic_1164.all ;

entity dianzimiaobiao is

port(LA:in std_logic;

LB:in std_logic;

LC:in std_logic;

clk:in std_logic;

wave1:out std_logic_vector(3 downto 0);

wave2:out std_logic_vector(3 downto 0);

wave3:out std_logic_vector(3 downto 0));

end dianzimiaobiao;

architecture dianzimiaobiao1 of dianzimiaobiao is

component counters3

port( clk : IN std_logic;

clear : IN std_logic;

qg3 : OUT std_logic_vector(3 downto 0));

end component;

component counters4

port( clk : IN std_logic;

clear : IN std_logic;

x1:out std_logic_vector(3 downto 0);

x2:out std_logic_vector(3 downto 0);

x3:out std_logic_vector(3 downto 0));

end component;

component latchinf

PORT(

R, S : IN std_logic;

q : OUT std_logic);

end component;

component and1

port(m:in std_logic;

n:in std_logic;

mn:out std_logic);

end component;

signal Q,

X,

Y:std_logic;

signal Z: std_logic_vector(3 downto 0);

begin

a: latchinf port map(LA,LB,Q);

b: and1 port map(Q,clk,X);

c: and1 port map(not Q,LC,Y);

d: counters3 port map(X,'0',Z);

e: counters4 port map(Z(3),Y,wave1,wave2,wave3);

end dianzimiaobiao1;

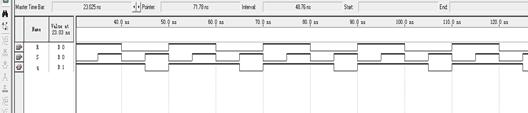

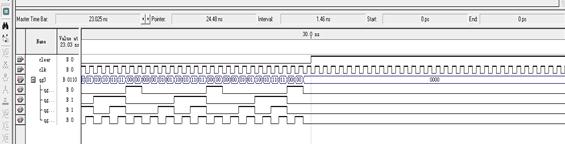

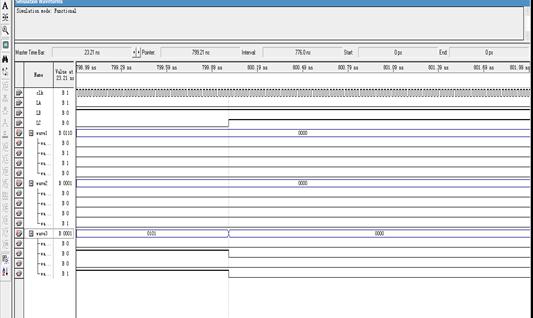

运行波形如下

加计数:

当LA=1 LB=0时,实现加计数。

保持状态:

当LA=0 LB=1时,保持原状态不变。

清零:

在保持的基础上,使LC=1,实现清零功能。

二、 感想

经过这次的数字电子秒表的VHDL课程设计后,我从中学到了好多东西。在我们上了一个学期的数字电子技术基础课后,我们已经对数字电子技术有一定的了解,加上之前学过的电路课,我们可以独立完成数字电子技术基础课程设计了,不过当中还是遇到许多不懂的问题。通过这次自己动手的课程设计,我学会了设计数字电子电路的一般方法,还进一步熟悉数字电子器件的使用。这个课程设计课我还不是很熟悉,第一次做难免会感到陌生,而且对很多基本的东西都不是很清楚,在一定程度上影响了我们的课程设计的质量,希望能在以后的时间里认真学习好这些基础的东西。我对这个课程设计课有着深刻的体会:要想做好这个课程设计,就必须认认真真地去做,不要怕麻烦,遇到不懂的问题就要主动去问同学或者老师。最后我希望课程设计课能够再多一点给我们提供动手的机会,并让我们多点发挥主观能动性和创造能力,这样可以在学到东西的同时又能发散大家的思维。

总之,通过这次练习我有了很多收获。在摸索该如何设计电路使之实现所需功能的过程中,特别有趣,培养了我的设计思维,增强了动手能力。

三、 参考文献

科学出版社 EDA技术实用教程(潘松、黄继业编著)。

第二篇:电子秒表实验报告

电子技术设计性

实训报告

学 号: ##

姓 名: ##

同组人: ##

班 级: 03班

指导老师: ##

日 期: 20##.09.07

目 录

一.实训目的---------------------------------------------------3

二.设计功能要求---------------------------------------------3

三.电路设计---------------------------------------------------4

(一)电路框图--------------------------------------------4

(二)单元电路分析-------------------------------------4

四.设计总图及其工作原理---------------------------------5

(一)工作原理--------------------------------------------5

(二)元件清单--------------------------------------------5

五. 电路调试--------------------------------------------------6

(一) 调试过程--------------------------------------------6

(二)故障分析与排除-----------------------------------7

六.实训心得---------------------------------------------------8

一. 实验目的

1. 对芯片74LS160芯片以及555的功能的更形象的认知。

2.增强使用EWB软件的能力。

3.进一步提高独立分析问题和解决问题的能力。

4.掌握数字系统的分析和设计方法。

5.对数字集成电路的综合应用有进一步的认识和理解。

二. 设计题目:制作一个简易的电子秒表

功能要求:

1 具有两位数码显示。分别显示1/10秒和秒计数。

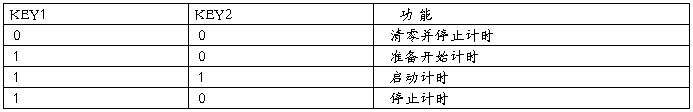

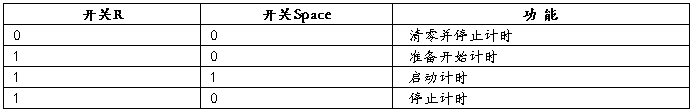

2 有两个按键分别控制启动(开始计时)/停止和清零。功能表如下:

概述:

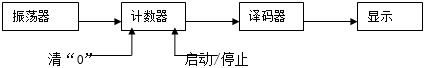

要完成题目要求的电子秒表功能,系统应具有如下几部分电路:

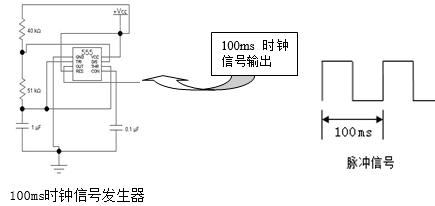

1.定时电路;题目要求最小计时单位为1/10秒,即100ms。这部分电路必须能准确的产生周期为100ms(频率为10Hz)的时钟信号。

2.计时电路:题目要求系统具有两位显示器,分别显示秒和1/10秒信号。所以本系统应具有两个十进制计数器,分别对定时信号进行计数,以产生1/10秒和秒计数。系统计数范围从0.0~9.9秒。

3.显示译码驱动电路:将计数器的计数结果(BCD码)通过译码器译成七段显示码并驱动LED数码管显示出来。

4.控制电路:根据题目要求,本电子秒表应具有两个按键。其中一个控制秒表的启/停,本按键应有自锁功能,按一次启动计时,再按一次停止计时。另一个按键控制清“0”,本按键不需自锁,按下时系统清“0”;放开时系统回复正常计时功能。系统电路结构框图如图1所示。

图1 系统结构框图

四、电路设计方案:

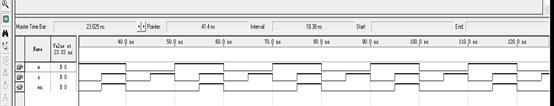

1、定时电路:系统的定时电路要求产生周期为100ms的时钟信号。由于在此实验前我们学过555定时器,故可用时钟信号发生器来实现。

定时器是电子秒表的核心,其作用是产生一个标准频率10赫兹的脉冲信号。振荡频率的精度和稳定度决定了秒表的质量(如图2 ),图3为脉冲信号宽度。

图2 时钟信号发生器

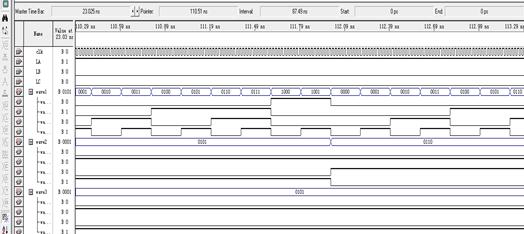

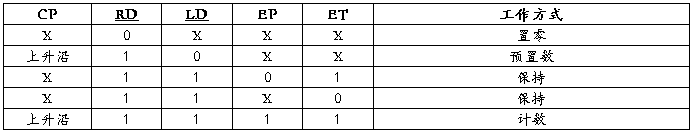

2、计时电路:本电路需要两位十进制加法计数器,对定时电路的时钟信号进行计数。可用两片74LS160实现。74LS160是同步十进制加法计数器,其功能表如下:

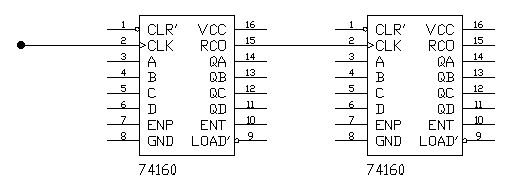

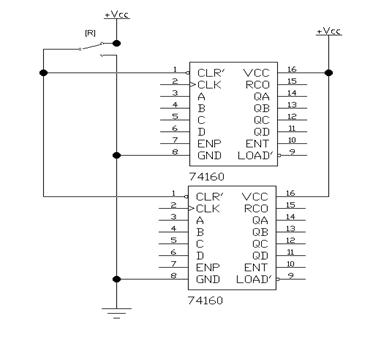

应用两片74LS160组合级联可构成10进制计数器。其级联方式可分为串行进位方式和并行进位方式两种。串行进位方式接法如图3所示。

图3 串行进位方式连接图

在串行进位方式中,将高位的74LS160的CP与低位的进位端C相接,当低位计数器计满产生进位时就会给高位计数器一个脉冲,使高位计数器加1。

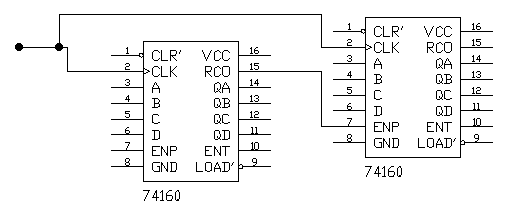

图4、 并行进位方式连接图

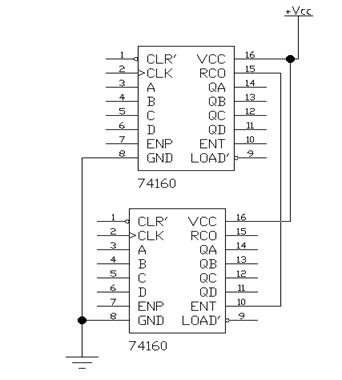

并行进位方式接法如图4所示。它是将高低位计数器的CP接在一起并将低位计数器的进位C与高位计数器的EP接起来。当低位计数器尚未计满时,其进位端C输出低电平使高位计数器处于保持状态(不计数);当低位计数器计满产生进位时,C输出高电平使高位计数器处于计数状态,定时脉冲一到高位计数器加1。同时低位计数器回零,C输出低电平,高位计数器又处于保持状态直到第二个进位脉冲的到来。

3、显示译码电路

显示译码电路根据显示器件的不同可有不同的器件选择,如74LS47(适合于驱动共阳接法的LED数码管)和74LS48(适合于驱动共阴接法的LED数码管),本实验提供的器件为共阴LED数码管,所以选用74LS48。其电路为如下图5:

图5、74LS48与共阴LED数码管组成的译码显示电路

4、控制电路

系统要求具有清“0”和启/停按键。对于清零功能,根据计数器74LS160的功能表,我们知道,74LS160提供了清零引脚,只要将该引脚置低电平,计数器既实现清零功能。具体接法如图6。

图6、实现清零功能电路

对于启/停控制,我们从74LS160的功能表可知,当ET端为低电平,计数器将处于保持状态(停止记数)。当ET端为高电平且其他控制引脚均满足计数条件时,计数器才开始计数。我们可采用图7的电路来实现启/停控制。当开关按下时,ET=“0”;放起时,ET=“1”。

五、应用EWB电子仿真软件进行设计仿真

1、定时电路的仿真调试

在计算机上运行EWB并调出时钟发生信号仿真运行达到预定目标,电路产生周期为100ms 的时钟信号。

2、计时及控制电路。

按并行进位方式接法,电路工作正常。按串行方式接法,结果出现了当低位计数到“9”时,高位立即显示“1”的情况。经分析,原来74LS160的进位C属于超前进位。当低位计数到“9”时,进位端即产生一从“0”到“1”的跳变。而74LS160的CP输入端是上升沿有效的,此时高位的计数器即从“0000”变为“0001”了,所以出现 了“19”的显示结果。要解决这一问题,只需将进位信号作为控制ENT端的一个信号,因为ENT为高电平有效,所以进位“0”到“1”的跳变不用担心超前进位而产生“19”的情况。

图8 并行进位示意图

3、显示译码电路

按设计方案接线,电路逻辑正常。

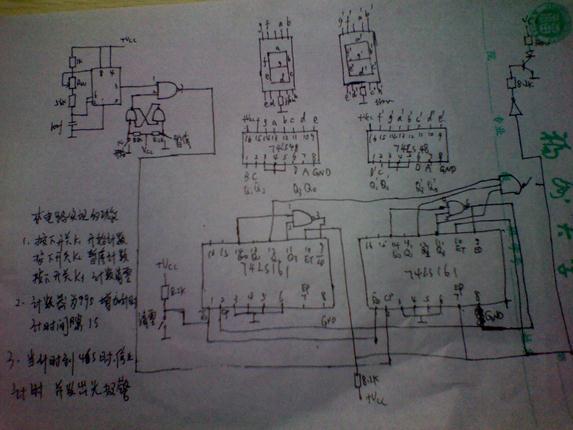

由上设计方案,该实现电子秒表功能的电路如下图9:

图9、实现电子秒表功能的电路

4、测试结果:

本电路通过两个开关R、Space来实现电路的控制启动(开始计时)/停止和清零,其测试结果为:

第一个数码管显示的是1/10秒,第二个数码管显示的是1秒,测试结果为:两个数码管显示的数字为00-99,即系统计数范围从0.0~9.9秒。

由此可知,该电路测试结果正确。

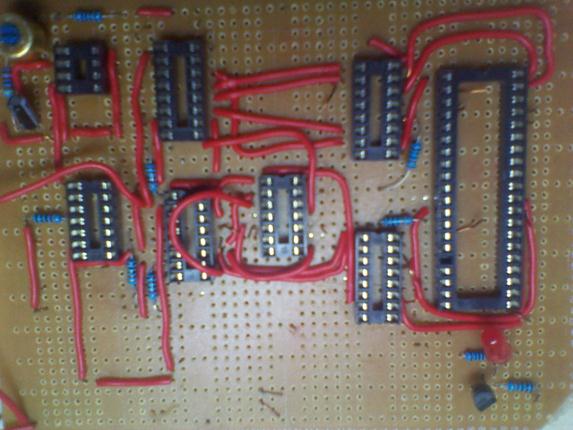

实物图:

六、总结

通过了这次的计数器电路的设计以及硬件电路的实现,我更好地掌握了各方面的知识。首先是74LS160的功能,懂得实际应用上,应用串行和并行方式进行连接电路实现计数器的级联电路,进一步可以利用多片芯片设计各进制的计数电路。通过设计重启和停止,启动计数键,我更好的理解了74LS160各引脚的功能和用法。在利用555产生时钟信号时,我也学会了用这个芯片输出不同的频率的信号。利用软件进行仿真时,我对EWB软件的功能有了进一步的认识并且会用其他一些复杂一些的功能。

学这门课就应该实践和理论结合在一起,像这次做计数器就是一个很好的途径。因为这样可以加深对理论知识的理解,还可以增强个人的动手能力以及设计、开放的能力。