一、课程名称:

EDA技术实验

二、教材名称:

《EDA技术使用教程》,潘松等编著。

三、本课程教学目的、要求:

介绍EDA的基本知识、常用的EDA工具的使用方法和目标器件的结构原理、VHDL设计输入方法(图形和文本)、VHDL仿真、VHDL的设计优化等。

EDA技术作为重要的专业课程,其实践性强。在教学时要注重理论和实践的紧密结合,通过大量上机操作,使学生掌握VHDL的基本结构和编程思想。

实验1 原理图输入方法及8位全加器设计(4课时)

1) 实验目的:

熟悉利用MAX+plusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行电子电路设计的详细流程。

2) 实验报告要求:

详细叙述8位加法器的设计流程;给出各层次的原理图及其对应的仿真波形图;给出加法器的延时情况。

3) 实验步骤:

(1) 设计一个一位半加器。

步骤1:输入设计项目和存盘

步骤2:输入半加器元件:

步骤3:将项目设置为工程文件

步骤4:选择目标器件并编译

步骤5:时序仿真

步骤6:包装元件入库

选择菜单“File”→“Open”,在“Open”对话框中选择原理图编辑文件选项“Graphic Editor Files”,然后选择h_adder.gdf,重新打开半加器设计文件,然后选择如图4-5中“File”菜单的“Create Default Symbol”项,将当前文件变成了一个包装好的单一元件(Symbol),并被放置在工程路径指定的目录中以备后用。

(2) 利用半加器组成一个一位全加器,并记录仿真结果。

(3) 利用全加器组成一个八位全加器,并记录仿真结果。

实验二 简单组合电路和时序电路设计(4课时)

一、实验目的:

熟悉Max+plusⅡ的VHDL文本设计流程全过程,学习简单组合电路和时序电路的设计和仿真方法。

二、实验内容

1:首先利用MAX+plusⅡ完成2选1多路选择器和一位全加器的文本编辑输入和仿真测试等步骤,给出仿真波形,验证本项设计的功能。

2:设计触发器(J-K),给出程序设计、软件编译、仿真分析、硬件测试及详细实验过程。

3:先设计或门和一位半加器的VHDL描述文件,并进行仿真调试,再用元件例化的方法实现一位全加器,并仿真调试。要求记录VHDL文件内容和仿真波形结果。

4:用一位全加器设计8为全加器。要求记录VHDL文件内容和仿真波形结果。(选作)

参考程序

ENTITY mux21a IS

PORT ( a, b : IN BIT;

s : IN BIT;

y : OUT BIT );

END ENTITY mux21a;

ARCHITECTURE one OF mux21a IS

SIGNAL d,e : BIT;

BEGIN

d <= a AND (NOT S) ;e <= b AND s ;y <= d OR e ;

END ARCHITECTURE one ;

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2a IS

PORT (a, b :IN STD_LOGIC;

c : OUT STD_LOGIC );

END ENTITY or2a;

ARCHITECTURE fu1 OF or2a IS

BEGIN

c <= a OR b ;

END ARCHITECTURE fu1;

半加器描述(1)

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY adder IS

PORT (a, b : IN STD_LOGIC;

co, so : OUT STD_LOGIC);

END ENTITY adder;

ARCHITECTURE fh1 OF adder is

BEGIN

so <= NOT(a XOR (NOT b)) ; co <= a AND b ;

END ARCHITECTURE fh1;

1位二进制全加器顶层设计描述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY f_adder IS

PORT (ain,bin,cin : IN STD_LOGIC;

cout,sum : OUT STD_LOGIC );

END ENTITY f_adder;

ARCHITECTURE fd1 OF f_adder IS

COMPONENT h_adder

PORT ( a,b : IN STD_LOGIC;

co,so : OUT STD_LOGIC);

END COMPONENT ;

COMPONENT or2a

PORT (a,b : IN STD_LOGIC;

c : OUT STD_LOGIC);

END COMPONENT;

SIGNAL d,e,f : STD_LOGIC;

BEGIN

u1 : h_adder PORT MAP(a=>ain,b=>bin,co=>d,so=>e);

u2 : h_adder PORT MAP(a=>e, b=>cin, co=>f,so=>sum);

u3 : or2a PORT MAP(a=>d, b=>f, c=>cout);

END ARCHITECTURE fd1;

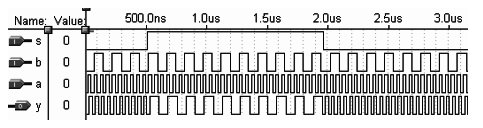

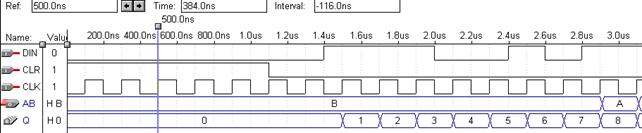

二选一多路选择器仿真结果:

实验三 含异步清0和同步时钟使能的4位加法计数器(4课时)

一、实验目的:

学习计数器的设计、仿真,进一步熟悉VHDL设计技术。

二、实验内容:

设计一含计数使能、异步复位和能进行计数值并行预置功能的4位加法计数器。RST是异步清零信号,高电平有效;clk是时钟输入信号;D0、D1、D2、D3是4位数据输入端(数据预置输入端)。Q0、Q1、Q2、Q3为计数器输出端。COUT为进位输出端。ENA为使能端,为‘1’时,计数器实现对CLK时钟脉冲信号的加1计数,为0时停止计数。

参考程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT4B IS

PORT (CLK : IN STD_LOGIC;

RST : IN STD_LOGIC;

ENA : IN STD_LOGIC;

OUTY : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : OUT STD_LOGIC );

END CNT4B;

ARCHITECTURE behav OF CNT4B IS

SIGNAL CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

P_REG: PROCESS(CLK, RST, ENA)

BEGIN

IF RST = '1' THEN CQI <= "0000";

ELSIF CLK'EVENT AND CLK = '1' THEN

IF ENA = '1' THEN CQI <= CQI + 1;

ELSE CQI <= "0000";

END IF; END IF;

OUTY <= CQI ;

END PROCESS P_REG ;

COUT <= CQI(0) AND CQI(1) AND CQI(2) AND CQI(3); --进位输出

END behav;

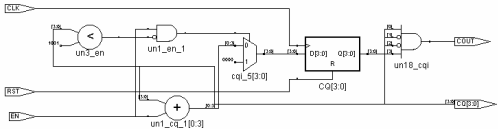

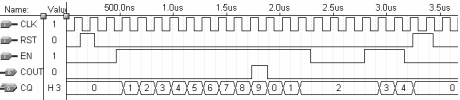

综合后的原理图:

仿真结果:

实验四 7段数码显示译码器设计(2课时)

一、实验目的:

1、学习7段数码显示译码器设计;

2、学习VHDL的多层次设计方法。

二、实验原理:

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。但为了简化过程,首先完成7段BCD码译码器的设计。例如输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是2进制的,所以输出表达都是16进制的,为了满足16进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。但为了简化过程,首先完成7段BCD码译码器的设计。例如输出为“1101101”时,数码管的7个段:g、f、e、d、c、b、a分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

图6-21 共阴数码管及其电路

三、实验内容

1、编程实现7段数码显示译码器设计;

2、对7段数码显示译码器设计进行编辑、仿真,给出其所有信号的时序仿真波形;

参考程序:

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DECL7S IS

PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ;

END ;

ARCHITECTURE one OF DECL7S IS

BEGIN

PROCESS( A )

BEGIN

CASE A IS

WHEN "0000" => LED7S <= "0111111" ; WHEN "0001" => LED7S <= "0000110" ;

WHEN "0010" => LED7S <= "1011011" ; WHEN "0011" => LED7S <= "1001111" ;

WHEN "0100" => LED7S <= "1100110" ; WHEN "0101" => LED7S <= "1101101" ;

WHEN "0110" => LED7S <= "1111101" ; WHEN "0111" => LED7S <= "0000111" ;

WHEN "1000" => LED7S <= "1111111" ; WHEN "1001" => LED7S <= "1101111" ;

WHEN OTHERS => NULL ;

END CASE ;

END PROCESS ;

END ;

仿真结果:

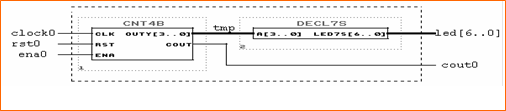

综合后的计数器和译码器连接电路的顶层文件原理图:

实验五 用状态机实现序列检测器的设计(4课时)

一、实验目的:

1、掌握状态机的编程方法和步骤;

2、掌握用状态机设计序列检测器的方法和步骤;

二、实验内容

用状态机编程实现对系列数“11100101”的检测,当某一系列串(以左移方式)进入检测器后,若该串与预置的系列数相同,则输出“A”,否则输出“B”。

三、实验步骤:

1、编辑系列检测器的VHDL程序;

2、仿真测试并给出仿真波形,了解控制信号的时序;

3、将上述方案改为系列检测密码为可预置(外部输入)情况,重新编写程序、编译和仿真,并记录仿真结果。

参考程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY SCHK IS

PORT ( DIN,CLK,CLR : IN STD_LOGIC;

AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));

END SCHK;

ARCHITECTURE behv OF SCHK IS

SIGNAL Q:INTEGER RANGE 0 TO 8;

SIGNAL D:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

D<="11100101";

PROCESS (CLK,CLR)

BEGIN

IF CLR= '1' THEN Q <= 0;

ELSIF clk='1' AND clk'EVENT THEN

CASE Q IS

WHEN 0 => IF DIN = D(7) THEN Q<=1;ELSE Q<=0;END IF;

WHEN 1 => IF DIN = D(6) THEN Q<=2;ELSE Q<=0;END IF;

WHEN 2 => IF DIN = D(5) THEN Q<=3;ELSE Q<=0;END IF;

WHEN 3 => IF DIN = D(4) THEN Q<=4;ELSE Q<=0;END IF;

WHEN 4 => IF DIN = D(3) THEN Q<=5;ELSE Q<=0;END IF;

WHEN 5 => IF DIN = D(2) THEN Q<=6;ELSE Q<=0;END IF;

WHEN 6 => IF DIN = D(1) THEN Q<=7;ELSE Q<=0;END IF;

WHEN 7 => IF DIN = D(0) THEN Q<=8;ELSE Q<=0;END IF;

WHEN OTHERS=> Q<=0;

END CASE;

END IF;

END PROCESS;

PROCESS(Q)

BEGIN

IF Q=8 THEN AB<="1010"; ELSE AB<="1011"; END IF;

END PROCESS;

END behv;

仿真结果:

提高型实验:

实验六 用VHDL实现数字钟及校园打铃系统(6课时)

一、实验目的及要求:

1、 掌握VHDL语言的基本结构及编程思想。

2、 掌握VHDL语言的进行系统设计的方法和步骤。

3、 提高学生综合应用能力。

二、实验内容:

1、用VHDL实现数字钟及校园打铃系统的软件编辑。

2、用VHDL实现数字钟及校园打铃系统的软件仿真。

三、实验步骤

1、 用VHDL编辑60进制计数器,并进行软件仿真。

2、 用VHDL编辑24进制计数器,并进行软件仿真。

3、 用VHDL编辑30进制计数器,并进行软件仿真。

4、 用元件例化的方法实现数字钟的软件编辑及软件仿真。

5、 实现数字钟的校时功能。

6、 实现数字钟的打铃功能。

7、 完成数字钟及校园打铃系统的实验报告。

实验七 A/D采样控制器设计

一、实验目的及要求:

1、掌握VHDL语言的基本结构及编程思想。

2、掌握A/D采样控制器的工作原理。

3、掌握A/D采样控制器的VHDL语言编程方法。

二、实验内容:

1、设计一A/D0809模数转换器控制器。

2、将转换结果送数码管显示器显示(2位)。

3、模拟输入通道为IN0。

三、实验步骤:

1、ADC0809特点介绍

(1)、单极性输入,8位A/D转换精度。

(2)、逐次逼近式,每次采样时间约为100US

(3)、8通道模拟输入

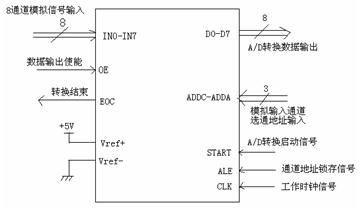

2、A/D转换器外部引脚功能结构图

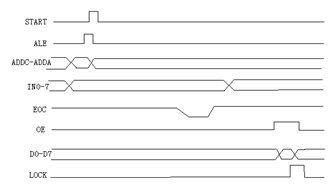

3、A/D转换器时序图

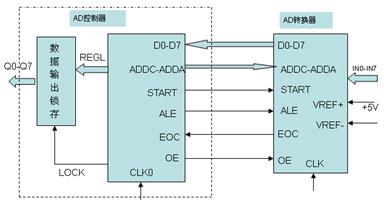

4、AD转换控制器与AD转换器的接口电路框图

5、状态控制

S0状态:初始状态。ADDC=‘1’,选择1通道模拟信号输入。

ALE=START=OE=LOCK=‘0’;

S1状态:通道锁存。ALE=‘1’, START=OE=LOCK=‘0’;

S2状态:启动A/D转换。 ALE=‘1’, START=‘1’,OE=LOCK=‘0’;

S3状态:A/D转换等待状态。

ALE=START=‘0’,OE=LOCK=‘0’;

IF EOC=‘0’ 保持当前状态不变,继续等待A/D转换。

ELSE 转换结束,进入下一状态。

S4状态:数据输出允许状态。A/D转换完毕,开启数据输出允许信号。

ALE=‘0’, START=‘0’,OE=‘1’,LOCK=‘0’;

S5状态:数据锁存状态。开启数据锁存信号,将转换结果送锁存器锁存。

ALE=‘0’, START=‘0’,OE=‘1’,LOCK=‘1’;

S6状态:延时状态。为了保证数据可靠锁存,延时一个时钟状态周期。

ALE=‘0’, START=‘0’,OE=‘1’,LOCK=‘1’;

其它状态:返回到初始状态。 ALE=START=OE=LOCK=‘0’;

6、参考程序:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY AD0809 IS

PORT (D :IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CLK0,EOC : IN STD_LOGIC; ADDA,OE : OUT STD_LOGIC;

ALE,START : OUT STD_LOGIC; Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

QQ : OUT INTEGER RANGE 15 DOWNTO 0);

END AD0809;

ARCHITECTURE behav OF AD0809 IS

TYPE ST_TYPE IS (S0, S1, S2, S3,S4,S5,S6,S7);

SIGNAL CURRENT_STATE,NEXT_STATE : ST_TYPE ;

SIGNAL REGL:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL LOCK :STD_LOGIC;

BEGIN

ADDA<='1';

PRO: PROCESS(CURRENT_STATE,EOC)

BEGIN

CASE CURRENT_STATE IS

WHEN S0 => QQ<=0;ALE<='0';START<='0';OE<='0';LOCK<='0'; NEXT_STATE <= S1;

WHEN S1 => QQ<=1;ALE<='0';START<='0';OE<='0';LOCK<='0'; NEXT_STATE <= S2;

WHEN S2 => QQ<=2;ALE<='1';START<='1';OE<='0';LOCK<='0'; NEXT_STATE <= S3;

WHEN S3 => QQ<=3;ALE<='1';START<='1';OE<='0';LOCK<='0';

IF EOC='0' THEN NEXT_STATE <= S4;

ELSE NEXT_STATE <= S3;

END IF;

WHEN S4 => QQ<=4;ALE<='0';START<='0';OE<='0';LOCK<='0';

IF EOC='1' THEN NEXT_STATE <= S5;

ELSE NEXT_STATE <= S4;

END IF;

WHEN S5 => QQ<=5;ALE<='0';START<='1';OE<='1';LOCK<='0'; NEXT_STATE <= S6;

WHEN S6 => QQ<=6;ALE<='0';START<='0';OE<='1';LOCK<='1'; NEXT_STATE <= S7;

WHEN S7 => QQ<=7;ALE<='0';START<='0';OE<='1';LOCK<='1'; NEXT_STATE <= S0;

WHEN OTHERS => NEXT_STATE <= S0;

END CASE;

END PROCESS PRO;

REG:PROCESS(CLK0)

BEGIN

IF CLK0'EVENT AND CLK0='1' THEN CURRENT_STATE<=NEXT_STATE;

END IF;

END PROCESS REG;

COM:PROCESS(LOCK)

BEGIN

IF LOCK'EVENT AND LOCK='1' THEN REGL<=D;

END IF;

END PROCESS COM;

Q<=REGL;

END behav;

实验八 数字频率计设计

一、实验目的及要求:

1、掌握VHDL语言的基本结构及编程思想。

2、掌握数字频率计的工作原理。

3、掌握数字频率计的VHDL语言编程方法。

二、实验内容:

1、设计8位十进制数字频率计。

2、测量频率范围为1Hz-50MHz

三、实验原理:

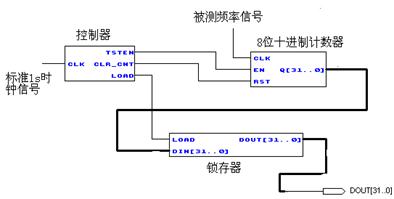

测频原理框图

四、实验步骤

1、8位十进制计数器设计

(1)用VHDL设计十进制计数器,并进行软件和硬件仿真

参考程序如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT (CLK,RST,EN : IN STD_LOGIC;

CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

COUT : OUT STD_LOGIC );

END CNT10;

ARCHITECTURE behav OF CNT10 IS

BEGIN

PROCESS(CLK, RST, EN)

VARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST = '1' THEN CQI := (OTHERS =>'0') ; --计数器复位

ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿

IF EN = '1' THEN --检测是否允许计数

IF CQI < "1001" THEN CQI := CQI + 1; --允许计数

ELSE CQI := (OTHERS =>'0');--大于9,计数值清零

END IF;

END IF;

END IF;

IF CQI = "1001" THEN COUT <= '1'; --计数大于9,输出进位信号

ELSE COUT <= '0';

END IF;

CQ <= CQI; --将计数值向端口输出

END PROCESS;

END behav;

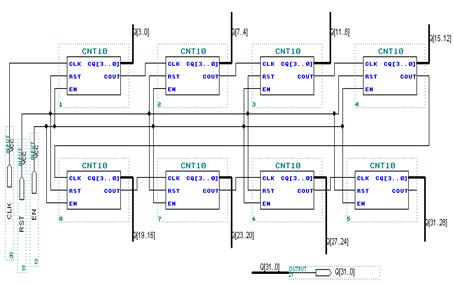

(2)8位十进制频率计电路图

2、32位锁存器设计

参考程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY reg32b IS

PORT (load : IN STD_LOGIC;

din: in STD_LOGIC_VECTOR(31 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END reg32b;

ARCHITECTURE behav OF reg32b IS

BEGIN

PROCESS(load,din)

BEGIN

IF load'EVENT AND load='1' THEN dout<=din; END IF;

END PROCESS;

END behav;

3控制器设计

(1)控制器时序图

(2)参考程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY testctl IS

PORT (clk : IN STD_LOGIC;

tsten:out STD_LOGIC;

clr_cnt: out STD_LOGIC;

load:out STD_LOGIC );

END testctl;

ARCHITECTURE behav OF testctl IS

signal div2clk:std_logic;

BEGIN

PROCESS(clk)

BEGIN

IF clk'EVENT AND clk='1' THEN div2clk<=not div2clk; END IF;

END PROCESS;

process(clk,div2clk)

begin

if clk='0' and div2clk='0' then clr_cnt<='1';

else clr_cnt<='0'; end if; end process;

load<=not div2clk; tsten<=div2clk;

END behav;

实验九 DAC接口电路与波形发生器设计

一、实验目的及要求:

1、掌握VHDL语言的基本结构及编程思想。

2、掌握DA转换器接口方法。

3、掌握DA转换器的VHDL语言编程方法。

二、实验内容:

1、设计一DAC0832数模转换器控制器。

2、要求使用DAC转换器输出一正弦波,最大值为5V。(使用单缓冲方式)

3、要求正弦波频率能步进可调,步进间隔为100Hz。(使用2个按键控制,一个步进为加,另一个为步进减)

三、实验原理

1、DAC0832特点

(1)、8位电流DAC转换,输出为电流信号,因此要转换为电压输出,必须外接集成运算放大器。。

(2)、转换时间约为50---500ns,转换速度比电压型DAC转换器快,电压型一般为1---10us

(3)、20脚双列直插式封装的CMOS型器件。

(4)、内部具有两极数据寄存器,可采用单或双缓冲方式。

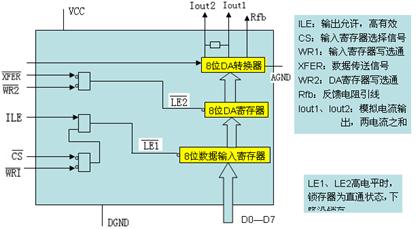

2、D/A转换器外部引脚功能及内部结构图

3、工作方式

方式一:直通工作方式(本实验采用此种方式)

一般用于只有一路输出信号的情况。

接线情况:ILE=1,CS=WR1=WR2 =XFER=0

方式二、双缓冲器工作方式

采用两步操作完成,可使DA转换输出前一数据的同时,将采集下一个数据送到8位输入寄存器,以提高转换速度。

一般用于多路DA输出。

4、DA转换器与控制器接口电路设计

5、实验仪实际接口电路图

6、DA转换器输出波形步进可调控制电路设计

设计思想:

设输入控制器的时钟频率为50MHz。

1、DA转换一次,需要一个时钟周期。若采用64点输出,则需要64个时钟周期。如果控制器时钟频率为64Hz,则输出的正弦波频率为1Hz。

2、因此,只需要控制DA转换控制器的时钟频率,则就可以控制正弦波频率,正弦波频率与时钟频率的关系为1:64。

3、题目要求正弦波步进频率为100Hz,则时钟频率步进应为6400Hz。按“加”键,则时钟频率增加6400Hz,按“减”减,时钟频率减小6400Hz。

7、带按键控制DA转换器与控制器接口电路设计

四、实验程序

参考程序:

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;

ENTITY DAC0832 IS

PORT (CLK :IN STD_LOGIC; DD : OUT INTEGER RANGE 255 DOWNTO 0);

END DAC0832;

ARCHITECTURE behav OF DAC0832 IS

SIGNAL Q:INTEGER RANGE 63 DOWNTO 0;SIGNAL D : INTEGER RANGE 255 DOWNTO 0;

BEGIN

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1' THEN Q<=Q+1; END IF; END PROCESS;

PROCESS(Q)

BEGIN

CASE Q IS

WHEN 00=>D<=254; WHEN 01=>D<=252; WHEN 02=>D<=249; WHEN 03=> D<=245;

WHEN 04=>D<=239; WHEN 05=>D<=233; WHEN 06=> D<=225; WHEN 07=> D<=217;

WHEN 08=>D<=207; WHEN 09=>D<=197; WHEN 10=> D<=186; WHEN 11=> D<=174;

WHEN 12=>D<=162; WHEN 13=>D<=150; WHEN 14=> D<=137; WHEN 15=> D<=124;

WHEN 16=>D<=112; WHEN 17=>D<=99; WHEN 18=> D<=87; WHEN 19=> D<=75;

WHEN 20=>D<=64; WHEN 21=>D<=53; WHEN 22=>D<=43; WHEN 23=> D<=34;

WHEN 24=>D<=26; WHEN 25=>D<=19; WHEN 26=> D<=13; WHEN 27=> D<=8;

WHEN 28=>D<=4; WHEN 29=>D<=1; WHEN 30=>D<=0; WHEN 31=> D<=0;

WHEN 32=>D<=1; WHEN 33=>D<=4; WHEN 34=> D<=8; WHEN 35=> D<=13;

WHEN 36=>D<=19; WHEN 37=>D<=26; WHEN 38=> D<=34; WHEN 39=> D<=43;

WHEN 40=>D<=53; WHEN 41=>D<=64; WHEN 42=> D<=75; WHEN 43=> D<=87;

WHEN 44=>D<=99; WHEN 45=>D<=112; WHEN 46=>D<=124; WHEN 47=> D<=137;

WHEN 48=>D<=150; WHEN 49=>D<=162; WHEN 50=> D<=255; WHEN 51=> D<=174;

WHEN 52=>D<=186; WHEN 53=>D<=197; WHEN 54=>D<=207; WHEN 55=> D<=217;

WHEN 56=>D<=225; WHEN 57=>D<=233; WHEN 58=> D<=239; WHEN 59=> D<=245;

WHEN 60=>D<=249; WHEN 61=> D<=252; WHEN 62=> D<=254; WHEN 63=>D<=255;

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

DD<=D; END;

实验十 七段显示器动态扫描电路设计(提高型)

实验目的及要求:

1、掌握VHDL语言的基本结构及编程思想。 2、掌握七段显示器动态扫描电路设计方法。

设计要求:

1、设计一个七段数码管动态扫描电路。

2、数码管个数为8个,共阴极接法。

3、设计BCD码--七段字符码的转换电路;

4、设计一电路,控制上述电路实现“12345678”八个数字的显示,要求显示方式为:

(1)自左至右逐个点亮数码管,最后全亮;再重复以上动作,每次变化时间间隔为1秒。

(2)自左至右点亮数码管,每次只点亮一个,最后全息灭,再重复以上动作,每次变化时间间隔为1秒。

(3) 先中间两个点亮,再依次向外点亮;全亮后,再依次向中间熄灭;重复上述步骤,每次变化时间间隔为1秒。

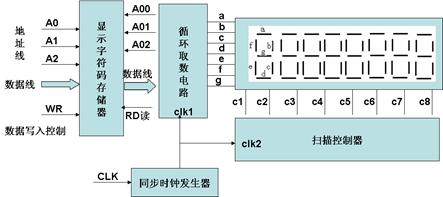

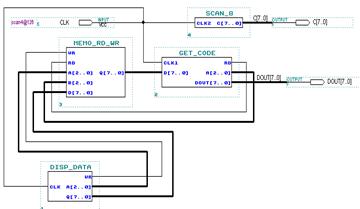

一、七段显示器动态扫描电路设计框图

二、存储器设计(8位8字节静态随机存储器SRAM)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY MEMO_RD_WR IS

PORT( WR,RD: IN STD_LOGIC;

A : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(2 DOWNTO 0);

D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

Q : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END MEMO_RD_WR;

ARCHITECTURE a OF MEMO_RD_WR IS

SIGNAL Q0,Q1,Q2,Q3: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL Q4,Q5,Q6,Q7: STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

PROCESS(WR,A)

BEGIN

IF WR='1' THEN

CASE A IS

WHEN "000"=>Q0<=D; WHEN "001"=> Q1<=D;

WHEN "010"=>Q2<=D; WHEN "011"=> Q3<=D;

WHEN "100"=>Q4<=D; WHEN "101"=> Q5<=D;

WHEN "110"=>Q6<=D; WHEN "111"=> Q7<=D;

WHEN OTHERS=>NULL;

END CASE; END IF; END PROCESS;

PROCESS(RD,B)

BEGIN

IF RD='1' THEN

CASE B IS

WHEN "000"=>Q<=Q0; WHEN "001"=> Q<=Q1;

WHEN "010"=>Q<=Q2; WHEN "011"=> Q<=Q3;

WHEN "100"=>Q<=Q4; WHEN "101"=> Q<=Q5;

WHEN "110"=>Q<=Q6; WHEN "111"=> Q<=Q7;

WHEN OTHERS=>NULL;

END CASE; END IF; END PROCESS;

END a;

四、循环取数电路设计

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY GET_CODE IS

PORT(CLK1: IN STD_LOGIC;

D : IN STD_LOGIC_VECTOR(7 DOWNTO 0);

RD:OUT STD_LOGIC;

A : OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

DOUT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END GET_CODE;

ARCHITECTURE a OF GET_CODE IS

SIGNAL LOAD: STD_LOGIC;

SIGNAL QQ : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL NUM: INTEGER RANGE 7 DOWNTO 0;

BEGIN

RD<=‘1’; LOAD<=CLK1;

PROCESS(CLK1)

BEGIN

IF CLK1'EVENT AND CLK1='1' THEN

IF NUM<=7 THEN NUM<=NUM+1;

ELSE NUM<=0; END IF; END IF;

END PROCESS;

PROCESS(NUM)

BEGIN

CASE NUM IS

WHEN 0 =>A<="000"; WHEN 1 =>A<="001"; WHEN 2 =>A<="010";

WHEN 3 =>A<="011"; WHEN 4 =>A<="100"; WHEN 5 =>A<="101";

WHEN 6 =>A<="110"; WHEN 7 =>A<="111"; WHEN OTHERS =>NULL;

END CASE;

END PROCESS;

PROCESS(LOAD)

BEGIN

IF LOAD‘EVENT AND LOAD=‘1’ THEN-------上升沿锁存

QQ<=D;

END IF;

END PROCESS;

DOUT(7 DOWNTO 0)<=QQ(7 DOWNTO 0);

END a;

五、扫描控制器设计

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY SCAN_8 IS

PORT(CLK2: IN STD_LOGIC;

C : OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END SCAN_8;

ARCHITECTURE a OF SCAN_8 IS

SIGNAL NUM: INTEGER RANGE 7 DOWNTO 0;

BEGIN

PROCESS(CLK2)

BEGIN

IF CLK2'EVENT AND CLK2=‘1' THEN

IF NUM<=7 THEN NUM<=NUM+1;

ELSE NUM<=0;

END IF; END IF;END PROCESS;

Process(num)

begin

CASE NUM IS

WHEN 1=>C<="11111110"; WHEN 2=> C<="11111101";

WHEN 3=>C<="11111011"; WHEN 4=> C<="11110111";

WHEN 5=>C<="11101111"; WHEN 6=> C<="11011111";

WHEN 7=>C<="10111111"; WHEN 0=> C<="01111111";

WHEN OTHERS=>NULL;

END CASE;

END PROCESS;

END A;

应用实例一:显示“01234567”八个数字

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY disp_data IS

PORT(CLK: IN STD_LOGIC;

WR:OUT STD_LOGIC;

A:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);

Q:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));

END disp_data;

ARCHITECTURE a OF disp_data IS

--SIGNAL QQ : STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL NUM: INTEGER RANGE 7 DOWNTO 0;

BEGIN

WR<=‘1’;

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1' THEN

IF NUM<=7 THEN NUM<=NUM+1;

ELSE NUM<=0; END IF; END IF;

END PROCESS;

PROCESS(NUM)

BEGIN

CASE NUM IS

WHEN 0 =>Q<="00111111";A<="000";

WHEN 1 =>Q<="00000110";A<="001";

WHEN 2 =>Q<="01011011";A<="010";

WHEN 3 =>Q<="01001111";A<="011";

WHEN 4 =>Q<="01100110";A<="100";

WHEN 5 =>Q<="01101101";A<="101";

WHEN 6 =>Q<="01111101"; A<="110";

WHEN 7 =>Q<="01111111"; A<="111";

WHEN OTHERS =>NULL;

END CASE; END PROCESS;END a;

实验十一 彩灯控制器设计(提高型实验)

实验目的及要求:

1、掌握VHDL语言的基本结构及编程思想。

2、掌握VHDL语言的进行系统设计的方法和步骤。

3、培养学生综合应用能力。

实验内容:

1、了解各类节日彩灯的显示方式(主要是动态方式)(上街观察);

2、将你所了解的情况,画出你的设计思想框图;

3、根据框图画出电路框图(用EDA技术);

4、用VHDL语言编程实现;

5、完成课程设计报告(约2000字)

实验十二、红绿交通灯控制系统

实验目的及要求:

1、掌握VHDL语言的基本结构及编程思想。

2、掌握VHDL语言的进行系统设计的方法和步骤。

3、培养学生综合应用能力。

实验内容:

设计一个简易十字路口交通灯控制器。

要求:

1、每个路口有红、绿、黄三个指示灯指示交通运行情况。红灯亮,禁止车辆通行;绿灯亮,车辆正常通行。

2、利用两位数码管显示通行到计时时间。

3、用VHDL语言编程实现;

4、完成课程设计报告

实验步骤:

1、红绿黄灯秒计数选择控制电路(traffic_mux)

SING_STATE:

00 绿灯20秒(横向路口); 01 黄灯5秒(横向路口)

10 绿灯20秒(直向路口) 11 黄灯5秒(直向路口)

RECOUNT:重新计数信号。 =‘1’,发送倒计时时间数据; =‘0’,正常倒计时;

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_unsigned.all;

USE IEEE.std_logic_arith.all;

entity traffic_mux is

port(reset,clk_1Hz,recount: in std_logic;

sign_state: in std_logic_vector(1 downto 0);

load: out integer range 255 downto 0);

end;

begin

process(reset,clk_1s)

begin

if reset='1' then load<="00000000";

elsif (clk_1Hz'event and clk_1Hz='1') then

if recount = '1‘ then

CASE sign_state IS

WHEN "00" => load <= 20;

WHEN "01" => load <= 5; WHEN "10" => load <= 20;

WHEN "01" => load <= 5; WHEN OTHERS =>null;

END CASE;

end if; end if; end process;end BEHAVIOR;

2、倒计时控制电路(count_down)

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

use IEEE.std_logic_unsigned.all;

entity count_down is

port(reset,clk_1Hz: in std_logic;

recount:in std_logic;

load: in integer range 255 downto 0;

seg7:out std_logic_vector(15 downto 0);

next_state: out std_logic);

end;

architecture BEHAVIOR of count_down is

signal cnt_ff: integer range 255 downto 0;

begin

process(clk_1Hz,reset)

begin

if (reset='1') then cnt_ff<="00000000"; seg7<="0000000000000000";

elsif (clk_1Hz'event and clk_1Hz='1') then

if recount='1‘ then cnt_ff<=load-1;

else cnt_ff<=cnt_ff-1;

end if; end if; end process;

process(cnt_ff)

begin

case cnt_ff is

when 0=>seg7<="0011111100111111"; when 1=>seg7<="0011111100000110";

when 2=> seg7<="0011111101011011"; when 3=> seg7<="0011111101001111";

when 4=> seg7<="0011111101100110"; when 5=> seg7<="0011111101101101";

when 6=> seg7<="0011111101111101"; when 7=> seg7<="0011111100000111";

when 8=> seg7<="0011111101111111"; when 9=> seg7<="0011111101111011";

when 10=> seg7<="0000011000111111"; when 11=> seg7<="0000011000000110";

when 12=> seg7<="0000011001011011"; when 13=> seg7<="0000011001001111";

when 14=> seg7<="0000011001100110"; when 15=> seg7<="0000011001101101";

when 16=> seg7<="0000011001111101"; when 17=> seg7<="0000011000000111";

when 18=> seg7<="0000011001111111"; when 19=> seg7<="0000011001111011";

when 20=> seg7<="0101101100111111"; when 21=> seg7<="0101101100000110";

when 22=> seg7<="0101101101011011"; when 23=> seg7<="0101101101001111";

when 24=> seg7<="0101101101100110"; when 25=> seg7<="0101101101101101";

when 26=> seg7<="0101101101111101"; when 27=> seg7<="0101101100000111";

when 28=> seg7<="0101101101111111"; when 29=> seg7<="0101101101111011";

when others=> seg7<="0011111100111111";

end case; end process;

next_state <= '1' when cnt_ff=1 else '0';

end BEHAVIOR;

3、红绿灯信号控制电路(traffic_fsm)

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

USE IEEE.std_logic_arith.all;

USE IEEE.std_logic_unsigned.all;

entity traffic_FSM is

port(reset,clk,clk_1Hz,flash_1Hz: in std_logic;

a_m:in std_logic;

next_state: in std_logic;

recount: out std_logic;

sign_state: out std_logic_vector(1 downto 0);

red: out std_logic_vector(1 downto 0);

green: out std_logic_vector(1 downto 0);

yellow: out std_logic_vector(1 downto 0));

end;

architecture BEHAVIOR of traffic_FSM is

type Sreg0_type is (r0g1, r0y1, g0r1, y0r1, y0y1, y0g1, g0y1, r0r1);

signal state : Sreg0_type;

signal light: std_logic_vector(5 downto 0);

begin

if (reset='1') then

state<=r0g1; ----设定当前为横向红灯亮,竖向绿灯亮

sign_state<=“01”;------选择20秒倒计时

recount<=‘1’; ------装入计数初值并启动倒计时

else

if (clk'event and clk='1') then

case STATE is

when r0g1 => if (a_m='1' and clk_1Hz='1') then

if (next_state = ‘1’) then --当前计数完毕,转入下一种计时

recount<='1'; state<=r0y1; sign_state <= "01";

else recount<=‘0’; state<=r0g1;----否则,继续倒计时

end if;

when r0y1 => -- now state: red0 on yellow1 flash

if (a_m='1' and clk_1Hz='1') then

if (next_state = '1') then

recount<='1'; state<=g0r1; sign_state <= "10";

else recount<='0'; state<=r0y1; end if;

when g0r1 => -- now state: green0 on red1 on

if (a_m='1' and ena_1Hz='1') then

if (next_state = '1') then recount<='1'; state<=y0r1;

sign_state <= "11";

else recount<='0'; state<=g0r1; end if;

when y0r1 => -- now state: green0 on red1 on

if (a_m='1' and ena_1Hz='1') then

if (next_state = '1') then recount<='1'; state<=r0g1; sign_state <= "00";

else recount<='0';

state<=y0r1; -- red=2'b10; green=2'b00; yellow=2'b01;

end if;

when others => state<=r0g1; recount<='0'; sign_state <= "00";

end case;

end if; end if; end process;

-- light: r(10)y(10)g(10)

light <= "010010" when (state=r0g1) else

"011000" when (state=r0y1) else

"100001" when (state=g0r1) else

"100100" when (state=y0r1) else

"110000";

red <= light(5 downto 4);

yellow <= light(3 downto 2) and (flash_1Hz & flash_1Hz);

green <= light(1 downto 0);

end BEHAVIOR;