基于MATLAB的数字频率合成DDS设计

一、实验目的:

1:理解数字频率合成DDS的原理。

2:掌握DDS的设计方法与理念。

3:学会用MALTLAB对DDS进行程序实现。

二、实验背景:

随着技术和器件水平的提高,称之为直接数字式频率合成器(DDS)新的频率合成技术得到飞速的发展。 DDS 在相对带宽、频率转换时间、相位连续性、正交输出、高分辨力以及集成化等一系列指标方面,已远远超过了传统频率合成器所能达到的水平,完成了频率合成技术的又一次飞跃。DDS 与传统的 DS 和 IS 一起构成了现代频率合成技术体系,将频率合成技术推向了一个新阶段。

三、实验原理:

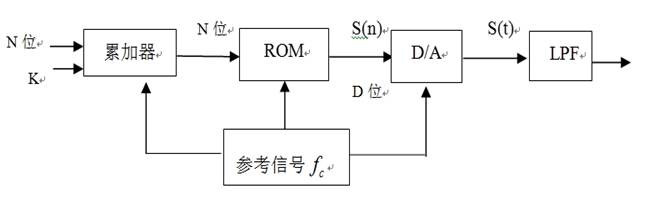

数字频率合成是从相位概念出发直接合成所需波形的一种新技术,它采用一个恒定的输入参考时钟,通过数据处理的方式产生频率、相位可调的输出信号。DDS系统由相位累加器、波形ROM、D/A转换器和低通滤波器构成。它具有频率分辨率高、频率切换速度快、频率切换时相位连续等优点。

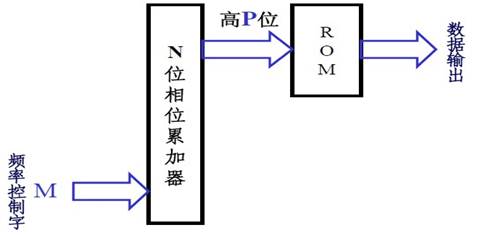

DDS是继直接频率合成技术和锁相环式频率合成技术之后的第三代频率合成技术。它的工作原理是基于相位与幅度的对应关系,通过改变频率控制字(K)来改变相位累加器(位数为N)的相位累加速度,然后在固定时钟的控制下取样,取样得到的相位值(去取相位累加器的高M位)通过相位幅度转换得到与相位值对应的幅度序列,幅度序列通过数模转换及低通滤波得到正弦波输出。下图为DDS的原理图。

图(1) 原理框图

其中,K为频率控制字, 为基准时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在基准时钟fc的控制下以步长K做累加,把相加后的结果送至相位累加器的输入断,相位累加器一方面将在上一时钟周期作用后产生的新的相位数据反馈到自身的输入端,在下一个时钟的作用下继续与频率控制数据K相加,另一方面将这个值作为取样地址输出,送人正弦查找表ROM,作为波形ROM的地址,对波形ROM进行寻址。波形ROM输出D位的幅度码S(n)经D/A转换器变成阶梯波S(t),再经过低通滤波器平滑后就可以得到合成的信号波形。合成的信号波形取决于波形ROM中存放的幅度码,因此用DDS可以产生任意波形。

为基准时钟频率,N为相位累加器的字长,D为ROM数据位及D/A转换器的字长。相位累加器在基准时钟fc的控制下以步长K做累加,把相加后的结果送至相位累加器的输入断,相位累加器一方面将在上一时钟周期作用后产生的新的相位数据反馈到自身的输入端,在下一个时钟的作用下继续与频率控制数据K相加,另一方面将这个值作为取样地址输出,送人正弦查找表ROM,作为波形ROM的地址,对波形ROM进行寻址。波形ROM输出D位的幅度码S(n)经D/A转换器变成阶梯波S(t),再经过低通滤波器平滑后就可以得到合成的信号波形。合成的信号波形取决于波形ROM中存放的幅度码,因此用DDS可以产生任意波形。

(1)频率预置与调节

K被称为频率控制字,也叫相位增量。DDS方程为f0=fC K/2N,f0为输出频率,fc为时钟频率。当K=1时,DDS输出最低频率(也即频率分辨率)为fC/2N,而DDS的最大输出频率由Nyquist采样定理决定,即fc/2,也就是说K的最大值为2N-1。因此只要N足够大,DDS可以得到很细的频率间隔。要改变DDS的输出频率,只要改变频率控制字K即可。

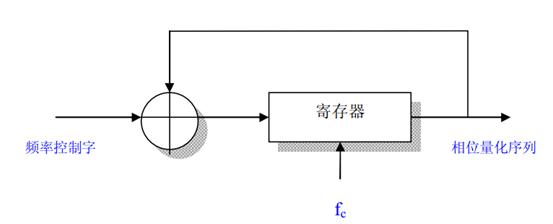

(2)累加器

图(2) 累加器框图

相位累加器由N位加法器和N位寄存器级联构成,来一个时钟脉冲fc,加法器将频率控制字K与寄存器输出的累加相位相加,再将相加后的结果送入寄存器的数据输入端。寄存器将加法器在上一个时钟作用后所产生的相位数据反馈到加法器的输入端,使加法器在下一个时钟作用下继续与频率控制字进行相加。这样,相位累加器在时钟的作用下进行相位累加。当相位累加器加满时产生一次溢出,完成一个周期性的动作。

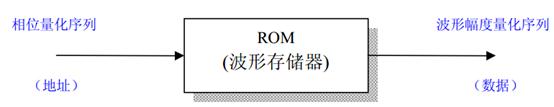

(3)波形存储器

用累加器输出的数据作为波形存储器的取样地址,进行波形的相位—幅值转化,即可在给定的时间上确定波形的抽样幅值。N位的寻址ROM相当于把0O~360O的正弦信号离散成具有2N个样值的序列,若波形ROM有D位数据,则2N个样值的幅值以D为二进制数值固化在ROM中,按照地址的不同可以输出相应正弦信号的幅值。

相位—幅度变化原理图如下所示:

图(3) 相位—幅度变化原理图

(4)D/A转换器

D/A转换器的作用是把合成的正弦波数字量转换为模拟量。正弦幅度量化序列S(n)经过D/A转换后变成了包络为正弦波的阶梯波S(t)。需要注意的是频率合成器对D/A转换器的分辨率有一定要求,D/A转换器的分辨率越高,合成的正弦波S(t)台阶数就越多,输出波形的精度也就越高。

(5)低通滤波器

对D/A输出阶梯波S(t)进行频谱分析,可知S(t)中除主频f0外,还存在分布在fc,2fc ......两边±f0处的非谐波分量,幅值包络为辛格函数。因此为了取出主频f0,必须在D/A转换器的输出端接入截止频率为fc/2的低通滤波器。

四、DDS性能:

DDS的频率合成原理及实现技术与传统的直接合成DS和锁相合成完全不同,在性能上也很独特。

1. 相对带宽

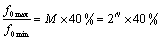

当频率控制字K=1时,最低输出频率为fomax=fc/M,式中M = 2N,当累加器字长 N 很大时,最低输出频率达 Hz、mHz 量级都是不困难的,可认为DDS的最低合成频率接近于零频。

DDS的最高输出频率受限于时钟频率fc和采样定理,fomax= fc。

fc。

在实际应用中,考虑到输出滤波器的非理想特性,一般采用 fomax= fc×40%。

这样DDS的相对带宽为

这样DDS的相对带宽为

2.频率分辨率

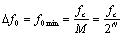

DDS的最小频率步进量就是它的最低输出频率,即

DDS的最小频率步进量就是它的最低输出频率,即

也可以采用十进制的相位累加器,那么M = 10N。可见只要累加器有足够的字长,实现非常精密的分辨率也没有多大的困难,正像全面介绍的一样,可达 Hz、mHz、甚至μHz 的频率步进量。是传统频率合成技术所无可达到的。

3.频率转换时间

DDS的频率转换时间近似认为是即时的,这是因为它的相位序列在时间上是离散的。在频率控制字 K 改变以后,要经一个时钟周期之后才能按新的相位增量累加,所以可以说它的频率转换时间就是频率控制字的传输时间,即一个时钟周期Tc=1/fc。目前,集成DDS产品的频率转换时间可达10ns的量级。这是常用锁相频率合成所无法达到的。

4. 频率转换时的相位连续性

当频率控制字从K1变为K2之后,它是在已有的累加相位nK1δ之上,再每次累加K2δ,相位函数的曲线是连续的,只是在改变频率瞬间其斜率发生了突变,因而保持了输出信号相位的连续性。这一点对利用相位信息的那些系统很重要。

相位连续可避免信息的丢失,相位不连续回导致频谱的扩散,不利于频谱资源的有效利用。

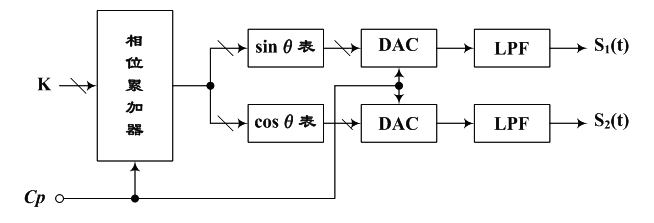

5. 可输出正交信号

有些应用场合要用到正交信号输出,即同时输出s1(t)= sin (2πf0t)和s2(t) = cos (2πf0t)

在DDS中,只要分别在两个ROM中存储sinθ和 cosθ两个函数表,即可同时输出正交信号,实现框图如 3-14 所示。

图(4) 可输出正交信号的DDS框图

6. 可输出任意波形

若在ROM中存储其它所需的波形函数表,DDS即可输出相应的周期性的波形,因此,更新ROM中的数据,使DDS输出方波、三角波、锯齿波等等。

7. 调制性能

由于DDS是全数字的,用频率控制字K可直接调整输出信号的频率与相位,所以很易于在DDS上实现数字调频和调相,很多DDS产品都具有数字调制功能。

8. 噪声与杂散

因为DDS是数字技术,先构成离散信号,再变换成模拟信号输出,因而噪声与杂散的存在是必然的。这是我们要特别关注的。

五、Matlab程序

function [y,t]=DDS(N,K,Fs,Nd,fai)

%输入:

% N 相位累加器字长

% K 频率控制字

% Fs 采样频率

% Nd 输出信号的点的数目

% fai 输出信号的初始相位

%输出:

% y 输出信号的波形

% t 输出信号时间

M= 2^N;

n=0:Nd-1;

y = sin(2*pi*n*K/M+fai); %产生离散信号

y = y/max(y); %对信号幅值进行归一化

%此时的相位增量为2*pi*K/

Ts = 1/Fs; %采样频率

t = (0:Nd-1)*Ts; %根据需要输出的信号点数,取得时间

plot(t,y);

xlabel('t/s'); %X轴标注坐标

ylabel('A'); %Y轴标注坐标

title('时域图'); %添加标题

grid on; %显示格点

Fy= abs(fft(y,4*Nd)); %对信号做傅里叶变换

Len_Fy = length(Fy); %此处的数字角频率

f = (0:Len_Fy)/Len_Fy*Fs; %输出信号频率,将数字频率转换成模拟频率(w=2*pi*f/fs)

count = floor(Len_Fy/2); %频谱显示的点数

figure %显示多幅图像

plot(f(1:count),Fy(1:count));

grid on;

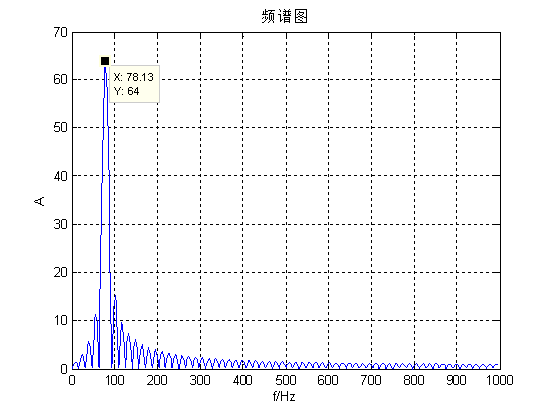

xlabel('f/Hz');ylabel('A');title('频谱图');

六、实验仿真波形:

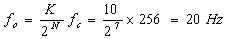

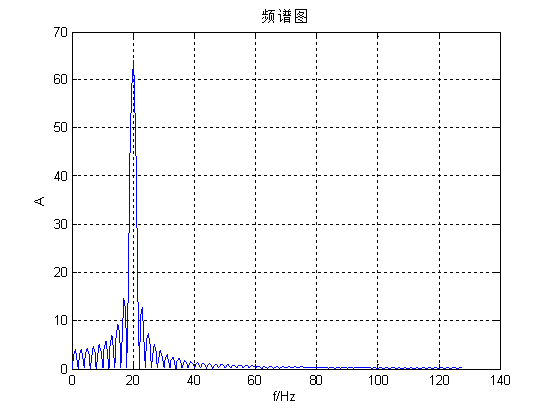

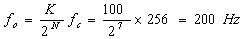

1、如果采样频率设置为256Hz,累加字长N为7位,K控制字长为10,那么输出信号的频率是 ,显示的点数设置为128,初始相位为0,实验结果如下图所示

,显示的点数设置为128,初始相位为0,实验结果如下图所示

图(5) 20Hz时域图

图(6) 20Hz频域图

上图的Matlab调用格式:

>> [y,t]=DDS(7,10,256,128,0);

由图(6)可以看出,实际得到的图形输出信号频率与理论计算相符合,说明了设计是正确的。

上图中的采样频率为256Hz,相位累加器字长为7,频率分辨率为1Hz,相位累加字长越长,其频率分辨率越高。

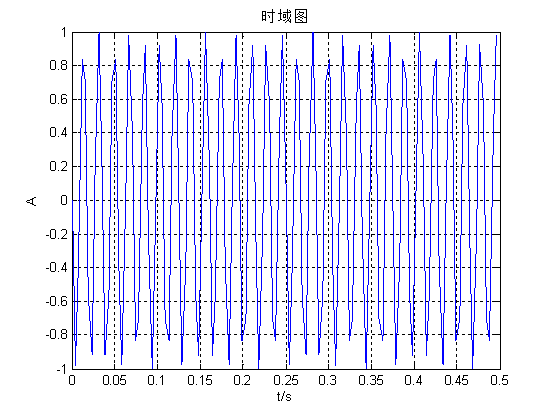

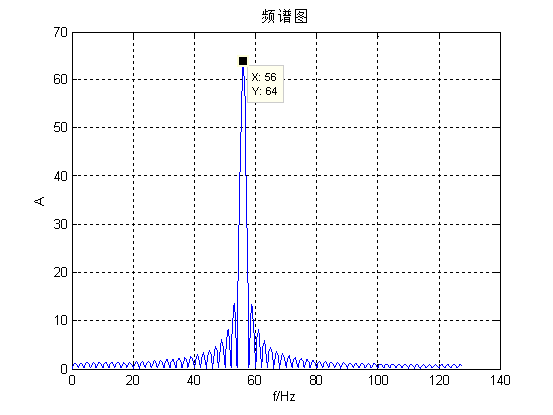

2、如果采样频率设置为256Hz,累加字长N为7位,K控制字长为100,那么输出信号的频率是 ,显示的点数设置为128,初始相位为0。

,显示的点数设置为128,初始相位为0。

Matlab调用格式:

>> [y,t]=DDS(7,100,256,128,0);

实验结果如下图所示

由图(8)知,产生的频率错了,输出产生了56Hz的频率。这是由于信号的输出频率必须大于等于两倍的采样频率(奈奎斯特定理知)。我们设置输出信号频率200Hz,而采样频率只有256Hz,不符合奈奎斯特采样定律,所以输出的频域图上的频率出现了错误。

图(7) 200Hz时域图

图(8) 200Hz频域图

3、如果想要得到一个1KHz的,初始相位是 的正弦波,那么其采样频率一定要大于2KHz在这取16KHz,相位累加器字长为8,

的正弦波,那么其采样频率一定要大于2KHz在这取16KHz,相位累加器字长为8,

Matlab调用程序:

>> [y,t]=DDS(8,32,16000,128,pi/4);

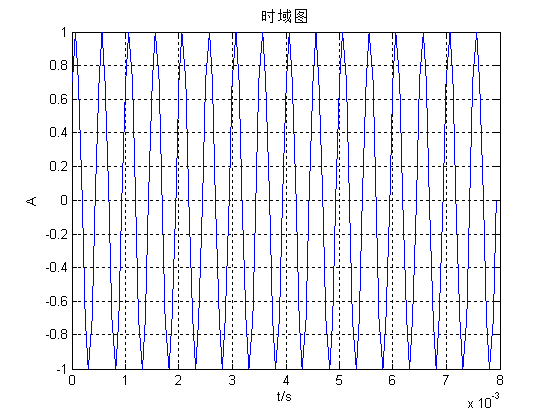

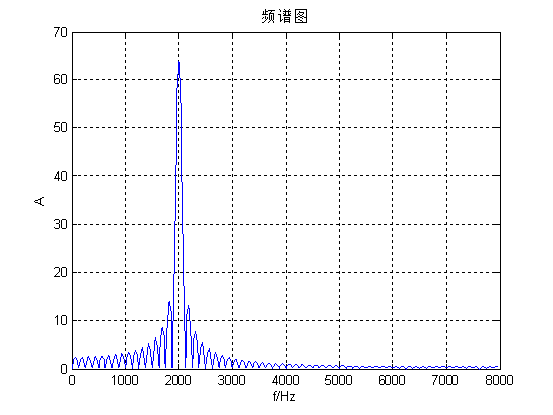

图(9)2KHz时域图

图(10) 2KHz频域图

由图(10)可知,系统正确的实现了所想的设计。

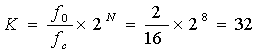

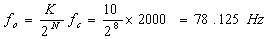

4、如果采样频率设置为2KHz,累加字长N为8位,K控制字长为10,那么输出信号的频率是 ,显示的点数设置为128,初始相位为

,显示的点数设置为128,初始相位为 。

。

Matlab调用格式:

>> [y,t]=DDS(8,10,2000,128,pi/2);

实验结果如下图所示

图(11) 78.125Hz时域图

图(12) 78.125Hz频域图

由图(12)知,当所要产生的不是整数时,该系统也能正确的输出所要的频率。

综上所述,此系统设计的很成功,可以很好地满足数字频率合成DDS的设计要求。

七、总结

本次的课程设计我个人觉得是很有意义的。老师给的每一个题目都很有代表性,而且实用性很强。这次课程设计学到的东西很多,它把我这期所学的知识系统的规划起来并用于实践的操作,这也是对理论知识深刻认识的最重要一步,让我受益匪浅。

首先,拿到一个题目,知道如何去分析它,建立设计思想,可以通过系统划分,设计输入、逻辑设计综合,再编译仿真这几个步骤进行。其次,也熟悉了Maltlab的使用和编程,对DDS有了很深的理解。

通过初次设计DDS程序,我学到了很多以前从未学到的知识,对数字频率合成也有了更深的了解,也终于知道了,要想做一个有用的东西出来不是那么容易的事情,但是我会尽可能的去学、去弄,我想只要不停止的去弄这个应该能学习到新东西。

第二篇:实验二 DDS波形发生器设计实验报告

实验二 DDS波形发生器设计实验报告

一.实验任务及要求

任务:利用FPGA+DAC,设计一个DDS信号发生器。

要求:(1)分辨率优于1Hz

(2)ROM表长度8位、位宽10位

(3)输出频率优于100kHz(每周期大于50个点)

(4)显示信号频率/频率控制字

二.实验设计方案

用CPLD,FPGA实现DDS波形发生器设计

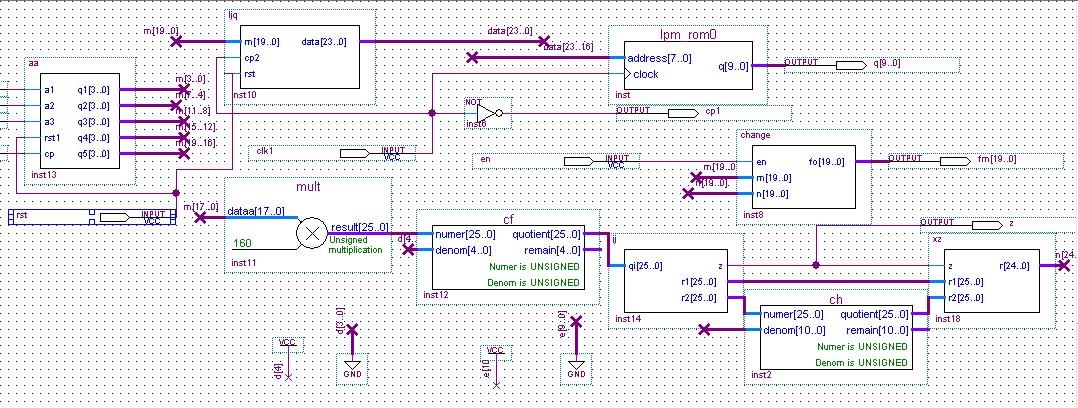

⑴用QuartusII的原理图输入来完成系统的顶层设计。

⑵相位累加器调用用HDL编写。

⑶波形存储器通过调用lpm_rom元件实现,其LPM_FILE的值*.mif是一个存放波形幅值的文件。

⑷频率-频率控制字之间的转换,可用乘、除法模块(LPM)设计以及用VHDL语言编写。

其具体实现方案如下原理图

输出频率:(1) 通过时钟频率, 改变输出波形的频率

(2) 改变寻址的步长来改变输出信号的频率—DDS

设:相位累加器为N位, Sin表的大小为2P,累加器的高P位用于寻址Sin表.时钟频率为fC,若累加器按步进为M地累加直至溢出,称M为频率控制字。

三.系统硬件设计

1)DDS参数计算

①相位寄存器每经过2N/M个时钟fc后回到初始状态,相应地正弦查询表经过一个循环回到初始位置,整个DDS系统输出一个正弦波。

则 输出正弦波周期 To=Tc*2n/M

即 输出正弦波频率 fout=M×fc/2n

②要求分辨率优于1Hz 则fc/2n<1

③输出频率优于100kHz(每周期大于50个点)

则fout=M×fc/2n >100KH

2n/M>50

由②、③可得 输入频率fc>5MHZ,在实验中我们设脉冲频率为10MHZ。

2)在实验中采用24位相位累加器(即n=24),用VHDL创建功能模块。

原理:通过频率控制字控制相位累加,直至溢出,取其高8位作为查询sin表的地址,从而控制输出的波形。

3)频率控制字M的设置,用VHDL创建功能模块aa

设置a1,a2,a3三个输入端,其不同的输入组合对应控制频率控制字M的各个位,确定控制位后,通过输入单脉冲控制其大小,直到输入所需控制字,同时设置了复位端rst1。

4)LPM_ROM模块功能及原理

通过公式1023/2*[sin(2*3.14*A/256)+1]制作sin表,设置长度8位、位宽10位。波形存储器通过调用lpm_rom元件实现,其LPM_FILE的值*.mif是制作的sin表文件。

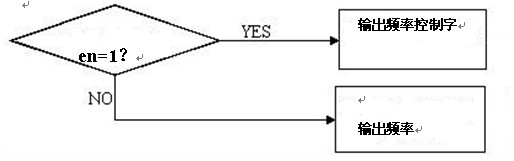

5) 输出频率-频率控制字之间的转换, 用VHDL创建功能模块chang。

通过设置使能端en,控制输出频率与频率控制字之间的显示转换。

6)输出频率显示设置,采用乘、除法模块(LPM)设计以及用VHDL语言编写。

其中通过编写VHDL,设置其输出单位,创建功能模块ij和xz。当LED1灯亮时则输出单位为KHZ,否则为HZ。并且通过乘除法的转换输出使数码管最后一位显示的为小数位。因为数码管为16进制显示所以在设置输出时,把fout=M×fc/2n之后乘以16,这样在数码管上显示的最后一位即为小数位。

7)具体电路原理图见附录1

四.系统软件设计

1)部分功能模块流程图

①相位累加器(ljq)流程图

②输出频率-频率控制字转换(chang)流程图

2)具体程序清单见附录2

五.系统测试

1)电路的测试方案

通过参数的计算公式fout=M×fc/2n,控制M的大小,测出输出频率并与理论数据相比较。

2)电路测试结果

通过调试得到完整稳定的波形图

①当输入控制字M大小为28F14H(十进制167700)时,经理论计算得输出频率为100KHZ;示波器中显示输出频率为99.9578KHZ;此时实验箱中LED1灯变亮,数据显示为665,因为数码管最后一位显示为小数,则显示输出数据应为(66.5H)KHZ,转换为10进制即102.03125KHZ.

②当输入控制字M大小为68DH(十进制1677)时,经理论计算得输出频率为1KHZ;示波器中显示输出频率为999.578HZ;此时实验箱中LED1灯未变亮,数据显示为10,同上,则显示输出数据应为(1.0H)KHZ,转换为10进制即1KHZ.

③当输入控制字M大小为10400H(十进制66560)时,经理论计算得输出频率为1KHZ;示波器中显示输出频率为999.578HZ;此时实验箱中LED1灯未变亮,数据显示为10,同上,则显示输出数据应为(1.0H)KHZ,转换为10进制即1KHZ.

④当输入控制字M大小为1H(十进制1)时,经理论计算得输出频率为596mHZ;示波器中显示输出频率为599.3mHZ;此时实验箱中LED1灯未变亮,数据显示为0,同上,则显示输出数据应为0HZ,最小输出频率。

⑤当输入控制字M大小为FFFFFH, 经理论计算得输出频率为625KHZ;示波器中显示输出频率为625.004KHZ;此时实验箱中LED1灯未变亮,数据显示为2712,同上,则显示输出数据应为(271.2H)KHZ, 转换为10进制即625.125KHZ.即为最大书出频率。

六.实验结论

由电路测试数据可知,测试结果与理论数据几乎相等,则实验设计正确。在实验过程中,在对小数进行处理时出现了一些问题,为了在数码管中显示出一位小数点,即显示的数据向左移动一位,刚开始直接在数据输出显示fout=M×fc/2n之后乘以10,忘了数码管显示为16进制,从而导致了数据显示结果总是与理论相差很多。

通过这次实验,我们对数字系统设计的方法有了更进一步的掌握。

附录1

附录2

程序清单

1.控制字M的设置

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity aa is

port(a1,a2,a3,rst1:in bit;

q1,q2,q3,q4,q5:buffer unsigned(3 downto 0);

cp:in bit);

end aa;

architecture rtl of aa is

signal tmp_in:bit_vector(2 downto 0);

begin

tmp_in<=a3&a2&a1;

process(cp,tmp_in,rst1)

begin

if rst1='1' then q1<="0000";q2<="0000";q3<="0000";q4<="0000";q5<="0000";

elsif cp 'event and cp='1'then

if tmp_in="001" then q1<=q1+1;

elsif tmp_in="010" then q2<=q2+1;

elsif tmp_in="011" then q3<=q3+1;

elsif tmp_in="100" then q4<=q4+1;

elsif tmp_in="101" then q5<=q5+1;

end if;

end if;

end process;

end rtl;

2.累加器ljq

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity ljq is

port(m:in unsigned(19 downto 0);

cp2,rst:in bit;

data:out unsigned(23 downto 0));

end ljq;

architecture atl of ljq is

signal iq:unsigned(23 downto 0);

begin

process (m,cp2,rst,iq)

begin

if rst='1' then iq<="000000000000000000000000";

elsif(cp2 'event and cp2='1')then

iq<=iq+m;

end if;

data<=iq;

end process;

end atl;

3输出频率显示设置 ij和xz

Ij:library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity jj is

port(qi:in unsigned(25 downto 0);

z:out bit;

r1,r2:out unsigned(25 downto 0));

end jj;

architecture rl of jj is

begin

process(qi)

begin

if qi<10000 then r1<=qi;

else r2<=qi;z<='1';

end if;

end process;

end rl;

xz:library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity xz is

port(z:in bit;

r1,r2:in unsigned(25 downto 0);

r:out unsigned(24 downto 0)) ;

end xz;

architecture t of xz is

begin

process(z,r1,r2)

begin

if z='1' then r<=r2(24 downto 0);

else r<=r1(24 downto 0);

end if;

end process;

end t;

4 输出频率与频率控制字的转换

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

entity change is

port(en:in bit;

m:in unsigned(19 downto 0);

n:in unsigned(19 downto 0);

fo:out unsigned(19 downto 0));

end change;

architecture qie of change is

begin

process (en)

begin

if en='1' then

fo<=m;

else fo<=n;

end if;

end process;

end qie;