科 技 学 院

课程设计实验报告

( 20##--20##年度第一学期)

名 称: 计算机组成原理综合实验

题 目: 运算器实验

院 系: 信息工程系

班 级:

学 号:

学生姓名:

指导教师: 李梅 王晓霞

设计周数: 一周

成 绩:

日期: 2015 年 1 月

一、目的与要求

(1) 熟悉与深入理解4位的运算器芯片Am2901的功能和内部组成,运行中要求使用的控制信号及其各自的控制作用;

(2) 熟悉与深入理解用4片4位的运算器芯片构成16位的运算器部件的具体方案,各数据位信号、各控制位信号的连接关系;

(3) 熟悉与深入理解用2片GAL20V8芯片解决ALU最低位的进位输入信号和最高、最低位的移位输入信号、实现4位的标志位寄存器的方案,理解为什么这些功能不能在运算器芯片之内实现而要到芯片之外另外处理。

(4) 明确教学计算机的运算器部件,使用总计23位的控制信号就完全确定了它的全部运算与处理功能,脱机运算器实验中可以通过24位的微型开关中的23位提供这些控制信号,教学计算机正常执行指令时,这些控制信号必须改由控制器部件来提供。在两种方式下,每一位(组)的控制功能是完全相同的。

二、实验正文

1. 实验内容

1.1 脱机运算器和联机运算器的区别和联系

运算器是计算机硬件系统传统的5大功能部件之一,承担执行运算和暂存运算。

数据的功能,通常由执行算术逻辑运算功能的ALU线路。暂存参加ALU运算的数据和中间运算结果的通用寄存器组、支持乘法运算的专用寄存器三部分组成,三部分之间通过多线路选择器线路实现连接,从而构成一个完整的运算器部件。

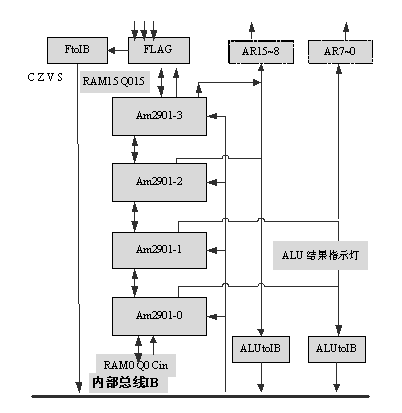

TEC-XP16教学计算机的运算器部件,主体部分由4片4位长度的位片结构的运算器芯片Am2901组成,每片Am2901可以接收来自内部总线IB的4位输入数据,其4为输出直接送到地址寄存器AR的不同字段,并且经过支持三态功能的开关门电路送到内部总线IB。还要使用MACH芯片内部的部分电路提供ALU最低位的进位输入信号和最高、最低的移位输入信号,使用一片GAL20V8实现4位的标志位寄存器FLAG,接收ALU输出的4个标志位信号和来自内存堆栈区的4位数据(用于恢复现场状态信息),FLAG的4位输出可以经过一片带支持三态功能的开关门电路送到内部总线IB,用于保存现场状态信息到堆栈区。教学机运算器部件的组成线路和信息连接关系如图2.1所示。

图2.1 运算器组成线路和信息连接关系

运算器部件的教学实验,要在教学计算机主板上进行,既可以在脱机方式下完成,也可以在联机方式下完成。

脱机运算器实验方式是指使运算器部件完全脱离与计算机主机其他部件正常的连接关系,在完全孤立出来的运算器上进行的教学实验。此时,只能通过数据开关拨入参加运算的数据,通过微型开关提供操作运算器运行所必需的控制信号,通过信号指示灯观察运算结果,操作简单,实验结果清晰易理解。图2. 2为16位运算器脱机实验的环境,在计原16系统中,运算器最低位的进位输入信号Cin和左右移位输入信号RAM0、Q0、RAM15、Q15是由MACH芯片内部的SHIFT线路提供的,图左侧的长方形部分是MACH内部的线路。16个开关拨入的数据经开关门电路送到内部总线,内部总线与运算器的输入端D15~D0已经连接。23位的微型开关的不同组合完成不同的控制,其各编码对应的控制功能给出在表2-1。

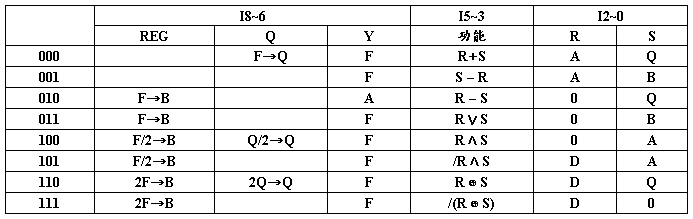

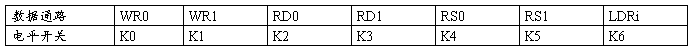

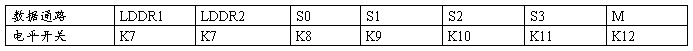

1.2 脱机运算器实验微型开关各字段的控制功能

1.3 脱机运算器实验

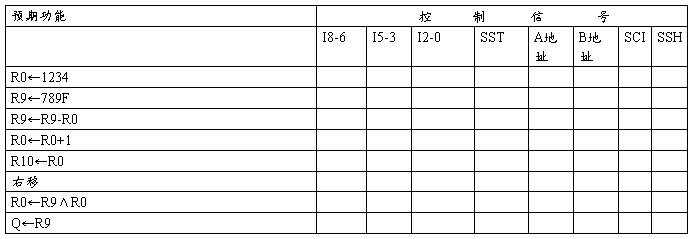

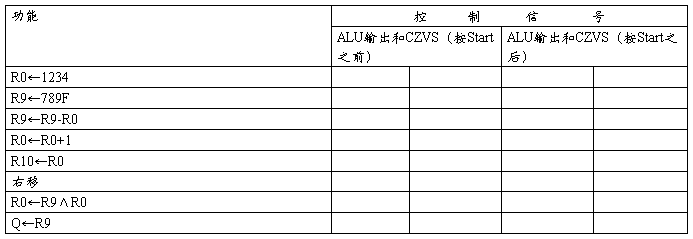

1根据预期要完成的运算设计实现方案,依据教学计算机的简明操作卡中的有关表格中的规定内容,找出实现每一操作功能要用到的控制码。请把下表中各种控制信号的正确取值填写在相应位置。

表 1

将上述七项运算的执行结果填进下表。

表2

还是采用脱机运算器的方法,完成表3。

表3

1.4 联机方式

三、综合实验总结

1. 实验难点

2. 心得体会

第二篇:计算机组成原理 实验一 运算器组成实验

实验一 运算器组成实验

一、实验目的

1.熟悉双端口通用寄存器堆的读写操作。

2.熟悉简单运算器的数据传送通路。

3.验证运算器74LS181的算术逻辑功能。

4.按给定数据,完成指定的算术、逻辑运算。

二、实验电路

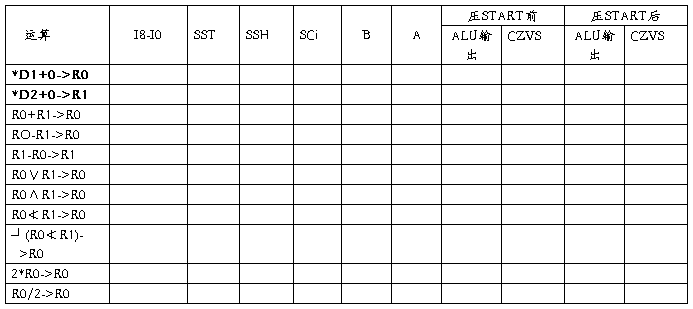

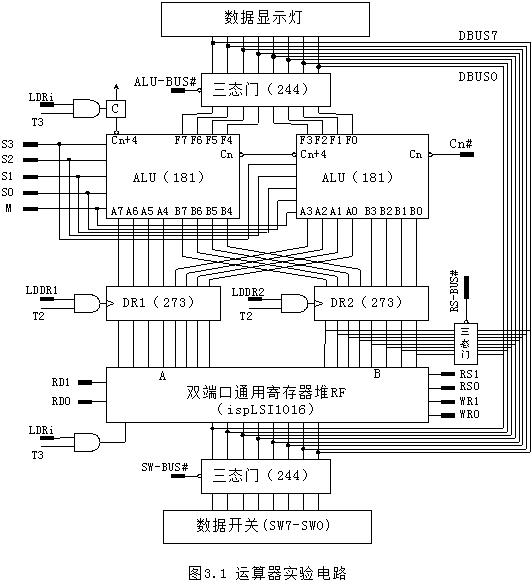

图3.1示出了本实验所用的运算器数据通路图。参与运算的数据首先通过实验台操作板上的八个二进制数据开关SW7-SW0来设置,然后输入到双端口通用寄存器堆RF中。

RF(U54)由一个ispLSI1016实现,功能上相当于四个8位通用寄存器,用于保存参与运算的数据,运算后的结果也要送到RF中保存。双端口寄存器堆模块的控制信号中,RS1、RS0用于选择从B端口(右端口)读出的通用寄存器,RD1、RD0用于选择从A端口(左端口)读出的通用寄存器。而WR1、WR0用于选择写入的通用寄存器。LDRi是写入控制信号,当LDRi=1时,数据总线DBUS上的数据在T3写入由WR1、WR0指定的通用寄存器。RF的A、B端口分别与操作数暂存器DR1、DR2相连;另外,RF的B端口通过一个三态门连接到数据总线DBUS上,因而RF中的数据可以直接通过B端口送到DBUS上。

DR1(U47)和DR2(U48)各由1片74LS273构成,用于暂存参与运算的数据。DR1接ALU的A输入端口,DR2接ALU的B输入端口。ALU(U31、U35)由两片74LS181构成,ALU的输出通过一个三态门(74LS244)发送到数据总线DBUS上。

实验台上的八个发光二极管DBUS7-DBUS0显示灯接在DBUS上,可以显示输入数据或运算结果。另有一个指示灯C显示运算器进位标志信号状态。

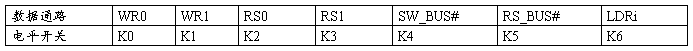

图中尾巴上带粗短线标记的信号都是控制信号,其中S3、S2、S1、S0、M、Cn#、LDDR1、LDDR2、ALU_BUS#、SW_BUS#、LDRi、RS1、RS0、RD1、RD0、WR1、WR0都是电位信号,在本次实验中用拨动开关K0—K15来模拟;T2、T3为时序脉冲信号,印制板上已连接到实验台的时序电路。实验中进行单拍操作,每次只产生一组T1、T2、T3、T4时序脉冲,需将实验台上的DP、DB开关进行正确设置。将DP开关置1,DB开关置0,每按一次QD按钮,则顺序产生T1、T2、T3、T4一组单脉冲。

三、实验设备

1. TEC-5计算机组成实验系统1台

2. 逻辑测试笔一支(在TEC-5实验台上)

3. 双踪示波器一台(公用)

4. 万用表一只(公用)

四、实验任务

1. 按图3.1所示,将运算器模块与实验台操作板上的线路进行连接。由于运算器模块内部的连线已由印制板连好,故接线任务仅仅是完成数据开关、控制信号模拟开关、与运算器模块的外部连线。注意:为了建立清楚的整机概念,培养严谨的科研能力,手工连线是绝对必要的。

2. 用开关SW7—SW0向通用寄存器堆RF内的R0—R3寄存器置数。然后读出R0—R3的内容,在数据总线DBUS上显示出来。

3. 验证ALU的正逻辑算术、逻辑运算功能。

令DR1=55H,DR2=0AAH,Cn#=1。在M=0和M=1两种情况下,令S3—S0的值从0000B变到1111B,列表表示出实验结果。实验结果包含进位C,进位C由指示灯显示。注意:进位C是运算器ALU最高位进位Cn+4#的反,即有进位为1,无进位为0。

五、实验要求

1. 做好实验预习,掌握运算器的数据传输通路及其功能特性,并熟悉本实验中所用的模拟开关的作用和使用方法。

2. 写出实验报告,内容是:

(1) 实验目的。

(2) 按实验任务3的要求,列表表示出实验结果。

(3) 按实验任务4的要求,在表中填写各控制信号模拟开关值,以及运算结果值。

六、实验步骤和实验结果

(1)实验任务2 的实验步骤和结果如下:(假定令R0=34H,R1=21H,R2=52H,R3=65H)

1. 置DP=1,DB=0,编程开关拨到正常位置。

接线表如下:

2. 打开电源

以下4条是将34H、21H、52H、65H分别写入R0、R1、R2、R3

3. 置K0(WR0)=0,K1(WR1)=0,K4(SW_BUS#)=0,K5(RS_BUS#)=1, K6(LDRi)=1,SW7-SW0=34H。在DBUS上将观察到DBUS=34H。按QD按钮,将34H写入R0。

4. 置K0(WR0)=1,K1(WR1)=0,K4(SW_BUS#)=0,K5(RS_BUS#)=1, K6(LDRi)=1,SW7—SW0=21H。在DBUS上将观察到DBUS=21H。按QD按钮,将21H写入R1。

5. 置K0(WR0)=0,K1(WR1)=1,K4(SW_BUS#)=0,K5(RS_BUS#)=1, K6(LDRi)=1,SW7—SW0=52H。在DBUS上将观察到DBUS=52H。按QD按钮,将52H写入R2。

6. 置K0(WR0)=1,K1(WR1)=1,K4(SW_BUS#)=0,K5(RS_BUS#)=1, K6(LDRi)=1,SW7—SW0=65H。在DBUS上将观察到DBUS=65H。按QD按钮,将65H写入R3。

以下4条是在DBUS总线上显示R0、R1、R2、R3的值

7. 置K2(RS0)=0,K3(RS1)=0,K4(SW_BUS#)=1,K5(RS_BUS#)=0, K6(LDRi)=0,在DBUS上将观察到DBUS=34H。

8. 置K2(RS0)=1,K3(RS1)=0,K4(SW_BUS#)=1,K5(RS_BUS#)=0, K6(LDRi)=0,在DBUS上将观察到DBUS=21H。

9. 置K2(RS0)=0,K3(RS1)=1,K4(SW_BUS#)=1,K5(RS_BUS#)=0, K6(LDRi)=0,在DBUS上将观察到DBUS=52H。

置K2(RS0)=1,K3(RS1)=1,K4(SW_BUS#)=1,K5(RS_BUS#)=0, K6(LDRi)=0,在DBUS上将观察到DBUS=65H。

(2)实验任务3的实验步骤和实验结果如下:

1.置DP=1,DB=0,编程开关拨到正常位置。

接线图如下:

数据通路的信号Cn#接VCC。

1. 打开电源

以下2条是向R0写入55H,向R1写入0AAH。

2. 置K0(WR0)=0,K1(WR1)=0,K6(LDRi)=1, K13(ALU_BUS#)=1,K14(SW_BUS#)=0。置SW7-SW0为55H,按QD按钮,将55H写入R0。

3. 置K0(WR0)=1,K1(WR1)=0,K6(LDRi)=1, K13(ALU_BUS#)=1,K14(SW_BUS#)=0。置SW7-SW0为0AAH,按QD按钮,将0AAH写入R1。

以下1条是将R0写入DR1,将R1写入DR2。

4. 置K2(RD0)=0,K3(RD1)=0,K4(RS0)=1,K5(RS1)=0,K6(LDRi)=0,K7(LDDR1和LDDR2)=1。按QD按钮,将R0写入DR1,将R1写入DR2。这时DR1=55H,DR2=0AAH。

以下2条是M=H时进行逻辑运算。

5. 置K6(LDRi)=1,K7(LDR1和LDR2)=0,K8(S0)=0,K9(S1)=0,K10(S2)=0,K11(S3)=0,K12(M)=1,K13(ALU_BUS#)=0,K14(SW_BUS#)=1。在数据总线DBUS上观察到逻辑运算结果0AAH。按QD按钮,观察到进位C为0。

6. 其他开关设置都不变,只改变K8(S0)、K9(S1)、K10(S2)、K11(S3)的设置,观察其他15种逻辑运算结果,并按QD按钮,观察进位C。

以下2条是M=L时进行算术运算。

7. 置K6(LDRi)=1,K7(LDR1和LDR2)=1,K8(S0)=0,K9(S1)=0,K10(S2)=0,K11(S3)=0,K12(M)=0,K13(ALU_BUS#)=0,K14(SW_BUS#)=1。在数据总线DBUS上观察到算术运算结果为55H。按QD按钮,观察到进位C为0。

8. 其他开关设置都不变,只改变K8(S0)、K9(S1)、K10(S2)、K11(S3)的设置,观察其他15种算术运算结果,并按QD按钮,观察进位C。

实验结果如下:

表3.2 实验任务3实验结果(DR1=55H,DR2=0AAH)