《电子线路课程设计报告》

系 别: 自动化

专业班级: 自动化0803

学生姓名: 冯刚

指导教师: 朱定华

(课程设计时间:20##年05月31日——20##年06月12日)

华中科技大学武昌分校

目 录

1.课程设计目的…………………………………………………………………3

2.课程设计题目描述和要求 ……………………………………………3

3.课程设计报告内容……………………………………………………………3-9

3.1实验名称………………………………………………………………………3

3.2实验目的………………………………………………………………………3

3.3实验器材及主要器件…………………………………………………………3

3.4数字电子钟基本原理…………………………………………………………4

3.5数字电子钟单元电路设计、参数计算和器件选择…………………………4-8

3.6数字电子钟电路图……………………………………………………………8

3.7数字电子钟的组装与调试……………………………………………………8-9

4.总结……………………………………………………………………………9

参考文献 …………………………………………………………………………10

1.课程设计目的

※掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;

※进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;

※提高电路布局﹑布线及检查和排除故障的能力;

※培养书写综合实验报告的能力。

2.课程设计题目描述和要求

(1)设计一个有“时”、“分”、“秒”(12小时59分59秒)显示,且有校时功能的电子钟;

(2)用中小规模集成电路组成电子钟,并在实验箱上进行组装、调试;

(3)画出框图和逻辑电路图,写出设计、实验总结报告;

(4)选做:整点报时。在59分51秒、53秒、55秒、57秒输出500Hz音频信号,在59分59秒时输出1000Hz信号,音频持续1s,在1000Hz荧屏结束时刻为整点。

3.课程设计报告内容

3.1实验名称

数字电子钟

3.2实验目的

·掌握数字电子钟的设计、组装与调试方法;

·熟悉集成电路的使用方法。

3.3实验器材及主要器件

(1)74LS48( 6片)

(2)74LS90(5片)

(3)74LS191(1片)

(4)74LS00(5片)

(5)74LS04(3片)

(6)74LS74(1片)

(7)74LS2O(2片)

(8)555集成芯片(1片)

(9)共阴七段显示器(6片)

(10)电阻、电容、导线等(若干)

3.4数字电子钟基本原理

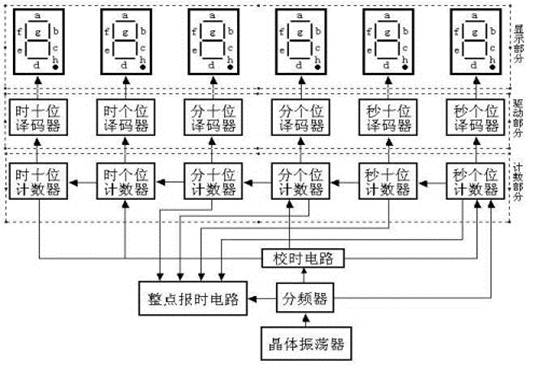

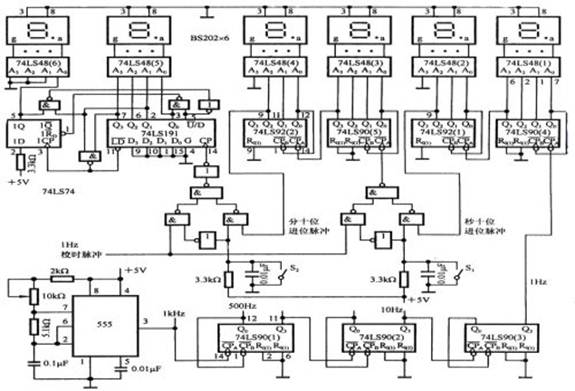

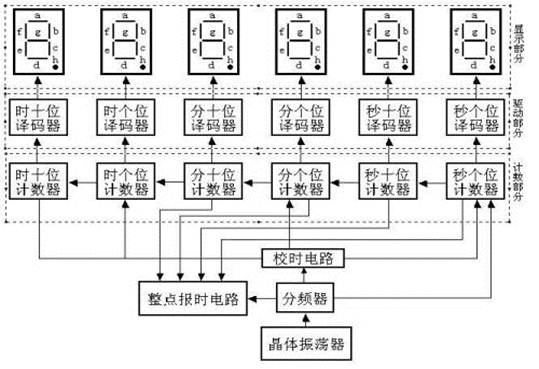

数字电子钟的逻辑框图如图3-4所示。它由555集成芯片构成的振荡电路、分频器、计数器、显示器和校时电路组成。555集成芯片构成的振荡电路产生的信号经过分频器作为秒脉冲,秒脉冲送入计数器,计数结果通过“时”、“分”、“秒”译码器显示时间。

图3-4

图3-4

3.5数字电子钟单元电路设计、参数计算和器件选择

1.振荡器

石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。它还具有压电效应,在晶体某一方向加一电场,则在与此垂直的方向产生机械振动,有了机械振动,就会在相应的垂直面上产生电场,从而机械振动和电场互为因果,这种循环过程一直持续到晶体的机械强度限止时,才达到最后稳定。这用压电谐振的频率即为晶体振荡器的固有频率。

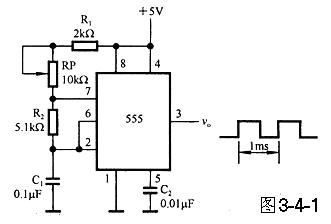

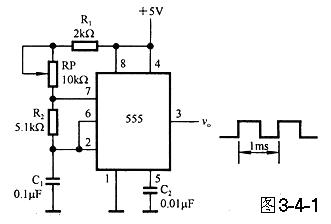

一般来说,振荡器的频率越高,计时精度越高,但耗电量将增大。如果精度要求不高也可以采用由集成电路定时器555与RC组成的多谐振荡器。如图3-4-1所示。设振荡频率f=1KHz,R为可调电阻,微调R1可以调出1KHz输出。

2.分频器

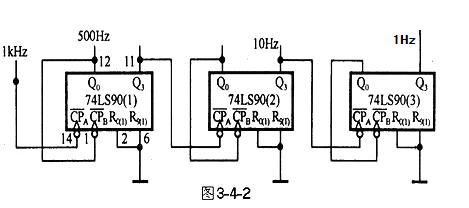

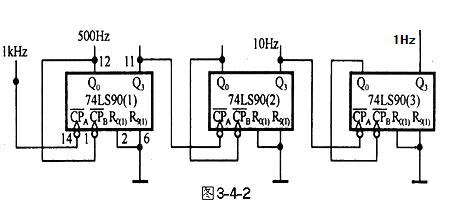

由于振荡器产生的频率很高,要得到秒脉冲,需要分屏电路。本实验由集成电路定时器555与RC组成的多谐振荡器,产生1KHz的脉冲信号。故采用3片中规模集成电路计数器74LS90来实现,得到需要的秒脉冲信号。如图3-4-2所示。

3.计数器

秒脉冲信号经过6级计数器,分别得到“秒”个位、十位、“分”个位、十位以及“时”个位、十位的计时。“秒”“分”计数器为六十进制,小时为十二进制。

(1)六十进制计数

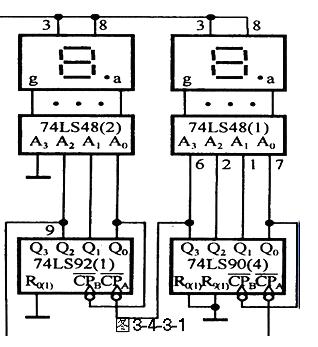

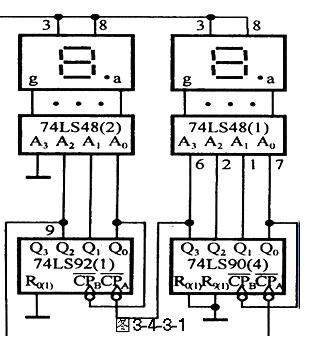

由分频器来的秒脉冲信号,首先送到“秒”计数器进行累加计数,秒计数器应完成一分钟之内秒数目的累加,并达到60秒时产生一个进位信号,所以,选用一片74LS90和一片74LS92组成六十进制计数器,采用反馈归零的方法来实现六十进制计数。其中,“秒”十位是六进制,“秒”个位是十进制。如图3-4-3-1所示。

(2)十二四进制计数

“12翻1”小时计数器是按照“01——02——03——……——11——12——01——02——……”规律计数的,这与日常生活中的计时规律相同。在此实验中,小时的个位计数器由4位二进制同步可逆计数器74LS191构成,十位计数器由D触发器74LS74构成,将它们级连组成“12翻1”小时计数器。

计数器的状态要发生两次跳跃:一是计数器计到9,即个位计数器的状态为Q03Q02Q01Q00=1001,在下一脉冲作用下计数器进入暂态1010,利用暂态的两个1即Q03Q01使个位异步置0,同时向十位计数器进位使Q10=1;二是计数器计到12后,在第13个脉冲作用下个位计数器的状态应为Q03Q02Q01Q00=0001,十位计数器的Q10=0。第二次跳跃的十位清0和个位置1信号可由暂态为1的输出端Q10,Q01,Q00来产生。

4.译码器

译码是指把给定的代码进行翻译的过程。计数器采用的码制不同,译码电路也不同。74LS48驱动器是与8421BCD编码计数器配合用的七段译码驱动器。74LS48配有灯测试LT、动态灭灯输入RBI,灭灯输入/动态灭灯输出BI/RBO,当LT=0时,74LS48出去全1。

5.显示器

本系统用七段发光二极管来显示译码器输出的数字,显示器有两种:共阳极显示器或共阴极显示器。74LS48译码器对应的显示器是共阴极显示器。

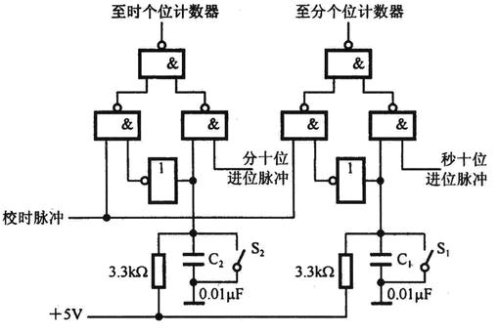

6.校时电路

当数字钟走时出现误差时,需要校正时间。校时电路实现对“时”“分”“秒”的校准。在电路中设有正常计时和校对位置。本实验实现“时”“分”的校对。对校时的要求是,在小时校正时不影响分和秒的正常计数;在分校正时不影响秒和小时的正常计数。需要注意的时,校时电路是由与非门构成的组合逻辑电路,开关S1或S2为“0”或“1”时,可能会产生抖动,为防止这一情况的发生我们接入一个由RS触发器组成的防抖动电路来控制。

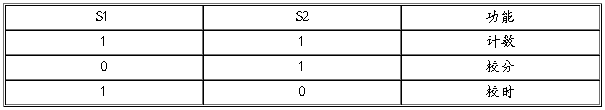

图3-4-6-1 校时开关的功能表

图3-4-6-2 校时电路

3.6数字电子钟电路图

3.7数字电子钟的组装与调试

由图3-4所示的数字中系统组成框图按照信号的流向分级安装,逐级级联。这里的每一级是指组成数字中的各个功能电路。

级联时如果出现时序配合不同步,或剑锋脉冲干扰,引起的逻辑混乱,可以增加多级逻辑门来延时。如果显示字符变化很快,模糊不清,可能是由于电源电流的跳变引起的,可在集成电路器件的电源端Vcc加退藕滤波电容。通常用几十微法的大电容与0.01μF的小电容相并联。

4.总结

虽然我们学习了模电和数电,对电子技术有了一些初步了解,但那都是一些理论的东西。通过这次数字电子钟的课程设计,我们才把学到的东西与实践相结合。从中对我们学的知识有了更进一步的理解。

为期两周的课程设计使我更进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法。也锻炼了自己独立思考问题的能力和通过查看相关资料来解决问题的习惯。虽然这只是一次简单的课程设计,但通过这次课程设计我们了解了课程设计的一般步骤,和设计中应注意的问题。设计本身并不是有很重要的意义,而是同学们对待问题时的态度和处理事情的能力。至于设计的成绩无须看的太过于重要,而是设计的过程,设计的思想和设计电路中的每一个环节,电路中各个部分的功能是如何实现的。各个芯片能够完成什么样的功能,使用芯片时应该注意那些要点。同一个电路可以用那些芯片实现,各个芯片实现同一个功能的区别。另外,我们设计要从市场需求出发,既要有强大的功能,又要在价格方面比同等档次的便宜。

同时对普通计数器如何构成n进制计数器有了更深的了解和掌握,对自我的实际操作能力也有了很高的提升。

在电脑制作文档的过程中,我也对办公软件有了更进一步的了解,使我对办公软件有了更深层次的掌握。

参考文献

1. 现代数字电路与逻辑设计 清华大学出版社 北京交通大学出版社.

2. 模拟电子技术(修订版) 清华大学出版社 北京交通大学出版社

3. 模拟电子技术教程 电子工业出版社

5. 朱定华主编.电子电路测试与实验.北京:清华大学出版社,2004.

课程设计成绩:

注:教师按学生实际成绩(平时成绩和业务考核成绩)登记并录入教务MIS系统,由系统自动转化为“优秀(90~100分)、良好(80~89分)、中等(70~79分)、及格(60~69分)和不及格(60分以下)”五等。

指导教师评语:

指导教师(签名):

20 年 月 日

第二篇:数字电子钟的设计报告.doc.deflate

数字电子钟设计报告

目 录

1.实验目的………………………………………………………………………2

2.实验题目描述和要求 …………………………………………………………2

3.设计报告内容…………………………………………………………………2

3.1实验名称………………………………………………………………………2

3.2实验目的………………………………………………………………………2

3.3实验器材及主要器件…………………………………………………………2

3.4数字电子钟基本原理…………………………………………………………3

3.5数字电子钟单元电路设计、参数计算和器件选择…………………………3-7

3.6数字电子钟电路图……………………………………………………………7

3.7数字电子钟的组装与调试……………………………………………………7-8

4.总结……………………………………………………………………………8

1.实验目的

※掌握组合逻辑电路、时序逻辑电路及数字逻辑电路系统的设计、安装、测试方法;

※进一步巩固所学的理论知识,提高运用所学知识分析和解决实际问题的能力;

※提高电路布局﹑布线及检查和排除故障的能力;

※培养焊接实际操作及书写综合实验报告的能力。

2.实验题目描述和要求

(1)设计一个有“时”、“分”、“秒”显示,且有校时功能的电子钟;

(2)用中小规模集成电路组成电子钟,并在经过仿真再进行实际组装、调试;

(3)画出框图和逻辑电路图,写出设计、仿真、焊接、调试、总结;

3.设计报告内容

3.1实验名称

数字电子钟

3.2实验目的

·掌握数字电子钟的设计、组装与焊接调试方法;

·熟悉集成电路的使用方法。

3.3实验器材及主要器件

(1)74LS48( 6片)

(2)74LS90(5片)

(3)74LS191(1片)

(4)74LS00(5片)

(5)74LS04(3片)

(6)74LS74(1片)

(7)74LS2O(2片)

(8)555集成芯片(1片)

(9)共阴七段显示器(6片)

(10)电阻、电容、导线等(若干)

3.4数字电子钟基本原理

数字电子钟的逻辑框图如图3-4所示。它由555集成芯片构成的振荡电路、分频器、计数器、显示器和校时电路组成。555集成芯片构成的振荡电路产生的信号经过分频器作为秒脉冲,秒脉冲送入计数器,计数结果通过“时”、“分”、“秒”译码器显示时间。

图3-4

图3-4

3.5数字电子钟单元电路设计、参数计算和器件选择

1.振荡器

石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。它还具有压电效应,在晶体某一方向加一电场,则在与此垂直的方向产生机械振动,有了机械振动,就会在相应的垂直面上产生电场,从而机械振动和电场互为因果,这种循环过程一直持续到晶体的机械强度限止时,才达到最后稳定。这用压电谐振的频率即为晶体振荡器的固有频率。

一般来说,振荡器的频率越高,计时精度越高,但耗电量将增大。如果精度要求不高也可以采用由集成电路定时器555与RC组成的多谐振荡器。如图3-4-1所示。设振荡频率f=1KHz,R为可调电阻,微调R1可以调出1KHz输出。

2.分频器

由于振荡器产生的频率很高,要得到秒脉冲,需要分屏电路。本实验由集成电路定时器555与RC组成的多谐振荡器,产生1KHz的脉冲信号。故采用3片中规模集成电路计数器74LS90来实现,得到需要的秒脉冲信号。如图3-4-2所示。

3.计数器

秒脉冲信号经过6级计数器,分别得到“秒”个位、十位、“分”个位、十位以及“时”个位、十位的计时。“秒”“分”计数器为六十进制,小时为十二进制。

(1)六十进制计数

由分频器来的秒脉冲信号,首先送到“秒”计数器进行累加计数,秒计数器应完成一分钟之内秒数目的累加,并达到60秒时产生一个进位信号,所以,选用一片74LS90和一片74LS92组成六十进制计数器,采用反馈归零的方法来实现六十进制计数。其中,“秒”十位是六进制,“秒”个位是十进制。如图3-4-3-1所示。

(2)十二进制计数

“12翻1”小时计数器是按照“01——02——03——……——11——12——01——02——……”规律计数的,这与日常生活中的计时规律相同。在此实验中,小时的个位计数器由4位二进制同步可逆计数器74LS191构成,十位计数器由D触发器74LS74构成,将它们级连组成“12翻1”小时计数器。

计数器的状态要发生两次跳跃:一是计数器计到9,即个位计数器的状态为Q03Q02Q01Q00=1001,在下一脉冲作用下计数器进入暂态1010,利用暂态的两个1即Q03Q01使个位异步置0,同时向十位计数器进位使Q10=1;二是计数器计到12后,在第13个脉冲作用下个位计数器的状态应为Q03Q02Q01Q00=0001,十位计数器的Q10=0。第二次跳跃的十位清0和个位置1信号可由暂态为1的输出端Q10,Q01,Q00来产生。

4.译码器

译码是指把给定的代码进行翻译的过程。计数器采用的码制不同,译码电路也不同。74LS48驱动器是与8421BCD编码计数器配合用的七段译码驱动器。74LS48配有灯测试LT、动态灭灯输入RBI,灭灯输入/动态灭灯输出BI/RBO,当LT=0时,74LS48出去全1。

5.显示器

本系统用七段发光二极管来显示译码器输出的数字,显示器有两种:共阳极显示器或共阴极显示器。74LS48译码器对应的显示器是共阴极显示器。

6.校时电路

当数字钟走时出现误差时,需要校正时间。校时电路实现对“时”“分”“秒”的校准。在电路中设有正常计时和校对位置。本实验实现“时”“分”的校对。对校时的要求是,在小时校正时不影响分和秒的正常计数;在分校正时不影响秒和小时的正常计数。需要注意的时,校时电路是由与非门构成的组合逻辑电路,开关S1或S2为“0”或“1”时,可能会产生抖动,为防止这一情况的发生我们接入一个RC组成的防抖动电路来控制。

图3-4-6-1 校时开关的功能表

图3-4-6-2 校时电路

3.6数字电子钟电路图

3.7数字电子钟的组装与调试

由图3-4所示的数字中系统组成框图按照信号的流向分级安装,逐级级联。这里的每一级是指组成数字中的各个功能电路。

级联时如果出现时序配合不同步,或剑锋脉冲干扰,引起的逻辑混乱,可以增加多级逻辑门来延时。如果显示字符变化很快,模糊不清,可能是由于电源电流的跳变引起的,可在集成电路器件的电源端Vcc加退藕滤波电容。通常用几十微法的大电容与0.01μF的小电容相并联。

4.总结

虽然我们学习了模电和数电,对电子技术有了一些初步了解,但那都是一些理论的东西。通过这次数字电子钟的课程设计,我们才把学到的东西与实践相结合。从中对我们学的知识有了更进一步的理解。

为期两周的课程设计使我更进一步地熟悉了芯片的结构及掌握了各芯片的工作原理和其具体的使用方法。也锻炼了自己独立思考问题的能力和通过查看相关资料来解决问题的习惯。虽然这只是一次简单的课程设计,但通过这次课程设计我们了解了课程设计的一般步骤,和设计中应注意的问题。设计本身并不是有很重要的意义,而是同学们对待问题时的态度和处理事情的能力。至于设计的成绩无须看的太过于重要,而是设计的过程,设计的思想和设计电路中的每一个环节,电路中各个部分的功能是如何实现的。各个芯片能够完成什么样的功能,使用芯片时应该注意那些要点。同一个电路可以用那些芯片实现,各个芯片实现同一个功能的区别。另外,我们设计要从市场需求出发,既要有强大的功能,又要在价格方面比同等档次的便宜。

同时对普通计数器如何构成n进制计数器有了更深的了解和掌握,对自我的实际操作能力也有了很高的提升。

在电脑制作文档的过程中,我也对办公软件有了更进一步的了解,使我对办公软件有了更深层次的掌握。