EDA实验二七段数码管显示译码的设计

一、实验目的

1、掌握七段数码管译码器的工作原理;

2、学会运用波形仿真测试检验程序的正确性;

3、学会运用波形仿真测试检验程序的正确性。

二、实验设备

ZYE1502C型实验箱

三、内容要求

1、用拨位开关输入8421BCD码,七段数码管显示“0-F”16个16进制的数字。

2、观察字符亮度和显示刷新的效果:

(1)在8个七段数码管上同时显示某一数字;

(2)在8个七段数码管上动态显示某一数字。

3、扩展内容:

(1)动态显示时,能即时改变显示的顺序;

(2)动态显示时,实现显示数字从0~F的循环显示。

四、实验步骤

1、输入:设计部分采用VHDL语言完成;

2、编译;

3、仿真;

4、下载;

5、连线。

(1)四个拨位开关(在P1、P2处选择)连接D3、D2、D1、D0信号所对应的管脚。时钟CLK所对应的管脚同实验箱上的时钟源相连。

(2)扫描片选信号DIG(0 TO 3)的管脚同七段数码管(共阴)相连;

(3)七段数码管驱动信号A,B,C,D,E,F,G的管脚分别同扫描数码管的段输入PCLK处的连接线孔A,B,C,D,E,F,G相连。

五、实验报告

1、论述实验过程和步骤;

2、填写正确的实验结果。

(1)通过两种显示效果分析:字符显示亮度同扫描频率的关系,且让人眼感觉不出光闪烁现象的最低扫描频率是多少?

答:扫描频率越高,显示亮度越低。人眼看是否闪烁与所用的时钟和分频方式有关,在频率稳定和分频均匀的情况下,最低扫描频率为256Hz,若分频不均匀或频率不稳定,则需更高频率。

(2)字形编码的种类,即一个7段数码管可产生多少种字符,产生所有字符需要多少根被译码信号线?

答:一个7段数码管可产生2^7=128种字符,产生所有字符至少需要7根被译码信号线。

但假如只编译0-F,16个字符,则至少只需要4根被译码信号线。

六、实验小结。

答:

1、不同控制端需要预先分配控制优先级,否则编写的时候会出现很多问题。优先级分为普通和特殊,一般错误情况可以跨越权限显示出来。

2、不同的错误需要不同的显示来区分。

3、LOAD和CLR的优先级低于EN,在EN从无效到有效的过程中(0→1),显示会根据现态和MODE出现多种情况:(0,次态,不定态,锁存值)等,所以一般在EN启动后,需要LOAD或者CLR来清空这些不确定因素。

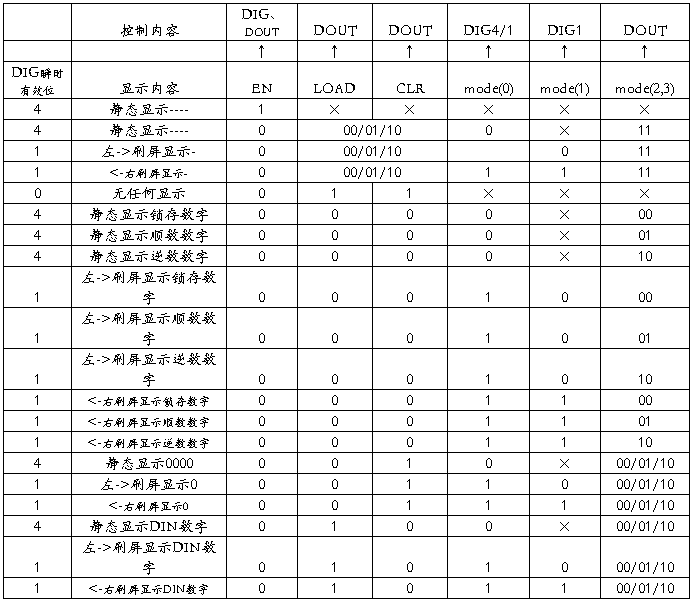

优先级设计:

控制端所有情况列表:

代码:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.All;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY segment IS

PORT (CLK : IN STD_LOGIC;

CP : Buffer STD_LOGIC;

EN : IN STD_LOGIC;

LOAD : IN STD_LOGIC;

CLR : IN STD_LOGIC;

MODE : IN STD_LOGIC_VECTOR(0 TO 3);

DOUT : OUT STD_LOGIC_VECTOR(0 TO 6);--对应A,B,C,D,E,F,G,DP输出

DIN : IN STD_LOGIC_VECTOR(3 DOWNTO 0);--对应4321位数字

DIG : OUT STD_LOGIC_VECTOR(0 TO 3));--段显信息,one hot

END segment;

ARCHITECTURE one OF segment IS

BEGIN

PROCESS (EN,LOAD,CLR,MODE,DIN,CLK,CP)

VARIABLE Q : STD_LOGIC_VECTOR(1 DOWNTO 0);

VARIABLE COUNT : STD_LOGIC_VECTOR(0 TO 3);

VARIABLE P : STD_LOGIC_VECTOR(0 TO 21);

BEGIN

--使能

IF EN='1' THEN DOUT(0 TO 6)<= "0000001";DIG(0 TO 3)<= "0000";

ELSIF LOAD='1' AND CLR='1' THEN DOUT(0 TO 6)<= "0000000";DIG(0 TO 3)<= "0000";

ELSE

--分频

IF CLK'EVENT AND CLK='1' THEN

IF P<3999999 THEN P := P + 1;

ELSE P := (OTHERS=>'0');

END IF;

END IF;

IF P=1999999 THEN CP<='1';

ELSE CP<='0';

END IF;

--刷屏模式:刷屏模式:0左->/1<-右mod(1)

IF CP'EVENT AND CP='1' THEN

IF (MODE(1)='0') THEN

IF Q<3 THEN Q := Q + 1;

ELSE Q := (OTHERS=>'0');

END IF;

ELSE

IF Q>0 THEN Q := Q - 1;

ELSE Q := "11";

END IF;

END IF;

END IF;

--刷屏模式:0静态/1刷屏模式mod(0)

IF (MODE(0)='0') THEN DIG(0 TO 3)<= "0000";

ELSE CASE Q IS

WHEN "00" => DIG(0 TO 3)<= "0111";

WHEN "01" => DIG(0 TO 3)<= "1011";

WHEN "10" => DIG(0 TO 3)<= "1101";

WHEN "11" => DIG(0 TO 3)<= "1110";

WHEN OTHERS => NULL;

END CASE;

END IF;

--显示数字:显示数字:00不变/01顺数/10逆数/11-mod(2,3)

IF LOAD='1' THEN COUNT(0 TO 3):=DIN(3 DOWNTO 0);

ELSIF CLR='1' THEN COUNT := "0000";

ELSE

IF CP'EVENT AND CP='1' THEN

IF (MODE(2)='0')AND(MODE(3)='0') THEN

COUNT := COUNT;

ELSIF (MODE(2)='0')AND(MODE(3)='1') THEN

IF COUNT<15 THEN COUNT := COUNT + 1;

ELSE COUNT := (OTHERS=>'0');

END IF;

ELSIF (MODE(2)='1')AND(MODE(3)='0') THEN

IF COUNT>0 THEN COUNT := COUNT - 1;

ELSE COUNT := "1111";

END IF;

ELSIF (MODE(2)='1')AND(MODE(3)='1') THEN

NULL;

END IF;

END IF;

END IF;

--显示模式

IF (MODE(2)='1')AND(MODE(3)='1') THEN DOUT(0 TO 6)<="0000001";

ELSE

CASE COUNT IS

WHEN "0000" => DOUT(0 TO 6)<= "1111110";

WHEN "0001" => DOUT(0 TO 6)<= "0110000";

WHEN "0010" => DOUT(0 TO 6)<= "1101101";

WHEN "0011" => DOUT(0 TO 6)<= "1111001";

WHEN "0100" => DOUT(0 TO 6)<= "0110011";

WHEN "0101" => DOUT(0 TO 6)<= "1011011";

WHEN "0110" => DOUT(0 TO 6)<= "1011111";

WHEN "0111" => DOUT(0 TO 6)<= "1110010";

WHEN "1000" => DOUT(0 TO 6)<= "1111111";

WHEN "1001" => DOUT(0 TO 6)<= "1111011";

WHEN "1010" => DOUT(0 TO 6)<= "1110111";

WHEN "1011" => DOUT(0 TO 6)<= "0011111";

WHEN "1100" => DOUT(0 TO 6)<= "1001110";

WHEN "1101" => DOUT(0 TO 6)<= "0111101";

WHEN "1110" => DOUT(0 TO 6)<= "1001111";

WHEN "1111" => DOUT(0 TO 6)<= "1000111";

END CASE;

END IF;

END IF;

END PROCESS;

END ARCHITECTURE one;

第二篇:《EDA技术与VHDL》实验七段数码管程序

EDA技术与VHDL实验:

七段数码管程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_Unsigned.ALL;

ENTITY showseg7 IS

PORT(clk: IN STD_LOGIC;

seg0,seg1,seg2,seg3,seg4,seg5,seg6,seg7:OUT STD_LOGIC;

dig0,dig1,dig2,dig3,dig4,dig5,dig6,dig7:OUT STD_LOGIC

);

END ENTITY showseg7;

ARCHITECTURE one OF showseg7 IS

SIGNAL count: STD_LOGIC_VECTOR(2 DOWNTO 0);

SIGNAL seg_r: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL dig_r: STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL data: STD_LOGIC_VECTOR(31 DOWNTO 0);

SIGNAL disp_r: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

data <= "00000001001000110100010101100111"; --??????,????????

PROCESS(clk) --1kHz

BEGIN

IF clk'EVENT AND clk='1' THEN

IF count<=7 THEN count<=count+1;

ELSE count<="000";

END IF;

END IF;

END PROCESS;

PROCESS(count)

BEGIN

CASE count IS

WHEN "000" => disp_r<=data(31 DOWNTO 28);dig_r<="01111111";--"00000000";--

WHEN "001" => disp_r<=data(27 DOWNTO 24);dig_r<="10111111";--"00000000";--

WHEN "010" => disp_r<=data(23 DOWNTO 20);dig_r<="11011111";--"00000000";--

WHEN "011" => disp_r<=data(19 DOWNTO 16);dig_r<="11101111";--"00000000";--

WHEN "100" => disp_r<=data(15 DOWNTO 12);dig_r<="11110111";--"00000000";--

WHEN "101" => disp_r<=data(11 DOWNTO 8);dig_r<="11111011";--"00000000";--

WHEN "110" => disp_r<=data(7 DOWNTO 4);dig_r<="11111101";--"00000000";--

WHEN "111" => disp_r<=data(3 DOWNTO 0);dig_r<="11111110";--"00000000";--

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

PROCESS(disp_r)

BEGIN

CASE disp_r IS

WHEN "0000" => seg_r<="00000011";--"10000001";

WHEN "0001" => seg_r<="10011111";--"11111001";

WHEN "0010" => seg_r<="00100101";--"10110001";

WHEN "0011" => seg_r<="00001101";--"11000010";

WHEN "0100" => seg_r<="10011001";--"11011000";

WHEN "0101" => seg_r<="01001001";--"10100100";

WHEN "0110" => seg_r<="11000001";--"10100000";

WHEN "0111" => seg_r<="00011111";--"10001111";

WHEN "1000" => seg_r<="00000000";--"10000000";

WHEN "1001" => seg_r<="00001001";--"10000100";

-- WHEN "1010" => seg_r<="";

-- WHEN "1011" => seg_r<="";

-- WHEN "1100" => seg_r<="";

-- WHEN "1101" => seg_r<="";

-- WHEN "1110" => seg_r<="";

-- WHEN "1111" => seg_r<="";

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

seg0<=seg_r(0);

seg1<=seg_r(1);

seg2<=seg_r(2);

seg3<=seg_r(3);

seg4<=seg_r(4);

seg5<=seg_r(5);

seg6<=seg_r(6);

seg7<=seg_r(7);

dig0<=dig_r(0);

dig1<=dig_r(1);

dig2<=dig_r(2);

dig3<=dig_r(3);

dig4<=dig_r(4);

dig5<=dig_r(5);

dig6<=dig_r(6);

dig7<=dig_r(7);

end architecture one;