电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室

实验一七段数码显示译码器

一. 实验目的:

1. 设计七段显示译码器,并在实验板上验证;

2. 学习Verilog HDL文本文件进行逻辑设计输入;

3. 学习设计仿真工具的使用方法;

二. 实验内容

1.实现BCD/七段显示译码器的“ Verilog ”语言设计。

说明:7段显示译码器的输入为:IN0…IN3共5根, 7段译码器的逻辑表同学自行设计,要求实现功能为:输入“ 0…15 (”二进制),输出“ 0…9…F (”显示数码),输出结果应在数码管(共阴)上显示出来。

2. 使用工具为译码器建立一个元件符号

3. 设计仿真文件,进行验证。

4. 编程下载并在实验箱上进行验证。

三. 实验原理:

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。例如6-18作为7段译码器,输出信号LED7S的7位分别接图6-17数码管的7个段,高位在左,低位在右。例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

1 / 8

电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室

四. 实验步骤

1.编辑和输入设计文件

新建文件夹——输入源程序——文件存盘

2.创建工程

打开并建立新工程管理窗口——将设计文件加入工程中——选择目标芯片——工具设置——结束设置

3.全程编译前约束项目设置

选择FPGA目标芯片——选择配置器件的工作方式——选择配置器件和编程方式——选择目标器件引脚端口状态——选择Verilog语言版本

4.仿真测试

五. 实验参考程序

module LED(A,LED7S);

input [3:0]A;

output [6:0]LED7S;

reg [6:0]LED7S;

always @ (A)

begin:

case(A)

4'b0000: LED7S<=7'b0111111;

4'b0001: LED7S<=7'b0000110;

4'b0010: LED7S<=7'b1011011;

4'b0011: LED7S<=7'b1001111;

2 / 8

电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室 4'b0100: LED7S<=7'b1100110;

4'b0101: LED7S<=7'b1101101;

4'b0110: LED7S<=7'b1111101;

4'b0111: LED7S<=7'b0000111;

4'b1000: LED7S<=7'b1111111;

4'b1001: LED7S<=7'b1101111;

4'b1010: LED7S<=7'b1110111;

4'b1011: LED7S<=7'b1111100;

4'b1100: LED7S<=7'b0111001;

4'b1101: LED7S<=7'b1011110;

4'b1110: LED7S<=7'b1111001;

4'b1111: LED7S<=7'b1110001;

default: LED7S<=7'b0111111;

endcase

end

endmodule

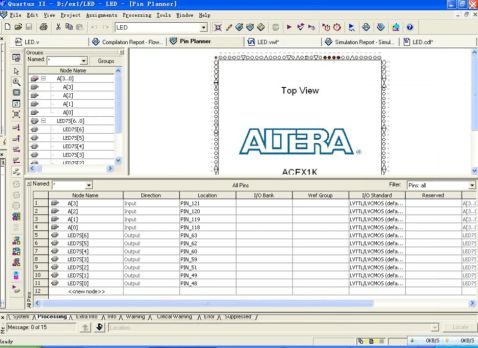

六. 编译仿真结果

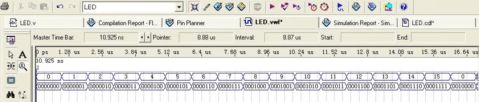

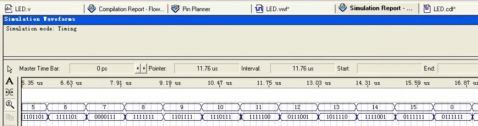

1.时序仿真

:

3 / 8

电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室

2.延时分析及结果:

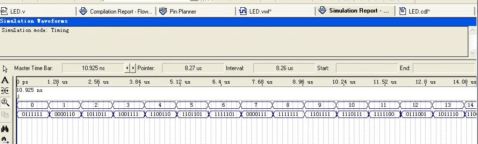

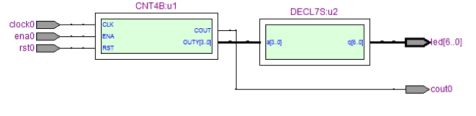

3.生成RTL原理图:

4 / 8

电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室

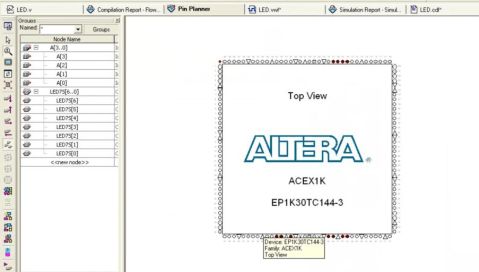

4.该实验的配置模式:

5 / 8

电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室

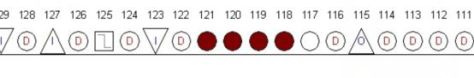

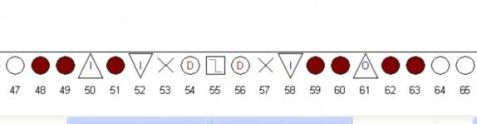

5.适配板布局图及实验仪IO脚与芯片的管脚对应关系和其详细放大图片:

6 / 8

电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室

6.十六进制逻辑分析:

7 / 8

电子设计自动化实验报告 学号:201115002 姓名:王冬冬 实验时间:第3周( 3月14日) 星期五(第一大节)实验地点:s5楼 208教室

7.计数器和译码器连接电路的顶层文件原理图:

七.体会思考:

通过本次实验对EDA和QUARTER2有了初步的了解,第一次上机感觉挺难的,这次对Verilog也有了深入了解。学会了7段数码显示译码器的Verilog硬件设计,学习了VHDL的CASE语句应用。认识到做实验应该提前弄清实验原理,做实验时耐心、认真,遇到问题争取努力解决。并且在实验后应认真总结实验,分析波形,完成实验报告。这门课程锻炼了我读程序的能力和分析语法用法的能力,为我将来学更高级的语言打下了基础。

8 / 8

第二篇:数字实验二 译码器及数码管驱动芯片应用 实验报告

学生实验报告