多功能数字时钟设计报告

目录

一、设计任务和要求……………………………………………2

二、设计的方案的选择与论证…………………………………2

(1) 总体电路分析…………………………………………2

(2) 仿真分析………………………………………………3

(3) 仿真说明………………………………………………3

三、电路设计计算与分析………………………………………4

(1) 小时计时电路………………………………………4

(2) 分钟计时电路………………………………………5

(3) 秒钟计时电路………………………………………7

(4) 校时选择电路………………………………………8

(5) 整点译码电路………………………………………9

(6) 定时比较电路………………………………………11

(7) 脉冲产生电路………………………………………12

四、电路仿真

五、总结及心得…………………………………………………13

六、附录…………………………………………………………15

(1) 元器件明细表……………………………………………15

(2) 附图………………………………………………………17

七、参考文献……………………………………………………17

一、 设计任务和要求

实现24小时的时钟显示、校准、整点报时、闹铃等功能。

具体要求:

(1)显示功能:具有“时”、“分”、“秒”的数字显示(“时”从0~23,分0~59,秒0~59)。

(2)校时功能:当刚接通电源或数字时钟有偏差时,可以通过手动的方式去校时。

(3)整点报时:当时钟计时到整点时,能进行整点报时。

(4)闹铃功能:在24小时之内,可以设定定时时间,当数字时钟到定时时间时能进行报时提醒。

二、 设计的方案的选择与论证

(1) 总体电路分析

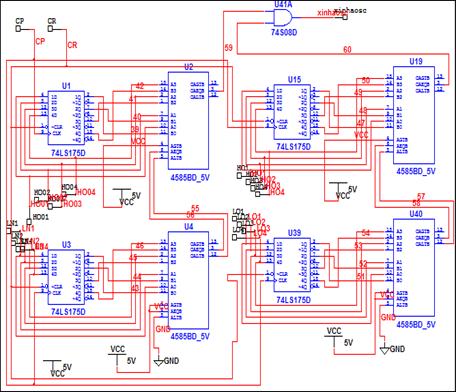

总体电路设计是将单元电路模块小时计时电路、分钟计时电路、秒计时电路、校时选择电路、整点译码电路、闹钟电路等模块连接在一起,外接输入开关和输出显示数码管构成。总体结构图如下:

(2) 仿真分析

单击运行按钮,可观测仿真结果。电路能完成显示计时、校时、整点报时以及闹铃等功能。

1计时功能。当开关S1、S2都处于左边触点时,数字时钟工作于计时状态。此时,电路中的秒计时电路、分计时电路以及小时计时电路分别对秒脉冲、分脉冲和小时脉冲进行计数。计数结果经数码管显示计时时间值。

2校时功能。当开关S1、S2都处于右边触点时,数字时钟工作于校时状态。按瞬态按钮B键,可以选择对“小时”、“分钟”和“秒钟”进行校时。校时时通过开关S3(按C键)手动输入校时时间。

3整点报时功能。整点译码电路通过识别整点时间,产生整点报时信号。当前时间为零点时,会产生整点报时,此时探针会亮,蜂鸣器会响。

4闹钟报时功能。通过校时功能将“小时”、“分钟”和“秒钟”设定在某一时间点,然后重新校时,调整到设定点以前的某一时间,当时钟到达设定点时,信号灯会亮,并且蜂鸣器会响。

(3) 仿真说明。

1因版面有限,总设计图并未纳入本设计报告中,而是在此之外通过PROTELL画图,用A3纸另外打印。这样看图较为清晰。

2采用总线方式,使信号线连线简介、美观,电路可持续性强。

三、 电路设计计算与分析

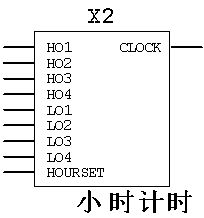

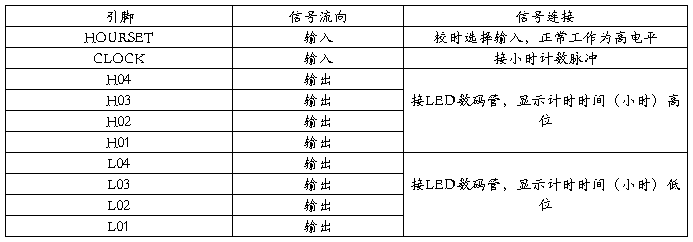

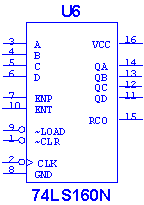

(1) 小时计时电路。小时计时电路如下图:

该电路用两片74LS160构成二十四进制计数器,与非门74LS00D构成译码电路,该译码电路能识别代码“24”,输出信号使~CLR=0,计数器的计数值被置0.所以,整个计数器的技术状态图为00至01至02至…至23至24(暂态)至00至01至…,共有24个稳定状态。小时计时电路的封装模块如下图:

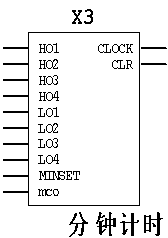

其引脚功能如表:

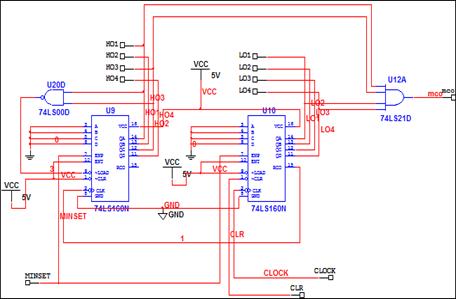

(2) 分钟计时电路。分钟计时电路如下图:

该电路用两片74LS160构成六十进制计数器,与非门74LS00D构成译码电路,该译码电路能识别代码59。整个计数器的计数状态图为00至01至…至58至59至00…,共有60个稳定的状态。其封装引脚同小时计时电路。分钟计时电路的封装模块如下图:

其引脚功能如下表:

(3) 秒钟计时电路。秒钟计时电路如下图:

该电路用两片74LS160构成六十进制计数器,与非门74LS00D构成译码电路,该译码电路能识别代码59。整个计数器的计数状态图为00至01至…至58至59至00…,共有60个稳定的状态。其封装引脚同小时计时电路。秒钟计时电路的封装模块如下图:

其引脚功能如下表:

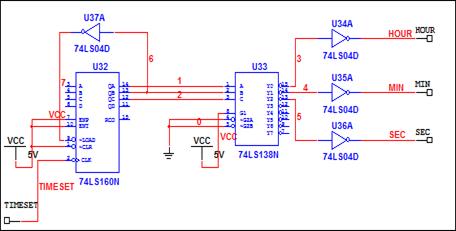

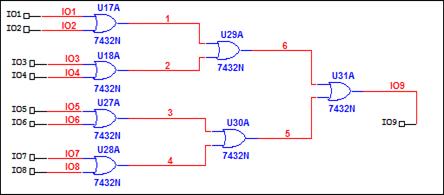

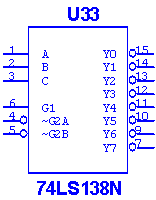

(4) 校时选择电路。校时选择电路如下图:

校时选择电路用计数器74LS160和译码器74LS138组成,计数器74LS160设计为三进制计数器,译码器的输出为反变量,其输出要接反向器。校时选择电路的封装模块如下图:

其对应的封装引脚如下表:

TIMESET:接瞬态开关,可手动选择校时信号。当校时信号HOUR=1、MIN=0、SEC=0时(选中“小时”计时电路,表示对“小时”进行校时);单击一次开关按钮,可使校时选择信号变为HOUR=0、MIN=1、SEC=0(选中“分钟”计时电路,表示对“分钟”进行校时),再单击一次开关按钮,可使校时选择信号变为HOUR=0、MIN=0、SEC=1(选中“秒”计时电路,表示对“秒”进行校时),这样可手动设置系统的时、分和秒。

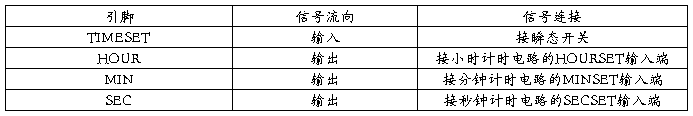

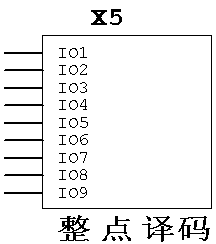

(5) 整点译码电路。

整点译码电路的作用是识别整点时间信号,以实现整点报时的功能。整点时间信号的特征是零分,零分作为数字量来说,是一个代码,用门电路组成的译码电路可识别一个代码。整点译码电路如下图:

其封装模块如下图:

其引脚功能功能如表:

(6) 定时比较电路(闹钟电路)。

定时比较电路是将设定的定时时间和当前的计时时间进行比较,电路可选用数值比较器CC4585。定时比较电路如图所示:

该电路共用四片CC4585和四片74LS175D构成定时比较电路,因为定时时间为小时和分钟,共16位二进制代码,每片数值比较器CC4585能比较两个4位二进制代码,用4片CC4585能构成16位数值比较器。当数字时钟的计时时间等于设定时间时,定时比较电路输出高电平,否则输出低电平。定时比较电路封装模块如图:

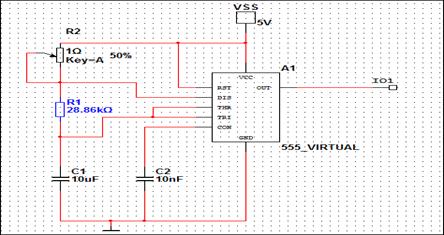

(7) 脉冲产生电路。

脉冲产生电路如图:

该电路由555定时器构成时钟脉冲产生电路。由于其相对于MULTSIM软件提供的脉冲产生器件较复杂,故在此并不是用这个秒脉冲电路,而是用所提供器件。

四、 总结与心得

时间过的好快,转眼间,为期一周的数字电路课程设计就结束了。通过这一周的课程设计,我拓宽了知识面,锻炼了能力,综合素质得到较大提高。

设计,给人以创作的冲动。但凡涉及设计都是一件良好的事情,因为她能给人以美的幻想,因为她能给人以金般财富,因为她能给人以成就之感,更为现实的是她能给人以成长以及成长所需的营养,而这种营养更是一种福祉,一辈子消受不竭享用不尽。安排课程设计的基本目的,在于通过理论与实际的结合、人与人的沟通,进一步提高思想觉悟。尤其是观察、分析和解决问题的实际工作能力,以便培养成为能够主动适应社会主义现代化建设需要的高素质的复合型人才。

课程设计发端之始,思绪全无,举步维艰,对于理论知识学习不够扎实的我深感“书到用时方恨少”,于是想起圣人之言“温故而知新”,便重拾教材与实验手册,对知识系统而全面进行了梳理,遇到难处先是苦思冥想再向同学请教,终于熟练掌握了基本理论知识,而且领悟诸多平时学习难以理解掌握的较难知识,学会了如何思考的思维方式,找到了设计的灵感。

课程设计的过程中,由于对理论掌握的不熟练,或者是操作过程中发生失误,都会导致最后结果出不来。至善至美,是人类永恒的追求。但是,不从忘却“金无足赤,人无完人”,我们换种思维方式,去恶亦是至善,改错亦为至美。在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获取。最终的检测调试环节,本身就是在践行“过而能改,善莫大焉”的知行观。

对我们电子信息专业的本科生来说,实际能力的培养至关重要,而这种实际能力的培养单靠课堂教学是远远不够的,必须从课堂走向实践。这也是一次预演和准备毕业设计工作。通过课程设计,让我们找出自身状况与实际需要的差距,并在以后的学习期间及时补充相关知识,为求职与正式工作做好充分的知识、能力准备,从而缩短从校园走向社会的心理转型期。

作为整个学习体系的有机组成部分,课程设计虽然安排在两周进行,但并不具有绝对独立的意义。它的一个重要功能,在于运用学习成果,检验学习成果。运用学习成果,把课堂上学到的系统化的理论知识,尝试性地应用于实际设计工作,并从理论的高度对设计工作的现代化提出一些有针对性的建议和设想。检验学习成果,看一看课堂学习与实际工作到底有多大距离,并通过综合分析,找出学习中存在的不足,以便为完善学习计划,改变学习内容与方法提供实践依据。

通过课程设计,我还更加明白了一个真理。时至今日,课程设计基本告成,才切身领悟“实践是检验真理的唯一标准”,才明晓实践出真知。因为在教材上,数字钟不过是由计数器和译码显码器组合而成,也便不以为然搭建电路图,结果电路出现诸多问题,譬如短路开路,EWB中引脚悬空即为低电平,现实中引脚悬空呈现大电阻特性即高电平,不为则不知,无为则无知,实践出真知。

课程设计达到了专业学习的预期目的。在一个星期的课程设计之后,我们普遍感到不仅实际动手能力有所提高,更重要的是通过对设计过程的了解,进一步激发了我们对专业知识的兴趣,并能够结合实际存在的问题在专业领域内进行更深入的学习。

五、 附录

一、元器件明细表

174LS160N 274LS138N

管脚图如下: 管脚图如下:

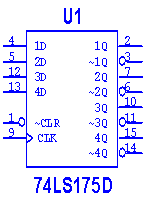

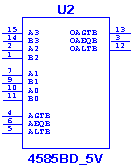

374LS175D 44585BD

管脚图如下: 管脚图如下:

574LS00D 6 电源

7 74LS21D 8 7432N

9 74LS04D 1074LS08D

11 7408N 12蜂鸣器

13数码管 14信号灯

15秒脉冲 16开关

17双选择开关 18开关

二、附图(见A3打印纸)

六、 参考文献

1. 从宏寿.Multisim8仿真与应用实例开发.北京:清华大学出版社,2007

2. 黄智伟.基于NI Multisim的电子电路计算机仿真设计与分析.北京:电子工业出版社,2008

3. 阎石.数字电子技术基础.第四版.北京:高等教育出版社,2010

4. 郭锁利.基于Multisim9的电子系统设计、仿真与综合应用.北京:人民邮电出版社,2008

第二篇:数字电路课程设计实例---24秒计时器

1 计数器概述

1.1篮球竞赛24秒计时器功能

数字电子技术在社会生活中发挥着越来越重要的作用,在生活中有着各种各样的应用。因此课程设计是数字电子技术学习中非常重要的一个环节,它将学生的理论知识和实践能力统一起来,为以后的工作做好准备。

在篮球比赛中,规定了球员的持球时间不能超过24秒,否则就犯规了。本课程设计的“篮球竞赛24秒计时器”可用于篮球比赛中,用于对球员持球时间24秒限制。一旦球员的持球时间超过了24秒,它就自动报警从而判定此球员的犯规。

本课程设计是脉冲数字电路的简单应用,设计了篮球竞赛24秒计时器。此计时器功能齐全,有显示24秒倒计时的功能,同时系统设置外部操作开关,控制计时器的直接清零、启动、暂停、连续功能。而在直接清零时,数码管显示器灭灯,计时器为24秒递减计时其计时间间隔为1秒,计时器递减计时到零时,数码管显示器不灭灯,同时发出光电报警信号。

1.2设计任务及要求

1.2.1 基本要求

(1)显示24秒计时功能。

(2)设置外部操作开关控制计时器直接清零、启动、暂停/连续功能。

(3)在直接清零时,要求数码显示器灭灯。

(4)计时器为24秒递减计时器,其计时间隔为1秒。

(5)递减计时到零时,显示器不能灭灯,同时发出光电报警信号。

(6)秒脉冲由555多谐振荡器给出。

1.2.2设计任务及目标

(1)根据原理图分析各单元电路的功能;

(2)熟悉电路中所用到的各集成块的管脚及其功能;

(3)进行电路的装接、调试、直到电路能达到规定的设计要求;

(4)写出完整、详细的课程设计报告

1.2.3 主要参考器件

555 晶体定时器

74 LS74双D触发器

74LS47译码器

74192双时钟十进制计数器

2 电路设计原理与单元模块

2.1设计原理

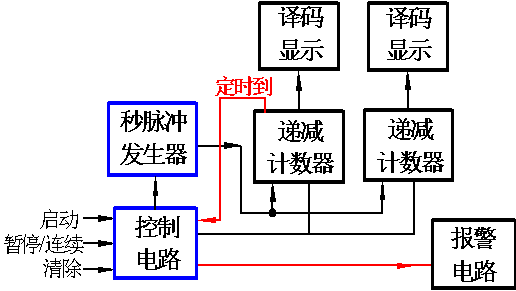

24秒计时器的总体参考方案框图如图2.1所示。它包括秒脉冲发生器、计数器、译码显示电路、报警电路和辅助时序控制电路等五个模块组成。其中计数器和控制电路是系统的主要模块。计数器完成24秒计时功能.而控制电路完成计数器的直接清零、启动计数、暂停/连续计数;译码显示电路的显示与灭灯、定时时间到启动报警等功能。

图2.1 24秒计时器系统设计框图

秒脉冲发生器产生的信号是电路的时钟脉冲和定时标准,但是设计对此信号要求并不太高,故电路可采用555集成电路或由TTL与非门组成的多谐振荡其构成。

译码显示电路由74LS47(译码器)和共阴极七段LED显示器组成。报警电路在试验中可用发光二极管与蜂鸣器代替。

2.2 设计方案

分析设计任务,计数器和控制电路是系统的主要部分。计数器完成24s计时功能,而控制电路具有直接控制计数器的启动计数、暂停/连续计数、译码显示电路的显示和灭灯功能。为了满足系统的设计要求,在设计控制电路时,应正确处理各个信号之间的时序关系。在操作直接清零开关时,要求计数器清零,数码显示器灭灯。

当启动开关闭合时,控制电路应封锁时钟信号CP,同时计数器完成置数功能,译码显示电路显示“24”字样;当启动开关断开时,计数器开始计数;当暂停/连续开关拨在暂停位置上时,计数器停止计数,处于保持状态;当暂停/连续开关拨在连续时,计数器继续递减计数。

2.3 各单元电路的设计

2.3.1 24进制计数器的设计

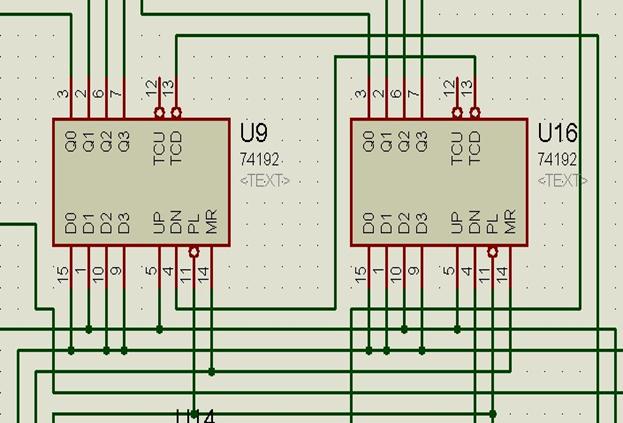

本设计中计数器是由两片74192的8421BCD码递减计数器构成。如图2.2所示。

图2.2 74192双时钟十进制计数器

74192是十进制同步加/减法计数器,采用8421BCD码编码,具有直接清零、异步制数的功能,且有进位 和借位

和借位 输出端。当需要进行多级扩展连接时,只要将前级的

输出端。当需要进行多级扩展连接时,只要将前级的 端接到下一级的CP+端,

端接到下一级的CP+端, 端接到下一级的CP-端即可。详见下面的功能表。

端接到下一级的CP-端即可。详见下面的功能表。

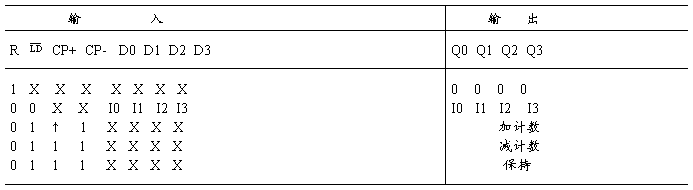

表2.3 74192的功能表

由功能表可以看出,当 =1,CR=0,CPD=1时,如果时钟脉冲加到CPU端,则计数器在预置数的基础上进行加法计数,当计数到9(1001)时,

=1,CR=0,CPD=1时,如果时钟脉冲加到CPU端,则计数器在预置数的基础上进行加法计数,当计数到9(1001)时, 端输出进位下降沿跳变脉冲;当

端输出进位下降沿跳变脉冲;当 =1,CR=0,CPD=1时,如果有时钟脉冲加到CPD端,则计数器在预置数的基础上进行减法计数器。只有当低位1端发出借位脉冲,高位计数器才做减计数。当高,低位计数器全为零时,且CPD为0时,置数端 2,计数器完成并行置数,在CPD端的输入时钟脉冲作用下,计数器进入下一轮循环减计数。

=1,CR=0,CPD=1时,如果有时钟脉冲加到CPD端,则计数器在预置数的基础上进行减法计数器。只有当低位1端发出借位脉冲,高位计数器才做减计数。当高,低位计数器全为零时,且CPD为0时,置数端 2,计数器完成并行置数,在CPD端的输入时钟脉冲作用下,计数器进入下一轮循环减计数。

2.3.2数码显示译码器的设计

在本设计中,根据设计的要求,我使用74LS48译码器来驱动共阴极数码显示管, 74LS48芯片是一种常用的七段数码管译码器驱动器,常用在各种数字电路和系统的显示系统中,下面我就给大家介绍一下这个元件的一些参数与应用技术等资料。74LS47的引脚图和功能表分别如图2.4和表2.5所示。

图2.4 74ls47引脚图

表2.5 74LS47的功能表

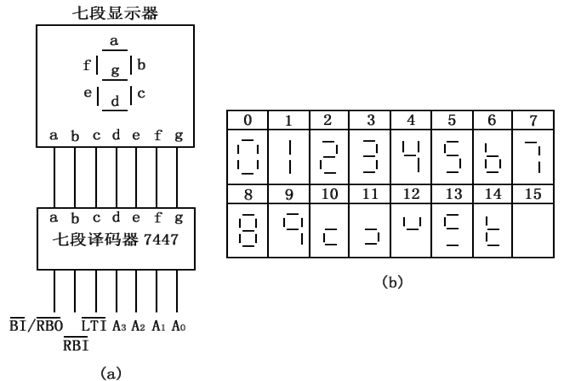

七段译码显示原理图如图2.4(a)所示,图2.4(b)给出了七段显示笔画与0~15共16个数字的对应关系

图2.6 七段数码显示管的引脚图

2.3.3秒脉冲的设计

根据设计要求,本电路需要产生间隔为一秒的时间脉冲,完成正确的计数功能。所以选择555定时器来设计此模块。从而产生标准的秒脉冲。

1.器件特性

555定时器是一种中规模集成电路,外形为双列直插8脚结构,体积很小,使用起来方便。只要在外部配上几个适当的阻容元件,就可以构成史密特触发器、单稳态触发器及自激多谐振荡器等脉冲信号产生与变换电路。它在波形的产生与变换、测量与控制、定时电路、家用电器、电子玩具、电子乐器等方面有广泛的应用。

集成555定时器有双极性型和CMOS型两种产品。一般双极性型产品型号的最后三位数都是555,CMOS型产品型号的最后四位数都是7555.它们的逻辑功能和外部引线排列完全相同。器件电源电压推荐为4.5~12V,最大输出电流200mA以内,并能与TTL、CMOS逻辑电平相兼容。

引脚功能:

Vi1(TH):高电平触发端,简称高触发端,又称阈值端,标志为TH。

Vi2( ):低电平触发端,简称低触发端,标志为

):低电平触发端,简称低触发端,标志为 。

。

VCO:控制电压端。

VO:输出端。

Dis:放电端。

:复位端。

:复位端。

555定时器内含一个由三个阻值相同的电阻R组成的分压网络,产生 VCC和

VCC和 VCC两个基准电压;两个电压比较器C1、C2;一个由与非门G1、G2组成的基本RS触发器(低电平触发);放电三极管T和输出反相缓冲器G3。

VCC两个基准电压;两个电压比较器C1、C2;一个由与非门G1、G2组成的基本RS触发器(低电平触发);放电三极管T和输出反相缓冲器G3。

是复位端,低电平有效。复位后, 基本RS触发器的

是复位端,低电平有效。复位后, 基本RS触发器的 端为1(高电平),经反相缓冲器后,输出为0(低电平)。

端为1(高电平),经反相缓冲器后,输出为0(低电平)。

分析图2.2.3.1的电路:在555定时器的VCC端和地之间加上电压,并让VCO悬空,则比较器C1的同相输入端接参考电压 VCC,比较器C2反相输入端接参考电压

VCC,比较器C2反相输入端接参考电压 VCC ,为了学习方便,我们规定:

VCC ,为了学习方便,我们规定:

当TH端的电压> VCC时,写为VTH=1,当TH端的电压<

VCC时,写为VTH=1,当TH端的电压< VCC时,写为VTH=0。

VCC时,写为VTH=0。

当 端的电压>

端的电压> VCC时,写为VTR=1,当

VCC时,写为VTR=1,当 端的电压<

端的电压< VCC时,写为VTR=0。

VCC时,写为VTR=0。

低触发:当输入电压Vi2< VCC 且Vi1<

VCC 且Vi1< VCC时,VTR=0,VTH=0,比较器C2输出为低电平,C1输出为高电平,基本RS触发器的输入端

VCC时,VTR=0,VTH=0,比较器C2输出为低电平,C1输出为高电平,基本RS触发器的输入端 =0、

=0、 =1,使Q=1,

=1,使Q=1, =0,经输出反相缓冲器后,VO=1,T截止。这时称555定时器“低触发”;

=0,经输出反相缓冲器后,VO=1,T截止。这时称555定时器“低触发”;

保持:若Vi2> VCC 且Vi1<

VCC 且Vi1< VCC,则VTR=1,VTH=0,

VCC,则VTR=1,VTH=0, =

= =1,基本RS触发器保持,VO和T状态不变,这时称555定时器“保持”。

=1,基本RS触发器保持,VO和T状态不变,这时称555定时器“保持”。

高触发:若Vi1> VCC,则VTH=1,比较器C1输出为低电平,无论C2输出何种电平,基本RS触发器因

VCC,则VTH=1,比较器C1输出为低电平,无论C2输出何种电平,基本RS触发器因 =0,使

=0,使 =1,经输出反相缓冲器后,VO=0;T导通。这时称555定时器“高触发”。

=1,经输出反相缓冲器后,VO=0;T导通。这时称555定时器“高触发”。

VCO为控制电压端,在VCO端加入电压,可改变两比较器C1、C2的参考电压。正常工作时,要在VCO和地之间接0.01μF(电容量标记为103)电容。放电管Tl的输出端Dis为集电极开路输出。根据555定时器的控制功能,可以制成各种不同的脉冲信号产生与处理电路电路,例如,史密特触发器、单稳态触发器、自激多谐振荡器等。在此次设计中,采用多谐振荡器来设计。

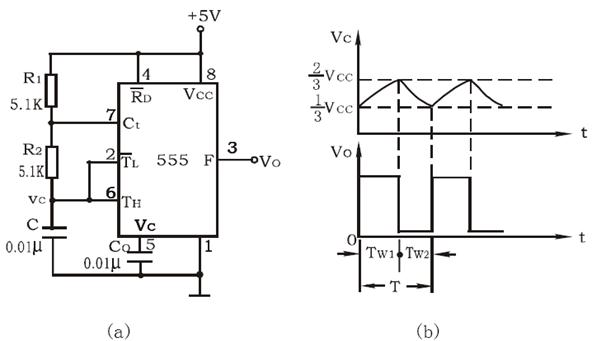

2.自激多谐振荡器

图2.7所示为自激多谐振荡器电路和波形图。自激多谐振荡器用于产生连续的脉冲信号。电路采用电阻、电容组成RC定时电路,用于设定脉冲的周期和宽度。调节RW或电容C,可得到不同的时间常数;还可产生周期和脉宽可变的方波输出。

脉冲宽度计算公式:Tw1=0.7 (R1 +R2) C Tw2=0.7R2 C

振荡周期计算公式:T=0.7 (R1 +2R2) C≈1s

图2.7 自激多谐振荡器电路和波形图

分析方法与单稳态电路相似,但电容器C的充电电阻是R1 +R2 ,放电电阻是R2 。当VC是低电平时,555定时器低触发,VO为高电平,放电管T截止,电容器经(R1 +R2)充电,当充电至VC=VTH> VCC时,电路高触发,输出VO变为低电平,放电管T导通,电容器经R2放电,当放电至VC=VTR<

VCC时,电路高触发,输出VO变为低电平,放电管T导通,电容器经R2放电,当放电至VC=VTR< VCC时,电路又进入低触发,VO变为高电平,如此周而复始,循环不止,输出连续脉冲信号。

VCC时,电路又进入低触发,VO变为高电平,如此周而复始,循环不止,输出连续脉冲信号。

2.3.4时序控制电路

完成计数器的复位、启动计数、暂停/ 继续计数、声光报警等功能。控制电路由IC5 组成。IC5B 受计数器的控制。IC5C、IC5D 组成RS 触发器, 实现计数器的复位、计数和保持“24”、以及声、光报警的功能。操作“清零”开关时,计数器清零。闭合“启动”开关时,计数器完成置数,显示器显示24断开“启动”开关,计数器开始进行递计数。电路图中,当开关S1合上时, =0,74LS192进行置数;当S1断开时, =1,74LS192处于计数工作状态。开关S2是时钟脉冲信号CP的控制电路。当定时时间未到时,74LS192的借位输出信号 2=1,则CP信号受“暂停/连续”开关S2的控制,当S2处于“暂停”位置时,门G3输出为0,门G2关闭,封锁CP 信号,计数器暂停计数;当S2处于连续位置时,门G3输出1,门G2打开,放行CP信号,计数器在CP作用下,继续累计计数。当定时时间到时, 2=0,门G2关闭,封锁CP信号,计数器保持零状态不变。

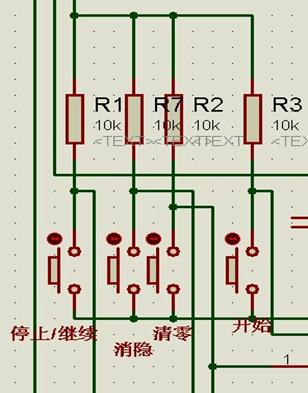

(1) K1: 启动按钮。K1 按下后处于断开位置时, 计数器从“24”递减计数到“00”同时控制电路发出声、光报警信号, 计数器保持“00”状态不变, 处于等待状态。当K1 再次闭合时, 计数器开始计数。

(2) K2: 手动复位按钮。当按下K2 时, 不管计数器工作于什么状态, 计数器立即复位到预置数值, 即“00”。

(3) K3:消隐按钮。按下K3时计数器断电并消除所有计数。

(4) K4: 暂停按钮。当“暂停/ 连续”开关处于“暂停”时, 计数器暂停计数, 显示器保持不变, 当此开关处于“连续”开关, 计数器继续累计计数。控制电路开关如图所示:

图 2.8 控制电路开关图

3 数字电路的仿真与调试

3.1 Protues仿真

首先在Protues中选好元器件,然后连好线,检查线路是否存在错误,如无,则进入了调试的正式阶段,启动调试,观察系统运行的状况是否良好,然后观察现系统的效果是否达到预期的要求,如无,则停止仿真,分析电路中存在的缺陷与错误,改正后再次启动调试,然后再次观察仿真效果是否达到预期的效果,如此循环下去,直到得到满意的仿真效果。到此调试仿真过程结束。以下是本设计的系统仿真结果图:

图3.1 系统仿真结果图

结束语

此次电子线路课程设计让我获益匪浅,使我尝到了将所学的知识用于实践的喜悦和成就感。

此课程设计所设计制作的篮球竞赛24秒计时器是一个实用性设计。此次设计的成不仅为所学的专业课程打下了坚实的基础,提高了我们对分析与解决问题的能力,也在研究与电子爱好追求上做了一个很好的起步。

在这个设计中,我学到了学习理论时学不到的东西,不但锻炼我的动手能力而且巩固我们所学的理论知识,这样实践与理论相结合就可以更快而有效地掌握知识。

本次的设计使我从中学到了一些很重要的东西,那就是如何从理论到实践的转化,怎样将我所学到的知识运用到我以后的工作中去。在大学的课堂的学习只是在给我们灌输专业知识,而我们应把所学的用到我们现实的生活中去,此次的电子时钟设计给我奠定了一个实践基础,我会在以后的学习、生活中磨练自己,使自己适应于以后的竞争,同时在查找资料的过程中我也学到了许多新的知识,在和同学协作过程中增进同学间的友谊,使我对团队精神的积极性和重要性有了更加充分的理解。

最后,感谢老师对我的细心的指导,正是由于老师的细心的辅导和他提供给我们的参考资料,使得我的课程设计能够顺利的完成,同时在课程设计过程中,我们巩固和学习了我们的电子技术知识。相信这对我以后的课程设计和毕业设计将会有很大的帮助!

参考文献

[1]温如坤、高志敏.数字电子技术基础实验[M].湖北汽车工业学院,2004.

[2]阎石.电子技术基础(数字部分)[M].高等教育出版社,2006.

[3]白中英.数字逻辑与数字系统[M].科学出版社,2002.

[4]谢自美.电子线路设计、实验、测试[M].华中科技大学出版社,2001.

[5]朱余钊.电子材料与元件[M].西安电子科技大学出版社,2002.

[6]杨志忠.数字电子技术[M].高等教育出版社,2000.