实验一 四位串行进位加法器的设计

一、实验目的

1. 理解一位全加器的工作原理

2. 掌握串行进位加法器的逻辑原理

3. 进一步熟悉Quartus软件的使用,了解设计的全过程,

二、实验内容

1. 采用VHDL语言设计四位串行进位的加法器

2. 采用画原理图的方法设计四位串行进位加法器

三、实验步骤

1、使用VHDL语言设计

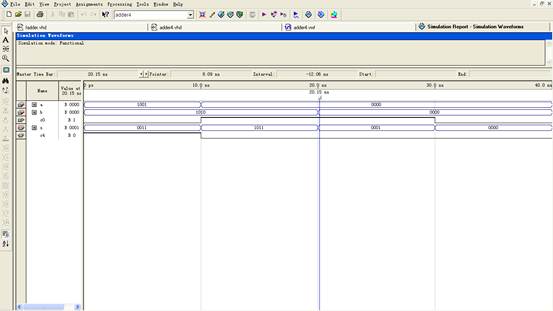

1.打开File—>New Project Wizard输入文件名adder4保存在D盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后保存、编译。打开File—>New—>Other File—>Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。从Assignments—>Settings—>Simulator Settings—>Functional

然后Processing—>Generate Functional Simnlation Netlist —>确定。选择Start Simulation保存最后的波形图,打开File—>close关闭工程。

底层文件:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY fadder IS

PORT

(

a, b,cin : IN STD_LOGIC;

s, co : OUT STD_LOGIC

);

END fadder;

ARCHITECTURE arc1 OF fadder IS

BEGIN

s<=a xor b xor cin;

co<=((a xor b)and cin)or(a and b);

END arc1;

顶层文件:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY adder4 IS

PORT

(

c0: IN STD_LOGIC;

a,b : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

s : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);

c4 : OUT STD_LOGIC

);

END adder4;

ARCHITECTURE arc2 OF adder4 IS

COMPONENT fadder

PORT

(

a, b,cin : IN STD_LOGIC;

s, co : OUT STD_LOGIC

);

END COMPONENT;

SIGNAL carry : STD_LOGIC_VECTOR(3 DOWNTO 1);

BEGIN

u1 : fadder PORT MAP (a=>a(0), b =>b(0),cin=>c0,s=>s(0),co=>carry (1));

u2 : fadder PORT MAP (a=>a(1), b=>b(1),cin=>carry(1),s=>s(1),co=>carry (2));

u3 : fadder PORT MAP (a=>a(2), b=>b(2),cin=>carry(2),s=>s(2),co=>carry (3));

u4 : fadder PORT MAP (a=>a(3),b=>b(3),cin=>carry(3),s=>s(3),co=>c4);

END arc2;

2、使用原理图的方法设计

打开File—>New Project Wizard输入文件名adder4保存在D盘内,打开File—>New—>VHDL File,从模版中选择库的说明,use语句的说明,实体的说明,结构体的说明,编写VHDL代码,然后选择File-->Create/Update-->Create Symbol Files for Current File,选择File-->New-->Other File-->Vector Waveform File,查找引脚,从Edit中选择End Time 输入40、ns 保存。从Assignments—>Settings—>Simulator Settings—>Functional

然后Processing—>Generate Functional Simnlation Netlist —>确定。选择Start Simulation保存最后的波形图,打开File—>close关闭工程。

文件:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

ENTITY fadder IS

PORT

(

Cin,a, b : IN STD_LOGIC;

s, co : OUT STD_LOGIC

);

END fadder;

ARCHITECTURE arc1 OF fadder IS

BEGIN

s<=a xor b xor cin;

co<=((a xor b)and cin)or(a and b);

END arc1;

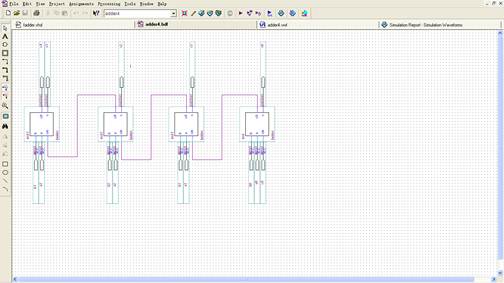

原理图:

四、实验现象

五、 实验体会与收获

问题:Error (10500): VHDL syntax error at adder4.vhd(10) near text ")"; expecting an identifier, or "constant", or "file", or "signal", or "variable"

Error (10500): VHDL syntax error at adder4.vhd(19) near text "COMPONENT"; expecting ";", or an identifier ("component" is a reserved keyword), or "entity"

Error (10396): VHDL syntax error at adder4.vhd(27): name used in construct must match previously specified name "adder4"

Error (10523): Ignored construct adder4 at adder4.vhd(3) due to previous errors

解决办法 :

c4 : OUT STD_LOGIC;

);改为:

c4 : OUT STD_LOGIC);

OUT STD_LOGIC后面无;

收获:第二种方法中只建立熟悉理解一位全加器的工作原理,掌握串行进位加法器的逻辑原理。

第二篇:实验一 四位串行进位加法器的设计

实验一 四位串行进位加法器的设计

一、实验目的

1. 理解一位全加器的工作原理

2. 掌握串行进位加法器的逻辑原理

3. 进一步熟悉Quartus软件的使用,了解设计的全过程,

二、实验内容

1. 采用VHDL语言设计四位串行进位的加法器

2. 采用画原理图的方法设计四位串行进位加法器

三、实验步骤

提示:

使用VHDL语言设计时,项目中包含2个VHDL设计文件,一个是低层的元件即一位全加器;一个是顶层的实体,4位串行进位加法器,其设计采用了例化的语句。注意,此两个设计文件放在同一个文件夹中。

使用原理图的方法设计时,首先将一位全加器设置成可调用的元件,方法是:使用VHDL语言设计一位全加法,选择

File—Create/Update---Create Symbol Files for Current File命令,将当前设计文件变成一个元件符号存盘,以待在高层次设计中调用。之后,建立四位加法器的顶层文件,通过选择File—New 命令并选择Block Diagram/Schematic File选项打开原理图编辑窗口,调出元件,依据设计的原理图连接四位加法器电路图。

四、实验现象

说明功能仿真的波形图

五、 实验体会与收获

说明发现问题以及解决的方法

特别提醒:不要将项目所在的文件夹设在计算机已有的安装目录下,更不要将项目文件夹直接放在Quartus安装目录中。