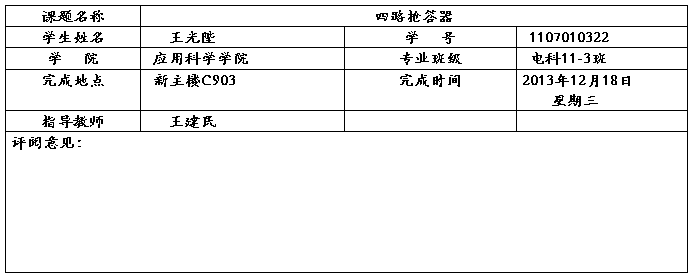

数字电路课程设计报告

题目:四人抢答器

摘要................................................................................................................................ 1

Abstract.................................................................................................................... 1

1、题目要求.................................................................................................................. 2

1.1设计任务.............................................................................................................. 2

2、题目的意义、本人所做的工作及系统的主要功能.............................................. 2

2.1题目的意义......................................................................................................... 2

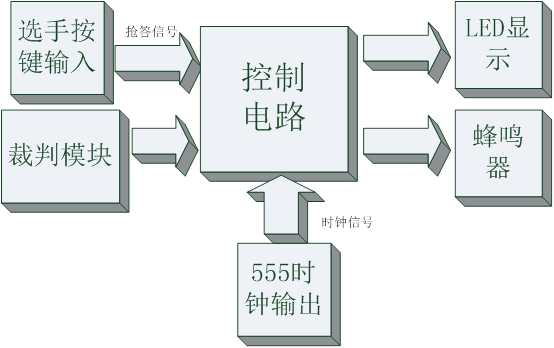

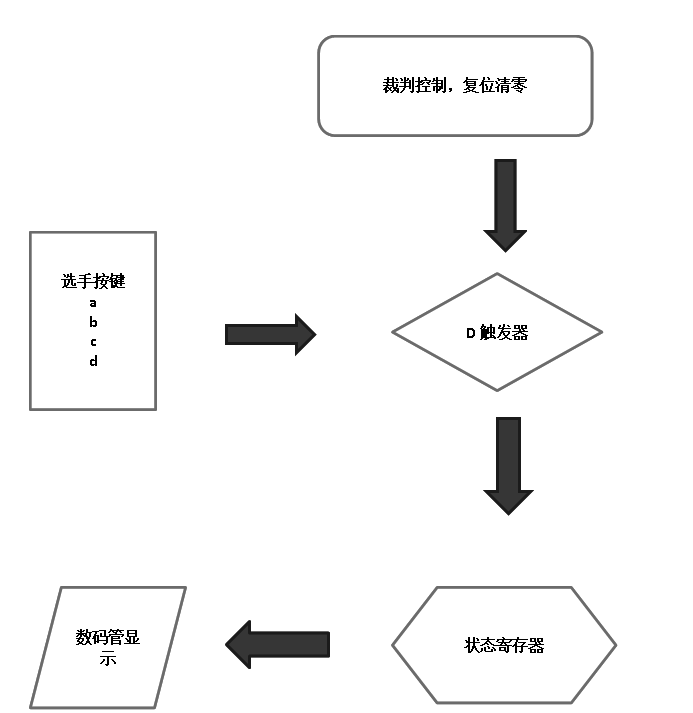

3、系统总体框图.......................................................................................................... 3

4、方案论证.................................................................................................................. 4

5、系统硬件设计.......................................................................................................... 4

5.1选手按键和LED显示电路................................................................................ 4

5.2时钟产生电路...................................................................................................... 5

5.3主持人控制电路.................................................................................................. 6

5.4系统总电路.......................................................................................................... 7

6、系统性能测试与分析.............................................................................................. 7

6.1测试使用的仪器:............................................................................................. 7

6.2性能测试与结果分析......................................................................................... 7

7、调试过程遇到的问题与解决方法.......................................................................... 8

8、课程设计体会.......................................................................................................... 8

9、参考文献.................................................................................................................. 8

四人抢答器

摘要

本系统是一个四人抢答器,主要由按键输入模块、信号控制模块、时钟模块、LED显示模块和报警电路组成。按键输入模块分为四个选手按键和一个支持人控制按键。信号控制模块分别由四D触发器74LS175、双四输入与非门74LS20和四2输入与非门74LS00构成。时钟模块由555组成,输出时钟脉冲为74LS175提供工作时钟。抢答信号由四个选手按键输入,当第一个抢答信号产生并且74LS175的时钟信号上升沿到来后,相应的D触发器输出不同的电平,相应的LED就亮,蜂鸣器报警,而且同时74LS175的时钟脉冲信号被封锁而停止工作,其他三个抢答者的信号输入被封锁,直到主持人再次清除信号为止,从而实现抢答器的功能。

关键词:74LS175 74LS20 74LS00 555 时钟信号

Abstract

This system is a four man vies to answer first device, and the main key input module, signal control module, clock module, LED display module and alarm circuit component. Key input module can be divided into four players keys and a hostess control buttons. Signal control module respectively by four D flip-flop 74 LS175, double four input and 74 LS20 sr and four double input and a 74 LS00 sr. The clock module composition by 555, the clock pulse output for 74 LS175 provide working clock. Vies to answer first signal by four players key input, when the first vies to answer first signal and 74 LS175 clock signal rise after coming along, the corresponding D flip-flop output of different level, the corresponding leds light, a buzzer alarm, and at the same time 74 LS175 clock pulse signal is closed and stop working, and the other three vies to answer first person signal input were closed, until the host again so clear signal, so as to realize the function of the contest.

Keywords: 74 LS175 74 LS20 74 LS00 555 clock signal

1、题目要求

1.1设计任务

使用中小型集成电路和门电路设计四人抢答器要求完成以下功能

? 可同时供4名选手参加比赛,各用一个抢答按钮,按钮编号和选手的编号相对应;

? 用发光二极管显示第一抢答者对应的指示灯亮;并使其余抢答开关不起作用 ;

? 主持人用一个控制开关,用来控制抢答器的清零和抢答开始;

? 使用555定时器产生一个1KHz的周期信号作为时钟信号。

1.2任务要求

? 时钟脉冲产生电路

? 无人抢答时所有的输出为零

? 按下抢答按钮

? 触发器翻转

? 显示电路:LED发光

? 报警电路:蜂鸣器发声

? 脉冲封锁以实现优先判决

? 主持人控制开关控制电路

1.3可选用的器件与元件

? 74LS00、74LS20、74LS175、NE555各1块,发光二极管4支,轻触开关 5个,蜂鸣器1个,电阻、电容任选

2、题目的意义、本人所做的工作及系统的主要功能

2.1题目的意义

抢答器对于我们来说都不陌生,它应用于很多竞赛场合,是参赛者用来抢答的工具,真正实现先抢先答,让最先抢到的选手来回答问题。依靠抢答器来断定抢答的先后,更好地实现公平公正的原则。

2.2本人所做的工作

本人主要负责PCB的设计、制作与调试,其次还有相关电路的仿真。

2.3系统主要功能

本系统可以供四名选手进行抢答,主持人使能抢答器工作后,当第一个选手按下按键时,相应的指示灯亮和蜂鸣器响,同时锁住抢答器,即其他选手按下按键不起作用,从而实现先抢先答的功能,直到主持人重新复位后方可抢答。

3、系统总体框图

系统设计框图如下图所示

系统框图

4、方案论证

方案一:用单片机实现四人抢答器的设计,显然,对于学过单片机的来说是一件十分容易的事情,使用的元件很少,而且编程也比较简单,但是我们觉得使用单片机来实现四人抢答器有点大材小用,所以我们不采用。

方案二: 数字电路抢答器。数字电路抢答器针对性强,并且还可以兼顾实用性,可靠性以及经济成本的合理性。虽然电路使用的元件相对较多,但是它可以发挥个人的设计思路,检查我们所学知识的掌握能力,锻炼我们的动手能力。

综上分析,我们采用方案二来完成这次的设计任务。

5、系统硬件设计

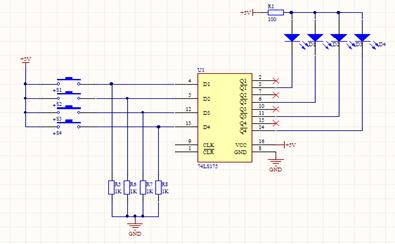

5.1选手按键和LED显示电路

选手按键和LED显示电路如图1所示

图1选手按键和LED显示电路

如图1所示,74LS175是四D触发器,R5、R6、R7、R8用于分压,当任一按键按下时,相应的D输入端为高电平,否则为低电平,其中R5、R6、R7、R8的电阻值理论上不能大于1.35kΩ,否则即使按键没按下时,输入都是高电平,本设计采用1 kΩ。当抢答信号产生并且CLK端时钟的上升沿到来时,对应的Q端口输出低电平,同时相应的LED亮。

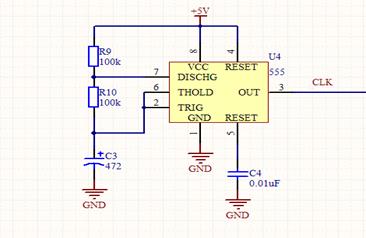

5.2时钟产生电路

图2 NE555时钟产生电路

时钟产生电路如图2所示,主要是由NE555定时器构成的多谐振荡器,其输出的时钟信号CLK为74LS175提供工作时钟,它产生的周期信号的频率计算公式为:

f=1/((R9+2R10)Cln2)(Hz)

先取定R9和R10的标称值为100kΩ,根据题目所要求的输出频率算出电容值,带入数值 f=1000Hz,通过公式计算可得C 3=4700pF。

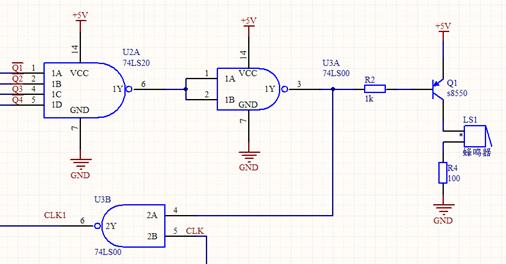

5.3信号控制和报警电路

信号控制和报警电路如图3所示

图3信号控制和报警电路

如图3所示,74LS20为双四输入与非门,74LS00为四2输入与非门,当没有抢答信号输入时,PNP三极管Q1的基极为高电平,此时Q1处于截止,蜂鸣器不响,即U3B与非门的一个输入端为高电平,则CLK1时钟信号能够输入到74LS175,使其工作。当有抢答信号输入时,相应的Q端为低电平,则四输入与非门U2A输出为高电平,而U3A输出为低电平,则Q1导通蜂鸣器响,同时U3B将555输出的时钟信号CLK封锁,不能输入到74LS175,使其停止工作(锁存),则其他选手的抢答信号被封锁,直到主持人再次清除信号为止。

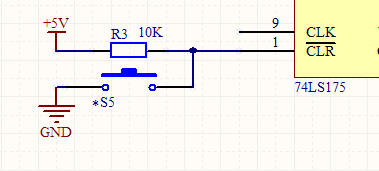

5.3主持人控制电路

主持人控制电路如图4所示

图4主持人控制电路

如图4所示,当按键S5未按下时,CLR端为高电平,清零无效,当按键S5按下时,CLR端为低电平,清零有效,即74LS175回到复位状态。第一次抢答完成后,D触发器处于锁存状态,只有当S5按下后,方可开始新一轮的抢答。

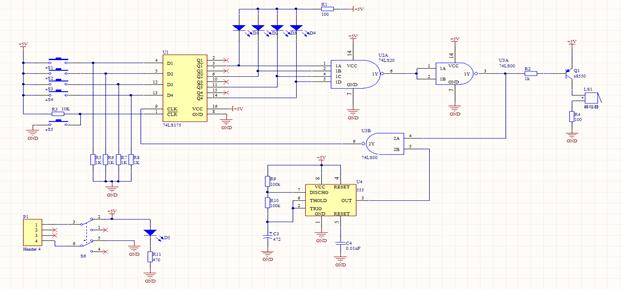

5.4系统总电路

图5 总电路原理图

6、系统性能测试与分析

6.1测试使用的仪器:

数字万用表、直流稳压电源。

6.2性能测试与结果分析

当按下抢答按键时,对应的LED亮,同时蜂鸣器报警,而此时再按下其他抢答按键均无效,当按下复位按键后,LED熄灭,蜂鸣器不响,回到初始状态,又可进行下一轮抢答。

当按下两个或多个抢答按键的时间差很小时,偶尔会出现不止一个LED显示,出现这种情况是正常的,从本系统的设计可知,D触发器是在时钟信号的一个上升沿到来才锁存的,如果在时钟的上升沿还没到来时,已经有多个抢答按键按下时,这样多个抢答信号都被锁存,从而导致不止一个LED显示的情况。要想解决这个问题,除非时钟信号频率无穷大,这是不可能的。但是如果时钟信号的频率足够大,要想实现两个或两个以上抢答信号时间相差很小而被同时锁存很难做到。总的来说,本系统基本上可以实现四人抢答器功能。

7、调试过程遇到的问题与解决方法

进行第一次调试的时候,当按下抢答按键后,发现LED闪烁一下就熄灭了,而且蜂鸣器响了一下又不响了,而又按下抢答按键时,情况一样。而当按下抢答按键不释放时,LED一直亮,蜂鸣器一直响,一释放,LED熄灭,蜂鸣器不响。

根据这种情况可以断定,74LS175、555时钟电路工作正常,问题主要出现在时钟信号锁存那里,未按下抢答按键时,用数字万用表测量Q1基极的电压V1(时钟信号锁存那个与非门的一个输入端)为高电平,当按下抢答按键时,V1先变成低电平又变成高电平。这样就说明74LS20和74LS00都没问题,问题就在PNP三极管Q1那里,经过查阅一些资料,最终找出问题的根源就是Q1基极上的限流电阻R2,出现那种情况是因为电阻R2的阻值取得太小(100Ω),导致基极的电压一直被置为高电平,从而导致时钟信号不能被锁存,即出现上面所说的情况。后来换了一个大些的电阻(1kΩ),问题就解决了,基本可以实现四人抢答器的功能。

8、课程设计体会

本次课程设计,使我受益匪浅,使我加深了对课本理论知识的理解,特别是数字逻辑电路的知识,使我的动手实践能力得到进一步的提高,进一步熟悉电子产品的设计流程。

9、参考文献

【1】徐秀平?数字电路与逻辑设计?北京:电子工业出版社,2010

【2】廖惜春?模拟电子技术基础?武汉:华中科技大学出版社,2008

第二篇:四路抢答器报告

硬件描述语言课程设计报告

哈尔滨理工大学

电子科学与技术系

摘要

Verilog HDL本身是一门比较复杂的语言,语法结构丰富。在王老师所教书中介绍了基于Verilog HDL的数字设计的基本原理和方法,重点是电路设计。为更好的将所学Verilog HDL语言的理论知识与实际应用结合起来,学会分析、解决实际的数字电路问题,锻炼独立进行某些数字应用系统的开发设计工作能力,我们在老师的指导下完成了此次项目设计。

本设计题目为四路抢答器电路,用Verilog HDL语言编写软件实现四路抢答功能。裁判发出开始信号后抢答有效(裁判使用拨码开关),一人抢答成功后其他人抢答无效直至裁判复位此状态后方可继续抢答(选手使用按键),同时使用数码管显示出选手的编号。

四路抢答器电路设计的主要问题在于如何实现各个模块的正确分配,进而使设计出的电路更加符合要求。为了使各个模块能够正确分配,在程序开始设计之前,必须反复推敲本组的设计方案并设计好各个模块的方框图。根据实验题目要求并进行电路的仿真,电路的设计应包括2个模块,即实例化模块和抢答模块。

此次设计四路抢答器电路的目的就是让同学们在学习Verilog HDL理论的基础上,通过对题目要求的分析进一步实现实际电路的设计,使我们不但能够将课堂上学到的理论知识与实际应用结合起来,而且能够对分析、解决实际的数字电路问题进一步加深认识,为今后能够独立进行某些数字应用系统的开发设计工作打下一定的基础。

【关键词】Verilog HDL,四路抢答器,模块,数码管显示,电路设计

第一部分 系统的设计

1.1、设计要求

(1)裁判发出开始信号后抢答有效。

(2)设选手及裁判按钮,选手使用按键,裁判使用拨码开关。

(3)一人抢答成功后,其他人再抢答无效,裁判复位此状态后方可继续抢答。

(4)使用数码管显示选手的编号。

1.2、设计目标

(1)我们在课本上学习了相关的基础知识,所以需要进一步对实际题目进行程序编写,以巩固所学知识,还可以发现自身不足。

(2)程序编好后还需要在实验室调试电路,观察实验现象,进一步熟悉相关仪器设备的使用。

(3)通过完成四人抢答器电路设计,使学生不但能够将课堂上学到的理论知识与实际应用结合起来,而且能够对分析、解决实际的数字电路问题进一步加深认识,为今后能够独立进行某些数字应用系统的开发设计工作打下一定的基础。

(4)培养综合运用知识和独立开展实践创新的能力。

(5)规范化训练学生撰写技术研究报告,提高书面表达能力。

1.3、设计方法

(1)仔细阅读课程设计题目要求,思考实现电路所需知识以及方法。

(2)遇到本组内解决不了的问题,及时和其他小组交流或询问老师。

(3)将任务分成若干模块,查阅相关论文资料,分模块调试和完成任务。

(4)通过完成该项任务,总结所学知识。

1.4、实验设计结果

(1)对所写程序进行编译无误。

(2)在实验室对电路进行引脚分配和仿真,通过DE2开发板观察实验现象。

(3)裁判发出开始信号后抢答有效。

(4)一人抢答成功后,其他人再抢答无效,裁判复位此状态后方可继续抢答。

(5)使用数码管显示选手的编号。

第二部分 实验设计部分

2.1、设计概述

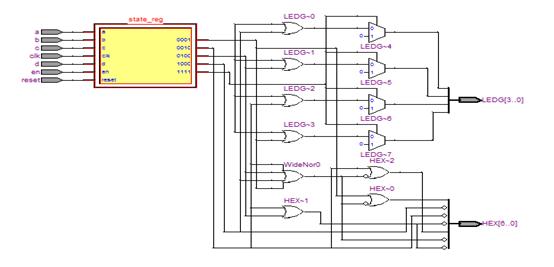

本次课程设计的四路抢答器要求实现以下功能,即裁判发出开始信号后抢答有效,设裁判及选手按钮,裁判使用拨码开关而选手使用按键。一人抢答成功后,其他人再抢答无效,裁判复位此状态后方可继续抢答,使用数码管显示选手的编号。

抢答器的核心部分为巧妙地利用D触发器的反馈,在检测到第一个上升沿时将按键(未按下时接低电平)接入的与门锁住,以保证与门只有一个上升沿输出,从而实现“最先按下按键的选手抢答成功,此后其他人抢答无效”。在与门输出上升沿的同时检测按键,用来确定是哪个选手抢答,用寄存器存储抢答选手的信息,最后数码管显示出抢答选手的编号。裁判对当时状态复位,则抢答重新开始,其原理同上。

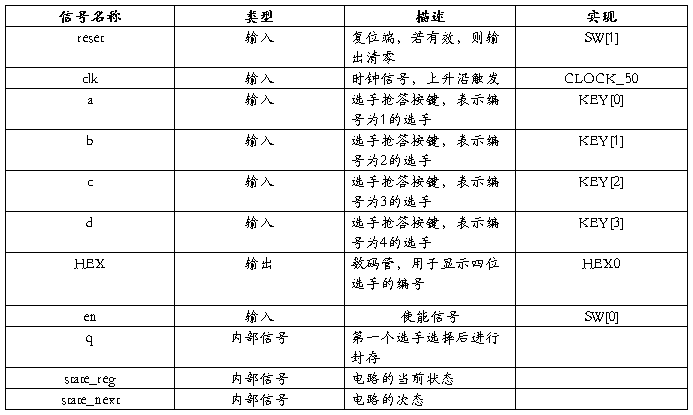

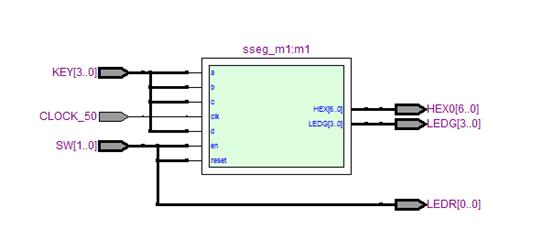

本设计要求采用DE2开发板设计并完成四路抢答器的设计,设计中采用DE2开发板上的开关及按键模拟裁判及选手的按键,通过七段显示译码器显示出选手编号的数码管。根据以上设计要求及分析,设计出系统输入输出信号如下表所示。

2.2、设计框图

2.3 、电路设计

(1)实例化

本次课程设计要求采用实验室中的DE2开发板完成四路抢答器的设计,这就要求采用DE2开发板上的开关及按键模拟选手及裁判的按键,并通过七段显示译码器模拟显示选手编号的数码管。这些要求可以通过模块实例化来实现。模块实例程序如下:

module qiengdaqi

(

input wire [1:0]SW,

input wire CLOCK_50,

input wire [3:0]KEY,

output wire[6:0]HEX0,

ouput wire[3:0]LEDG,

output wire[0:0]LEDR

);

assign LEDR=SW[0]

sseg_m1 m1(.clk(CLOCK_50),.en(SW[0]),.reset(SW[1]),.a(KEY[0]),.b(KEY[1]),

.c(KEY[2]),.d(KEY[3]),.HEX(HEX0),.LEDG(LEDG));

endmodule

(2)抢答模块

抢答模块要具有第一信号鉴别、锁存功能。第一信号鉴别锁存的关键是准确判断出第一抢答者并将其锁存,在得到第一信号后,将输入端封锁,使其他组的抢答信号无效,用触发器实现。设置抢答按钮in_a、in_b、in_c、in_d,裁判复位信号reset。reset=0时,第一信号鉴别、锁存电路以及电路复位;reset=1时,开始抢答,由第一信号鉴别锁存电路形成第一抢答信号,并通过数码管显示出抢答者的编号。抢答模块程序如下:

module sseg_m1

(

input wire clk,en,reset,

input wire a,b,c,d,

output reg [6:0]HEX,

output wire [3:0] LEDG

);

reg[3:0] state_reg,state_next;

reg q;

assign LEDG=(q)? 4'b0:state_reg;

always@(posedge clk,posedge reset)

begin

if(reset)

begin

state_reg<=4'b1111;

end

else

state_reg<=state_next;

end

always@*

begin

if(state_reg==4'b1111)

q=1'b1;

else

q=1'b0;

if((!a)&(q)&en)

state_next=4'b0001;

else if((!b)&(q)&en)

state_next=4'b0010;

else if((!c)&(q)&en)

state_next=4'b0100;

else if((!d)&(q)&en)

state_next=4'b1000;

else

state_next=state_reg;

end

always @*

begin

case(state_reg)

4'b0001:HEX[6:0]=7'b1111001;

4'b0010:HEX[6:0]=7'b0100100;

4'b0100:HEX[6:0]=7'b0110000;

4'b1000:HEX[6:0]=7'b0011001;

default:HEX[6:0]=7'b1111111;

endcase

end

endmodule

第三部分 设计仿真

(1)双击Quartus II软件快捷图标进入Quartus II集成开发环境,新建工程项目文件db,并在该项目下新建Verilog源程序文件qiangdaqi.v,输入上面的程序代码并保存。

(2)然后为该工程项目选择目标器件并对相应的管脚进行锁定。

(3)对该工程文件进行编译处理,若在编译过程中发现错误,找出并更正错误直至成功为止。

(4)将DE2开发板下载电缆端接到PC机,打开工作电源,执行下载命令把程序下载到DE2开发板上,通过KEY[0]到KEY[4]抢答按键按下后,由裁判员根据答题情况,通过控制按键操作,这样就可以看到数码管上的选手编号。

第四部分 调试运行

在编译调试运行的过程中,出现了不少问题。

(1)由于基础知识学习不够扎实,同时在两个always语句中队同一个变量赋值,由于各个always块是并行执行的,在编译过程中出现了错误。最后将两个always块合并为一个,避免了这个问题的出现。

(2)抢答成功后数码管不能正确显示其组号。原因在于所编程序中数码管数字编写出现错误,改正后,电路正常。

第五部分 仿真结果

(1) 复位端有效,清零,禁止抢答

(2) 编号为1的选手抢答成功

(3) 编号为2的选手抢答成功

(4) 编号为3的选手抢答成功

(5) 编号为4的选手抢答成功

第六部分 心得体会

通过一个星期的讨论、实践,加深了对EDA的了解,我更加熟练的掌握了QuartusⅡ的使用,并产生了浓厚的兴趣。特别是编译过程中,当错误一个个减少时,特别的兴奋。

这次项目设计选择了抢答器,刚开始进行分析,分为几个部分,然后每一部分分开编写,最后汇总于一个模块当中,不会太难。但是接下来程序编写过程中由于需要定义多个变量,弄的混乱不堪。而后先将所有用到的变量及其代表的含义先写下来,编写程序过程中一一对照才清楚了很多。

由于理论学习与实际运用存在太大的差别,在设计过程中错误不断,只能一点一点的进行修改。直到最后完整的实现了四人抢答器的基本功能。

在设计中遇到问题是在所难免的,但这是我们所必须面对的,有问题才能去解决问题,解决问题才能提高。从中学会的不止是怎样解决实际问题,更多的是遇到问题时该怎么思考。

通过这次项目设计,我更加理解了理论与实际相结合的重要性。只有理论知识是还远远不够,只有把所学的理论知识与具体问题结合起来,才能真正的应用,不断提高自己动手能力、思考的能力和团队合作能力。

总的来说,对这次设计抢答器还是比较满意的,即使没有完全实现预期效果,有些许遗憾,但至少是自己的成果。一周的时间,积累了经验,增强了实验素养,受益匪浅。

参考文献

[1] 夏宇闻. Verilog 《数字系统设计教程》.北京. 北京航空航天大学出版社.2008.6

[2] 张延伟,杨金岩,葛爱.《Verilog HDL 程序设计实例详解》.北京.人民邮电出版社

[3] 王伟.《Verilog HDL程序设计与应用》.北京. 人民邮电出版社

[4] 张亦华 延明 编著. 数字电路EDA入门---VHDL程序实例集,北京邮电大学出版社 2003