信息工程学院

EDA课程设计报告书

题目: 七人表决器

专 业:电子信息科学与技术_

班 级: 0309410

学 号: 030941008

学生姓名: 罗勋义

指导教师: 袁老师

20## 年 05月 10日

信息工程学院课程设计任务书

摘要

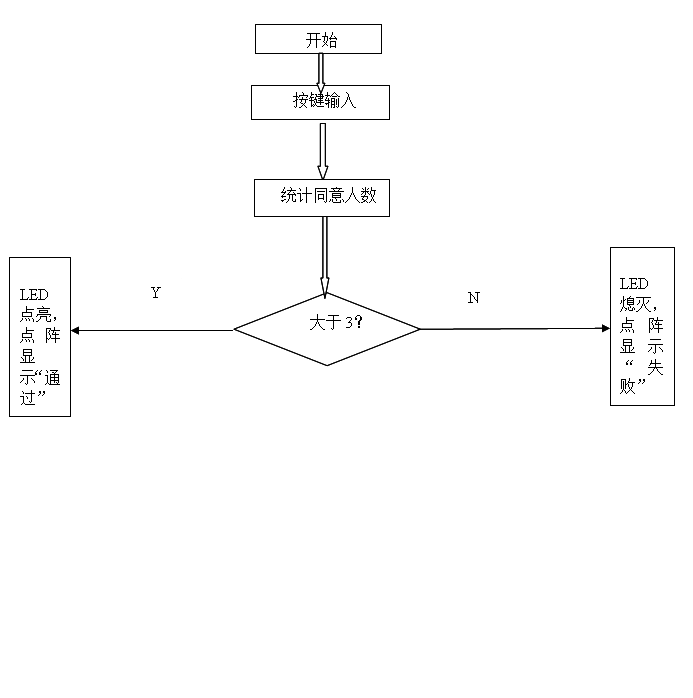

所谓表决器就是对于一个行为,由多个人投票,如果同意的票数过半,就认为此行为可行;否则如果否决的票数过半,则认为此行为无效。

七人表决器顾名思义就是由七个人来投票,当同意的票数大于或者等于4人时,则认为同意;反之,当否决的票数大于或者等于4人时,则认为不同意。实验中用7个拨挡开关来表示七个人,当对应的拨挡开关输入为‘1’时,表示此人同意;否则若拨挡开关输入为‘0’时,则表示此人反对。表决的结果用一个LED和点阵显示表示,若表决的结果为同意,则LED被点亮,点阵显示“通过”;否则,如果表决的结果为反对,则LED不会被点亮,点阵显示“失败”。

关键词:七人,表决器,点阵

目录

1 任务提出与设计思路................................................................................................ 5

1.1 设计要求........................................................................................................ 5

1.2设计思路......................................................................................................... 5

2 总体设计.................................................................................................................... 6

3 详细设计及仿真........................................................................................................ 7

3.1点阵原理......................................................................................................... 7

3.2 电路组成与管脚分配.................................................................................. 8

3.3 VHDL源程序................................................................................................. 10

3.4 EP3C40平台仿真......................................................................................... 14

4 总结.......................................................................................................................... 15

参考文献...................................................................................................................... 16

1 任务提出与设计思路

近十年由于超大规模集成电路和软件技术的快速发展,使数字系统集成到一片集成电路内成为可能,在小规模数字集成电路就要淘汰的今天,作为一个电子技术工程技术人员不懂VHDL语言和CPLD、FPGA器件设计就象在计算机时代不会使用计算机一样可怕。本次任务就是在此社会背景下提出,设计一个七人表决器。

1.1 设计要求

1).能够完成七人表决的功能,并且直观的显示结果:决议通过LED亮,点阵显示“通过”,否则LED灭,点阵显示“失败”

2).能够显示赞成方的人数,

3).设置投票有效时间,超过四人同意则表示决议通过

4)逻辑设计要求:用七个开关作为表决器的七个输入变量,逻辑“1”时表示“赞同”,逻辑“0”时表示“不赞同”

1.2设计思路

1.使用Altera的Cyclone III器件,FPGA型号为EP3C40F780C8;开发平台为Quartus II 8.1;

2.使用7个拨动开关用以进行表决,开关闭合时表示同意,断开时表示不同意;

3.使用1个LED和点阵用以显示最终结果。LED亮起,点阵显示“通过”,表示决议通过,否则LED灭,点阵显示“失败”;

4.使用一个七段数码管用以显示同意的人数;

2 总体设计

总体设计框图如图2-1所示。

图2-1组成框图

3 详细设计及仿真

3.1点阵原理

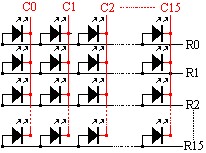

16*16扫描LED点阵的工作原理与8位扫描数码管类似,只是显示的方式与结果不一样而已。16*16点阵由256个LED通过排列组合而形成。单个的LED的电路如下图3-1所示:

16*16扫描LED点阵的工作原理与8位扫描数码管类似,只是显示的方式与结果不一样而已。16*16点阵由256个LED通过排列组合而形成。单个的LED的电路如下图3-1所示:

图3-1 单个LED电路图

16*16点阵也就是由16行和16列的LED组成,其中每一行的所有16个LED的Rn端并联在一起,每一列的所有16个LED的Cn端并联在一起。通过给Rn输入一个高电平,也就相当于给这一列所有LED输入了一个高电平,这时只要某个LED的Cn端输入一个低电平时,对应的LED就会被点亮。具体的电路如下图3-2所示:

16*16点阵也就是由16行和16列的LED组成,其中每一行的所有16个LED的Rn端并联在一起,每一列的所有16个LED的Cn端并联在一起。通过给Rn输入一个高电平,也就相当于给这一列所有LED输入了一个高电平,这时只要某个LED的Cn端输入一个低电平时,对应的LED就会被点亮。具体的电路如下图3-2所示:

图3-2 16*16点阵电路原理图

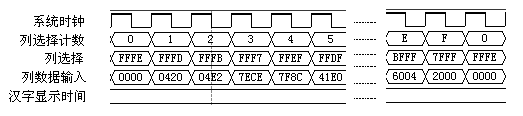

要显示一个汉字,在我们选中第一列后,根据要显示汉字的第一列中所需要被点亮的点对应的Rn置为高电平,则在第一列中需要被点亮的点就会被点亮。依此类推,然后根据人眼的视觉原理,将每一列显示的点的间隔时间设为一定的值,那么我们就会感觉显示一个完整的不闪烁的汉字。显示一个汉字所需要的时序图如图3-3所示:

图3-3 显示时序图

在上图中,在系统时钟的作用下,首先选取其中的一列,将数据输入让这列的LED显示其数据(当为高电平时LED发光,否则不发光)。然后选取下一列来显示下一列的数据。当完成一个16*16点阵的数据输入时,即列选择计数到最后一列后,再从第一列开始输入相同的数据。这样只要第一次显示第一列的数据和第二次显示第一列的数据的时间足够短,那么人的眼睛就会看到第一列的数据总是显示的,而没有停顿现象。同样的道理其它列也是这样,直到显示下一个汉字。

3.2 电路组成与管脚分配

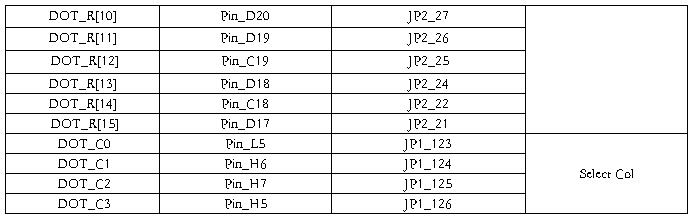

16*16点阵电路图如图3-4所示。整个设计与FPGA的管脚连接如表3-1和表3-2所示。

图3-4 16*16点阵电路图

表3-1 16X16点阵与FPGA的管脚连接表

表3-2 端口管脚分配表

3.3 VHDL源程序

源程序如下:

-------------------------------------

-- Title: 七人表决器 --

----------------------------------------

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

--------------------------------------------------------------------

entity luo is

port(

k1,K2,K3,K4,K5,K6,K7 : in std_logic; --输入:7个人

ledag : out std_logic_vector(7 downto 0); --数码管显示

m_Result : out std_logic ; --表决结果

clk : in std_logic; --时钟输入

keyc : out std_logic_vector(3 downto 0); --点阵列控制

keyr : out std_logic_vector(15 downto 0) --点阵行显示

);

end luo;

--------------------------------------------------------------------

architecture behave of luo is

signal K_Num : std_logic_vector(2 downto 0);

signal K1_Num,K2_Num: std_logic_vector(2 downto 0);

signal K3_Num,K4_Num: std_logic_vector(2 downto 0);

signal K5_Num,K6_Num: std_logic_vector(2 downto 0);

signal K7_Num : std_logic_vector(2 downto 0);

signal cdount : std_logic_vector(3 downto 0);

signal dount : std_logic_vector(8 downto 0);

signal dount1 : std_logic_vector(16 downto 0);

signal S : std_logic;

begin

process(K1,K2,K3,K4,K5,K6,K7,clk)

begin

if Clk'event and Clk='1' then

dount1<=dount1+1;

if dount1<65535 then

K1_Num<='0'&'0'&K1;

K2_Num<='0'&'0'&K2;

K3_Num<='0'&'0'&K3;

K4_Num<='0'&'0'&K4;

K5_Num<='0'&'0'&K5;

K6_Num<='0'&'0'&K6;

K7_Num<='0'&'0'&K7;

else

K1_Num<='0'&'0'&'0';

K2_Num<='0'&'0'&'0';

K3_Num<='0'&'0'&'0';

K4_Num<='0'&'0'&'0';

K5_Num<='0'&'0'&'0';

K6_Num<='0'&'0'&'0';

K7_Num<='0'&'0'&'0';

end if;

end if;

end process;

process(K1_Num,K2_Num,K3_Num,K4_Num,K5_Num,K6_Num,K7_Num) --计算表决同意人数

begin

K_Num<=K1_Num+K2_Num+K3_Num+K4_Num+K5_Num+K6_Num+K7_Num;

end process;

process(K_Num,cdount,S) --根据人数输出结果

begin

if(K_Num>3) then

m_Result<='1';

if S='0' then

case cdount is

when "0000"=>keyr<="1111111110111111"; --列显示通

when "0001"=>keyr<="1011111110111101";

when "0010"=>keyr<="1101111110110001";

when "0011"=>keyr<="1110000000110011";

when "0100"=>keyr<="1101111111111111";

when "0101"=>keyr<="1011111111111111";

when "0110"=>keyr<="0100000000001110";

when "0111"=>keyr<="0111101101101110";

when "1000"=>keyr<="0111101101101010";

when "1001"=>keyr<="0100000000000110";

when "1010"=>keyr<="0111101101101010";

when "1011"=>keyr<="0101101101101100";

when "1100"=>keyr<="0110000000000110";

when "1101"=>keyr<="0011111111101111";

when "1110"=>keyr<="1011111111111111";

when "1111"=>keyr<="1111111111111111";

when others=>keyr<="1111111111111111";

end case;

elsif S='1' then

case cdount is

when "0000"=>keyr<="1111111110011111"; --列显示过

when "0001"=>keyr<="1011111110011101";

when "0010"=>keyr<="1100000000010001";

when "0011"=>keyr<="1000000000010011";

when "0100"=>keyr<="0001111111111111";

when "0101"=>keyr<="0011111111100111";

when "0110"=>keyr<="0011111110100111";

when "0111"=>keyr<="0011111000100111";

when "1000"=>keyr<="0011001001100111";

when "1001"=>keyr<="0010001111100111";

when "1010"=>keyr<="0010011111100111";

when "1011"=>keyr<="0010000000000000";

when "1100"=>keyr<="0010000000000000";

when "1101"=>keyr<="0011111111100111";

when "1110"=>keyr<="1001111111100111";

when "1111"=>keyr<="1001111111111111";

when others=>keyr<="1111111111111111";

end case;

end if;

else

m_Result<='0';

if S='0' then

case cdount is

when "0000"=>keyr<="1111111011111111"; --列显示失

when "0001"=>keyr<="0111111010111111";

when "0010"=>keyr<="0111111011011111";

when "0011"=>keyr<="1011111011100001";

when "0100"=>keyr<="1101111011101111";

when "0101"=>keyr<="1110111011101111";

when "0110"=>keyr<="1111001011101111";

when "0111"=>keyr<="1111110000000000";

when "1000"=>keyr<="1111001011101111";

when "1001"=>keyr<="1110111011101111";

when "1010"=>keyr<="1101111011101111";

when "1011"=>keyr<="1101111011100111";

when "1100"=>keyr<="1011111011101111";

when "1101"=>keyr<="0011111001111111";

when "1110"=>keyr<="1011111011111111";

when "1111"=>keyr<="1111111111111111";

when others=>keyr<="1111111111111111";

end case;

elsif S='1' then

case cdount is

when "0000"=>keyr<="0111111111111111"; --列显示败

when "0001"=>keyr<="1011100000000001";

when "0010"=>keyr<="1100111111111101";

when "0011"=>keyr<="1111000000000101";

when "0100"=>keyr<="1110111111111101";

when "0101"=>keyr<="1001100000000000";

when "0110"=>keyr<="0111111111111101";

when "0111"=>keyr<="1011111111011111";

when "1000"=>keyr<="1101111111101111";

when "1001"=>keyr<="1110100000110000";

when "1010"=>keyr<="1111011111110111";

when "1011"=>keyr<="1110100111110111";

when "1100"=>keyr<="1101111000000111";

when "1101"=>keyr<="1001111111110011";

when "1110"=>keyr<="1101111111110111";

when "1111"=>keyr<="1111111111111111";

when others=>keyr<="1111111111111111";

end case;

end if;

end if;

end process;

process(K_Num) --根据人数数码管显示表决通过人数

begin

case K_Num is

when "000"=>ledag<="00111111";

when "001"=>ledag<="00000110";

when "010"=>ledag<="01011011";

when "011"=>ledag<="01001111";

when "100"=>ledag<="01100110";

when "101"=>ledag<="01101101";

when "110"=>ledag<="01111101";

when "111"=>ledag<="00000111";

when others=>ledag<="00000000";

end case;

end process;

process(clk) --显示时序控制

begin

if clk'event and clk='1' then

dount<=dount+1;

if dount=255 then

if S='1' then

S<='0';

else

S<='1';

end if;

else

S<=S;

end if;

if cdount<15 then

cdount<=cdount+1;

else

cdount<="0000";

end if;

end if;

keyc<=cdount;

end process;

end behave;

3.4 EP3C40平台仿真

1. 在Quartus中打开已经建好的工程文件;

2. 按要求选择设备并且分配管脚,重新编译,连接实验板的电源线与下载线,下载程序文件

3. 分别拨动开关sw0到sw6,看是否能够满足基本要求。

4. 调试程序直到能够完成设计的要求。

5. 最后结果:实验板启动默认可以显示表决结果为'"失败"。任意拨动4个开关后可以正确显示"通过"。

4 总结

通过本次设计,我进一步熟悉了Altera公司产品和软件QUARTUSⅡ及其它相关软件的使用,学会了自己设计简单的数字系统。同时,经过这次设计,我回顾了以前学过的知识,加深了对所学知识的了解和融会贯通,此外,此次设计也提起了我对硬件描述语言的兴趣,深刻认识到一个电子技术工程技术人员如果不懂VHDL语言和CPLD、FPGA器件设计,将会是多么悲哀。

在此次设计过程中,由于对设计平台的不了解,对VHDL语言不够熟悉,因此出现了不少的问题,但在同学的帮助,老师的指导下,总算是差强人意的完成了。总的来说,此次设计还是很有收获的。

参考文献

1.顾斌.数字电路EDA设计.西安电子科技大学出版社,2004.

2.李国洪,等.可编程器件EDA设计与实践,机械工业出版社,2004.

3.潘松,等.EDA技术及其应用,清华大学出版社,2007.

4.王振红,等.VHDL数字电路设计与应用实践教程(第二版),机械工业出版社,2005.

5.赵明富,等.EDA技术基础,北京大学出版社.