北 华 航 天 工 业 学 院

《EDA技术综合设计》

课程设计报告

报告题目: 数字秒表

作者所在系部: 电子工程系

作者所在专业: 通信工程

作者所在班级: B11232

作 者 姓 名 : 院文乐(35),张涛(36)

指导教师姓名: 崔瑞雪

完 成 时 间 : 2013.12.9---2013.12.12

内容摘要

秒表共有6个输出显示,分别为百分之一秒、十分之一秒、秒、十秒、分、十分,所以共有6个计数器与之相对应,6个计数器的输出全都为BCD码输出,这样便于和显示译码器的连接。当计时达60分钟后,蜂鸣器鸣响10声。

除此之外,整个秒表还需有一个启动信号和一个归零信号,以便秒表能随意停止及启动。

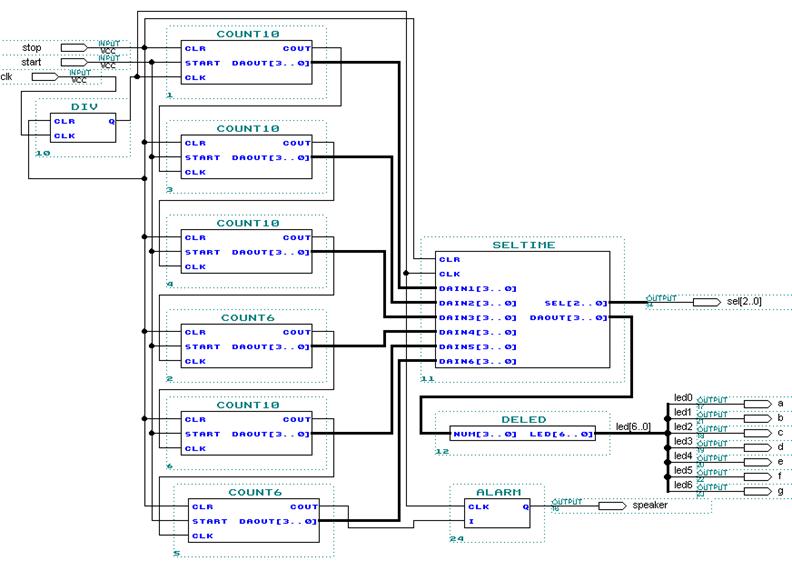

秒表的逻辑结构较简单,它主要由显示译码器、分频器、十进制计数器、六进制计数器和报警器组成。

四个10进制计数器:用来分别对百分之一秒、十分之一秒、秒和分进行计数;

两个6进制计数器:用来分别对十秒和十分进行计数;

分频器:用来产生100HZ计时脉冲;

显示译码器:完成对显示的控制。

根据电路持点,用层次设计概念将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口。

按适配划分后的管脚定位,同相关功能块硬件电路接口连线。

用VHDL语言描述所有底层模块。

清零信号为异步清零。

当最高位记到6时 停止计数 显示译码器全部显示零,并发出十声警报声。按下复位按钮后继续计数。

目 录

一、 系统组成框图……………………………………………………5

二、 各模块原理及其程序……………………………………………5

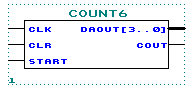

1、 六进制计数器……………………………………………………6

2、 十进制计数器 …………………………………………………6

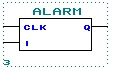

3、 蜂鸣器 ………………………………………………………7

4、 译码器…………………………………………………………7

5、 控制器…………………………………………………………8

6、 分频器………………………………………………………9

7、 元件例化………………………………………………………9

三、 系统仿真 ………………………………………………………10

1、 六进制计数器 …………………………………………………10

2、 十进制计数器 …………………………………………………11

3、 蜂鸣器 ………………………………………………………11

4、 译码器 ………………………………………………………11

5、 控制器 ………………………………………………………11

四、心得体会 ……………………………………………………11

五、参考文献……………………………………………………12

课程设计任务书

设计过程

一.系统组成框图

二.各模块及的原理及其程序

二.各模块及的原理及其程序

(1)六进制计数器

library ieee;

(1)六进制计数器

use ieee.std_logic_1164.all;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity count6 is

port (clk,clr,start:in std_logic;

daout:out std_logic_vector(3 downto 0);

cout:out std_logic );

end count6;

architecture behave of count6 is

signal temp:std_logic_vector(3 downto 0);

begin

process(clk,clr)

begin

if clr='1' then temp<="0000";

cout<='0';

elsif clk'event and clk='1' then

if start='1'then

if temp>="0101" then temp<="0000";

cout<='1';

else temp<=temp+1; cout<='0';

end if;

end if;

end if;

end process;

daout<=temp;

end behave;

(2)十进制计数器

(2)十进制计数器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity count10 is

port(

clr,start,clk:in std_logic;

cout:out std_logic;

daout:buffer std_logic_vector(3 downto 0));

end count10;

architecture behave of count10 is

begin

process(clr,start,clk)

begin

if clr='1' then daout<="0000";

elsif ( clk'event and clk='1') then

if start='1' then

if daout="1001" then daout<="0000";cout<='1';

else daout<=daout+1;cout<='0';

end if;

end if;

end if;

end process;

end behave;

(3)蜂鸣器

library ieee;

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity alarm is

port(clk,I:in std_logic;

q:out std_logic

);

end alarm;

architecture ar of alarm is

signal n:integer range 0 to 20;

signal q0:std_logic;

begin

process(clk)

begin

if clk'event and clk='1'

then

if i='0' then q0<='0';

n<=0;

elsif n<=19 and i='1' then

q0<=not q0;

n<=n+1;

else q0<='0';

end if;

end if;

end process;

q<=q0;

end ar;

(4)译码器

library ieee;

library ieee;

use ieee.std_logic_1164.all;

entity deled is

port(num:in std_logic_vector(3 downto 0);

led:out std_logic_vector(6 downto 0));

end deled ;

architecture a of deled is

begin

process(num)

begin

case num is

when"0000"=>led<="0111111";

when"0001"=>led<="0000110";

when"0010"=>led<="1011011";

when"0011"=>led<="1001111";

when"0100"=>led<="1100110";

when"0101"=>led<="1101101";

when"0110"=>led<="1111101";

when"0111"=>led<="0100111";

when"1000"=>led<="1111111";

when"1001"=>led<="1101111";

when others=>led<="0000000";

end case;

end process;

end a;

(5)控制器

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity seltime is

port(clr,clk: in bit;

dain0,dain1,dain2,dain3,dain4,dain5: in std_logic_vector(3 downto 0);

sel: out std_logic_vector(2 downto 0);

daout: out std_logic_vector(3 downto 0));

end seltime;

architecture a of seltime is

architecture a of seltime is

signal temp:integer range 0 to 5;

begin

process(clk)

begin

if (clr='1') then

daout<="0000";

sel<="000";

temp<=0;

elsif (clk='1'and clk'event) then

if temp=5 then temp<=0;

else temp<=temp + 1;

end if;

case temp is

when 0=>sel<="000";daout<=dain0;

when 1=>sel<="001";daout<=dain1;

when 2=>sel<="010";daout<=dain2;

when 3=>sel<="011";daout<=dain3;

when 4=>sel<="100";daout<=dain4;

when 5=>sel<="101";daout<=dain5;

end case;

end if;

end process;

end a;

(6)分频器(10MHz的时钟脉冲)

library ieee;

use ieee.std_logic_1164.all;

entity div is

port(clr,clk: in std_logic;

q: buffer std_logic);

end div;

architecture a of div issignal count:integer range 0 to 99999;

begin

process(clr,clk)

begin

if (clk'event and clk='1') then

if clr='1' then

count<=0;

elsif count=99999 then

count<=0;

q<= not q;

else

count<=count+1;

end if;

end if;

end process;

end ;

(7)元原件例化

library ieee;

use ieee.std_logic_1164.all;

entity mb_top is

port (

stop,start,clk:in std_logic;

a,b,c,d,e,f,g,speaker:out std_logic;

sel:out std_logic_vector(2 downto 0));

end mb_top;

architecture a of mb_top is

component div

port(clr,clk: in std_logic;

q: buffer std_logic);

end component;

component count10

port(

clr,start,clk:in std_logic;

cout:out std_logic;

daout:buffer std_logic_vector(3 downto 0));

end component;

component count6

port(

clr,start,clk:in std_logic;

cout:out std_logic;

daout:buffer std_logic_vector(3 downto 0));

end component;

component seltime

port(

clr,clk:in std_logic;

dain1:in std_logic_vector(3 downto 0);

dain2:in std_logic_vector(3 downto 0);

dain3:in std_logic_vector(3 downto 0);

dain4:in std_logic_vector(3 downto 0);

dain5:in std_logic_vector(3 downto 0);

dain6:in std_logic_vector(3 downto 0);

sel:out std_logic_vector(2 downto 0);

daout:out std_logic_vector(3 downto 0));

end component;

component deled

port(

num:in std_logic_vector(3 downto 0);

led:out std_logic_vector(6 downto 0));

end component;

component alarm

port(

clk,i:in std_logic;

q:out std_logic);

end component;

signal div_q,b_cout,s_cout,m_cout,sm_cout,f_cout,sf_cout:std_logic;

signal b_daout,s_daout,m_daout,sm_daout,f_daout,sf_daout,seltime_daout:std_logic_vector(3 downto 0);

signal ledout:std_logic_vector(6 downto 0);

begin

a<=ledout(0);b<=ledout(1);c<=ledout(2);d<=ledout(3);

e<=ledout(4);f<=ledout(5);g<=ledout(6);

u1:div port map(stop,clk,div_q);

u2:count10 port map(stop,start,div_q,b_cout,b_daout);

u3:count10 port map(stop,start,b_cout,s_cout,s_daout);

u4:count10 port map(stop,start,s_cout,m_cout,m_daout);

u5:count6 port map(stop,start,m_cout,sm_cout,sm_daout);

u6:count10 port map(stop,start,sm_cout,f_cout,f_daout);

u7:count6 port map(stop,start,f_cout,sf_cout,sf_daout);

u8:seltime port map(stop,div_q,b_daout,s_daout,m_daout,sm_daout,f_daout,sf_daout,sel,seltime_daout);

u9:deled port map(seltime_daout,ledout);

u10:alarm port map(div_q,sf_cout,speaker);

end a;

三.系统仿真

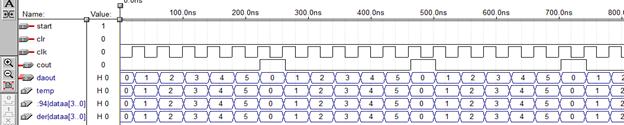

(1)六进制

(1)六进制

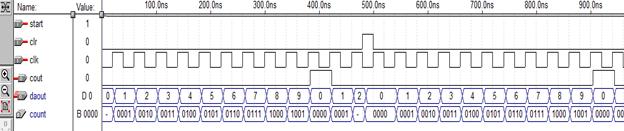

(2)十进制

(2)十进制

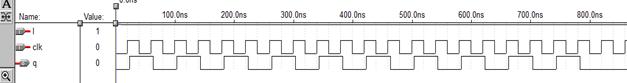

(3)蜂鸣器

(3)蜂鸣器

(4)译码器

(5)控制器

(5)控制器

四.心得体会

四.心得体会

开始做设计时总是会犯一些错误,只有经过不停的改错不停的编译才能得到正确的程序。在编程时,我充分使用了结构化的思想,这样程序检查起来也比较方便,调试时也给了我很大方便,只要一个模块一个模块的进行调就可以了,充分体现了结构化编程的优势。在设计中要求我要有耐心和毅力,还要细心,稍有不慎,一个小小的错误就会导致结果的不正确,而对错误的检查要求我要有足够的耐心,通过这次设计和设计中遇到的问题,也积累了一定的经验,对以后从事集成电路设计工作会有一定的帮助。

在应用VHDL的过程中让我真正领会到了其并行运行与其他软件顺序执行的差别及其在电路设计上的优越性。用VHDL硬件描述语言的形式来进行数字系统的设计方便灵活,利用EDA软件进行编译优化仿真极大地减少了电路设计时间和可能发生的错误,降低了开发成本,这种设计方法在数字系统设计中发挥越来越重要的作用。

五、参考文献

[1]李国洪、胡辉、沈明山.EDA技术与实验.机械工业出版社,2009

[2]闫石.数字电子技术基础(第五版).高等教育出版社,2006