实验报告

实验课程: 51单片机C语言教程

实验内容: 8孔流水灯

院 (系): 计算机学院

专 业: 通信工程

20##年10月29日

一、实验目的:

1、 熟练掌握AT89S52-Ⅰ型开发板的使用方法和注意事项。

2、 了解简单单片机应用系统的设计方法。

3、 掌握应用KEIL软件编辑、编译源汇编程序的操作方法。

4、 掌握应用USBISP烧录软件的操作方法。

5、 帮助学生养成良好实验习惯。

二、实验原理:

当STC89C51的P1口有低电平输出时,相应的发光二极管就会点亮。应用这一原理我们可以容易的点亮一个数码管,例如令P1口输出0111 1111时D1就会点亮。若再把0111 1111向右循环一位,利用P1口输出,就会点亮D2。在发光二极管两次点亮的间隔中加延时程序,让每次点亮停留一段时间,像这样人眼就可以看到“流水” 的现象。

1.单片机各引脚接口说明如表:

引脚分类

电源线2个、控制线6个、端口线4×8个总计40个引脚。

电源引脚:

VCC:接电源正极,给芯片通电,引脚号40。

GND:接电源负极,芯片地线,引脚号20。 控制引脚 :

9号引脚是单片机复位端(RST)

18、19号引脚是单片机的时钟端(XTAL2 XTAL1)

31号引脚是单片机片外程序存储器选择引脚(EA^)

30号引脚是地址锁存允许 (ALE)

29号引脚是片外ROM选通线 (PSEN^)

端口引脚 : P0,P1,P2,P3共32个

三、实验内容及步骤:

实验步骤:

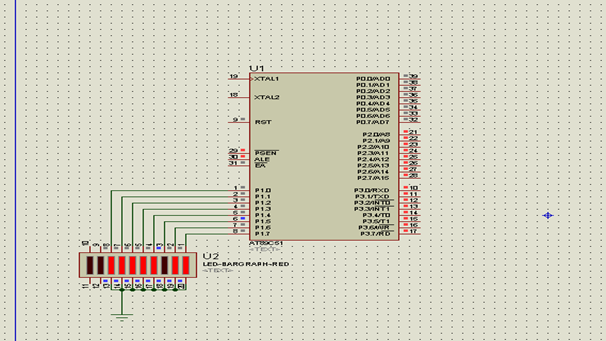

1. 用Proteus设计流水灯显示接口电路;

2. 在Keil C51中编写液晶显示控制语言C程序,编译通过后,与Proteus联合调试;

3. 在Proteus中仿真模拟。

实验电路图:

实验代码:

#include<reg52.h> //52单片机头文件

#include <intrins.h> //包含有左右循环移位子函数的库

#define uint unsigned int //宏定义

#define uchar unsigned char //宏定义

sbit P1_0=P1^0;

uchar tt,a;

void main() //主函数

{

TMOD=0x01;//设置定时器0为工作方式1

TH0=(65536-50000)/256;

TL0=(65536-50000)%256;

EA=1;//开总中断

ET0=1;//开定时器0中断

TR0=1;//启动定时器0

a=0xfe;

while(1);//等待中断产生

}

void timer0() interrupt 1

{

TH0=(65536-50000)/256;

TL0=(65536-50000)%256;

tt++;

if(tt==2)

{

tt=0;

P1=a;

a=_crol_(a,1);

}

}

四、实验总结与分析:

通过本次实验,了解了单片机IO口LED灯的电路结构,学会构建简单的流水灯电路。掌握C51单片机中IO口的进行输入输出的注意事项。

第二篇:eda流水灯实验报告

1. 实验目的

1.通过此实验让用户进一步了解、熟悉和掌握CPLD/FPGA开发软件的使用方法及VHDL的编程方法,熟悉以Herilong HDL文件为顶层模块的设计。

2.学习和体会分支条件语句casc的使用方法及FPGA I/O口的输出控制。

2. 实验内容

SmartSOPC实验箱上有8个按键KEY1~KEY8和8个发光二极管LED1~LED8。在SmartSOPC实验箱上KEY1~KEY8通过跳线JP6的LED1~LED8分别于芯片的121~124、143、141、158、和156引脚相连。

本实验的内容是要求在SmartSOPC实验箱上完成对8个键盘KEY1~KEY8进行监控,一旦有键输入判断其键值,并点亮相应的发光二极管,如若KEY3按下,则点亮LED1~LED3发光管并且在放开时也能保持亮的状态。

3. 实验原理

FPGA的所有I/O控制块允许每个I/O引脚单独置为输入口,不过这种配置是系统自动完成的,一旦该I/O口被设置为输入口使用时,该 I/O控制模块将直接使三态缓冲区的控制端接地,使得该 I/O引脚对外呈高阻态,这样改 I/O引脚即可用作专用输入引脚。只要正确分配并锁定引脚后,一旦在KEY1~KEY8中有键输入,在检测到键盘输入的情况下,继续判断其键盘值并作出相应的处理。

最后拿出跳线短接帽跳接到JP6的LED1~LED7、KEY1~KEY8使LED1~LED8和KEY1~KEY8和芯片对应的引脚相连。拿出Altera ByteBlasterⅡ下载电缆,并将此电缆的两端分别接到PC机的打印机并口和QuickSOPC核芯板上的JTAG下载口上,打开电源,执行下载命令,把程序下载到FPGA器件中,按下KEY1~KEY8的任意键,观察LED1~LED8的状态。

4. 实验步骤

1.启动QuartusⅡ建立一个空白工程,然后命名为keyboard 。

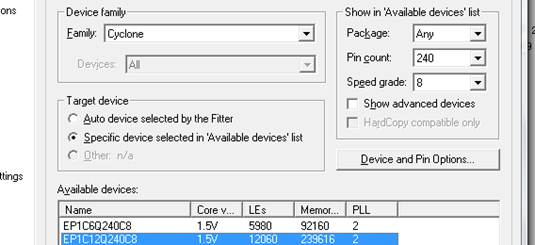

2.源程序文件命名为keyboard ,并选择器件为Altera公司Cyclone系列的EPIC12Q240C8芯片,如图1—1

图1—1

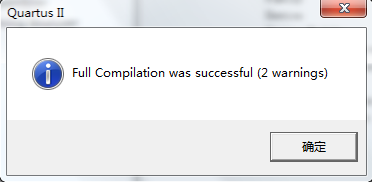

3.新建Veriog HDL源程序文件,输入程序代码并保存。再进行综合编译,若发现编译过程中有错误1—2(1),则找出并更正错误,直到编译成功为止。如图1—2(2)就表示编译成功了(warings可以不考虑)。

图1—2(1)

图1—2(2)

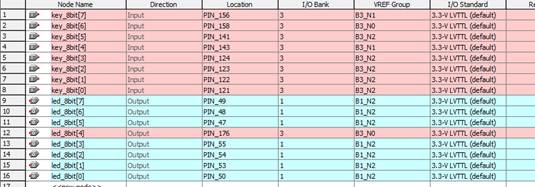

4.对引脚进行锁定。通过选择[Assignments]下的[pins]。分配好管脚如图1—3所示。

图1—3

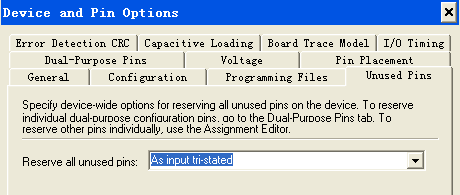

5.将未使用的管脚设置为三输入。以防止损坏芯片如图1—4所示。

图1—4

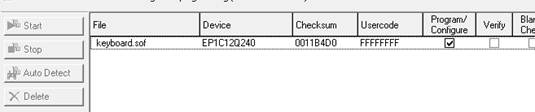

6. 最后拿出跳线短接帽跳接到JP6的LED1~LED7、KEY1~KEY8使LED1~LED8和KEY1~KEY8和芯片对应的引脚相连。拿出Altera ByteBlasterⅡ下载电缆,并将此电缆的两端分别接到PC机的打印机并口和QuickSOPC核芯板上的JTAG下载口上,打开电源,执行下载命令,把程序下载到FPGA器件中(如图1-5),按下KEY1~KEY8的任意键,观察LED1~LED8的状态。

图1—5在点[Start]即可下载烧录了。

5. 实验程序

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

use IEEE.STD_LOGIC_UNSIGNED.ALL;

entity keyboard is

port(key_8bit:IN std_logic_vector(7 downto 0);

led_8bit:OUT std_logic_vector(7 downto 0));

end keyboard;

architecture keyboard of keyboard is

signal tmp: std_logic_vector(7 downto 0);

begin

process(key_8bit)

begin

case key_8bit is

when "11111110"=>tmp<="11111110";

when "11111101"=>tmp<="11111101";

when "11111011"=>tmp<="11111011";

when "11110111"=>tmp<="11110111";

when "11101111"=>tmp<="11101111";

when "11011111"=>tmp<="11011111";

when "10111111"=>tmp<="10111111";

when "01111111"=>tmp<="01111111";

when others=>tmp<="ZZZZZZZZ";

end case;

end process;

led_8bit<=tmp;

end keyboard;

6. 实验结果

展示依次按下单个按键的效果

7.总结与思考

(详见手写附页)