电子设计自动化实验报告 学号: 姓名:

实验(一)

1. 实验名称:

7段数码显示译码器

2. 实验目的:

学习7段数码显示译码器的Verilog硬件设计。

3. 实验原理:

7段数码是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能作十进制BCD码译码,然而数字系统中的数据处理和运算都是二进制的,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。例如6-18作为7段译码器,输出信号LED7S的7位分别接图6-17数码管的7个段,高位在左,低位在右。例如当LED7S输出为“1101101”时,数码管的7个段g,f,e,d,c,b,a分别接1,1,0,1,1,0,1;接有高电平的段发亮,于是数码管显示“5”。这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h,然后将LED7S改为8位输出。

4. 实验内容:

1、 编辑和输入设计文件

新建文件夹——输入源程序——文件存盘

源程序:

module LED(A,LED7S);

input [3:0]A;

output [6:0]LED7S;

reg [6:0]LED7S;

1

电子设计自动化实验报告 学号: 姓名:

always @ (A)

begin: LED

case(A)

4'b0000: LED7S<=7'b0111111;

4'b0001: LED7S<=7'b0000110;

4'b0010: LED7S<=7'b1011011;

4'b0011: LED7S<=7'b1001111;

4'b0100: LED7S<=7'b1100110;

4'b0101: LED7S<=7'b1101101;

4'b0110: LED7S<=7'b1111101;

4'b0111: LED7S<=7'b0000111;

4'b1000: LED7S<=7'b1111111;

4'b1001: LED7S<=7'b1101111;

4'b1010: LED7S<=7'b1110111;

4'b1011: LED7S<=7'b1111100;

4'b1100: LED7S<=7'b0111001;

4'b1101: LED7S<=7'b1011110;

4'b1110: LED7S<=7'b1111001;

4'b1111: LED7S<=7'b1110001;

default: LED7S<=7'b0111111;

endcase

end

endmodule

2、 创建工程

打开并建立新工程管理窗口——将设计文件加入工程中——选择目标芯片——工具设置——结束设置

3、 全程编译前约束项目设置

选择FPGA目标芯片——选择配置器件的工作方式——选择配置器件和编程方式——选择目标器件引脚端口状态——选择Verilog语言版本

4、 全程综合与编译

Processing——Start Compilation启动全程编译

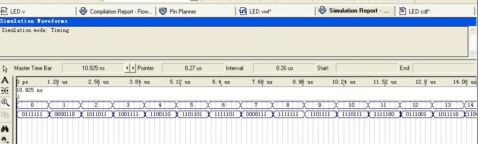

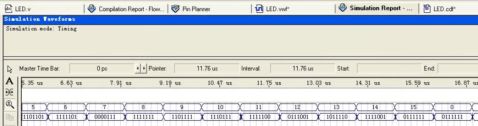

5、 仿真测试

时序分析

:

延时分析及结果:

2

电子设计自动化实验报告 学号: 姓名:

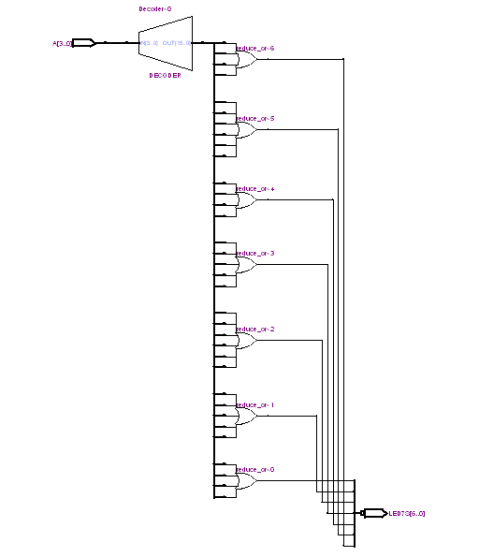

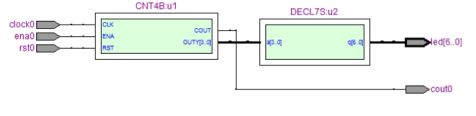

生成 RTL原理图:

3

电子设计自动化实验报告 学号: 姓名:

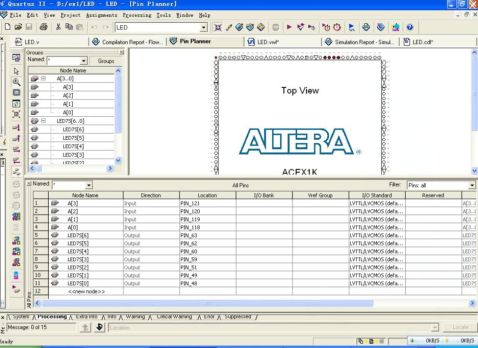

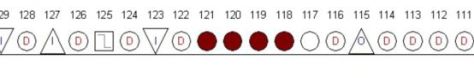

该实验的配置模式:

4

电子设计自动化实验报告 学号: 姓名:

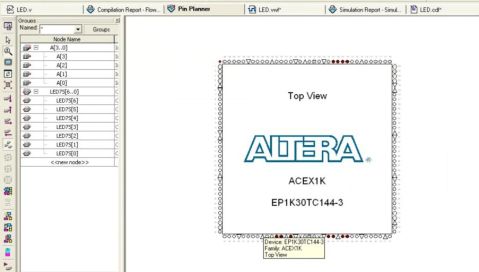

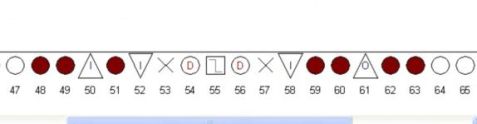

适配板布局图及实验仪IO脚与芯片的管脚对应关系和其详细放大图片:

5

电子设计自动化实验报告 学号: 姓名:

6

电子设计自动化实验报告 学号: 姓名:

逻辑分析:

计数器和译码器连接电路的顶层文件原理图:

6. 总结与体会

通过本次实验,我对Quartus II有了进一步的学习和认识,对Verilog也有了深入了解。学会了7段数码显示译码器的Verilog硬件设计,学习了VHDL的CASE语句应用。认识到做实验应该提前弄清实验原理,做实验时耐心、认真,遇到问题争取努力解决。并且在实验后应认真总结实验,分析波形,完成实验报告。这门课程锻炼了我读程序的能力和分析语法用法的能力,为我将来学更高级的语言打下了基础。但我开始学会运用Quartus II 这个软件,并靠自己慢慢去摸索,慢慢研究和老师的教导以及同学们的相互帮助,我相信我能学好这门课程的。 7

第二篇:实验1 7段数码显示译码器设计

实验二 7段数码显示译码器设计

一、 实验目的

学习7段数码显示译码器设计;学习VHDL的CASE语句应用及多层次设计。

二、 实验内容

说明例3-1中各语句的含义,以及该例的整体功能。在QuartusⅡ上对该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序波形。

硬件设置:选实验电路模式6,用数码8显示译码输出(PIO46~40, 引脚号为105、103、99~96、85),键8(PIO13, 引脚号为36)、键7(PIO12, 引脚号为

35)、键6(PIO11, 引脚号为34)、键5(PIO10, 引脚号为33)四位控制输入。最后进行编译、下载和硬件测试实验。

三、 实验报告

根据实验内容,写出实验报告,包括编译仿真波形、分析结果以及硬件测试实验结果。

四、 实验步骤

将实验一中的源程序输入部分改为7段数码显示译码器程序输入即可。

实验二 7段数码显示译码器设计 LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY DECL7S IS

PORT ( A : IN STD_LOGIC_VECTOR(3 DOWNTO 0); LED7S : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) ) ; END DECL7S;

ARCHITECTURE one OF DECL7S IS

BEGIN

PROCESS( A )

BEGIN

CASE A IS

WHEN "0000" => LED7S <= "0111111" ; WHEN "0001" => LED7S <= "0000110" ; WHEN "0010" => LED7S <= "1011011" ; WHEN "0011" => LED7S <= "1001111" ; WHEN "0100" => LED7S <= "1100110" ; WHEN "0101" => LED7S <= "1101101" ; WHEN "0110" => LED7S <= "1111101" ; WHEN "0111" => LED7S <= "0000111" ; WHEN "1000" => LED7S <= "1111111" ; WHEN "1001" => LED7S <= "1101111" ; WHEN "1010" => LED7S <= "1110111" ; WHEN "1011" => LED7S <= "1111100" ; WHEN "1100" => LED7S <= "0111001" ; WHEN "1101" => LED7S <= "1011110" ; WHEN "1110" => LED7S <= "1111001" ; WHEN "1111" => LED7S <= "1110001" ; WHEN OTHERS => NULL ;

END CASE ;

END PROCESS ;

END ;

实验三 计数器设计

四、 实验目的

学习含异步清零、同步时钟使能功能的计数器设计。

五、 实验内容

说明程序中各语句的含义,以及该例的整体功能。在QuartusⅡ上对该例进行编辑、编译、综合、适配、仿真,给出其所有信号的时序波形。

硬件设置:选实验电路模式5,用数码管1显示计数器输出(PIO19~16, 引脚号为42、41、40、39),使能端为键1(PIO0, 引脚号为1),清零端为键2(PIO1, 引脚号为2),进位端为发光二极管1(PIO8, 引脚号为11),时钟端(clock0, 引脚号为93)。最后进行编译、下载和硬件测试实验。

六、 实验报告

根据实验内容,写出实验报告,包括编译仿真波形、分析结果以及硬件测试实验结果。

四、 实验步骤

输入编写的源程序,编译通过后,进行仿真分析。仿真完成后进行管脚定义并编译通过,实验箱时钟clock5加短路帽,clock0接4HZ。烧写程序,实现硬件测试。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY cnt10a IS --主程序

PORT(CLK,RST,ENA:IN STD_LOGIC; --时钟信号端、清零端、使能端 COUNT:OUT STD_LOGIC_VECTOR(3 DOWNTO 0); --四位输出 OUTY:OUT STD_LOGIC); --进位端

END cnt10a;

ARCHITECTURE beha OF cnt10a IS

SIGNAL c1: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(CLK,RST,ENA)

BEGIN

IF(RST='1')THEN c1<="0000"; --复位端有效时,立刻输出清零 ELSIF(CLK'EVENT AND CLK='1')THEN

IF ENA='1'THEN c1<=c1+1; --同步使能端有效时,计数1次 IF(c1>="1001")THEN c1<="0000"; --十进制计数器,计满循环 END IF;

END IF;

END IF;

END PROCESS;

PROCESS(CLK)

BEGIN

IF CLK'EVENT AND CLK='1'THEN

IF c1="1001"THEN OUTY<='1'; --计数器计满进位判断

ELSE OUTY<='0';

END IF;

END IF;

COUNT<=c1; --进位输出标志

END PROCESS;

END beha;